隨著半導(dǎo)體技術(shù)的飛速發(fā)展,芯片集成度不斷提高,功能日益復(fù)雜,這對(duì)半導(dǎo)體貼裝工藝和設(shè)備提出了更高的要求。半導(dǎo)體貼裝工藝作為半導(dǎo)體封裝過程中的關(guān)鍵環(huán)節(jié),直接關(guān)系到芯片的性能、可靠性和成本。本文將深入分析半導(dǎo)體貼裝工藝及其相關(guān)設(shè)備,探討其發(fā)展趨勢(shì)和挑戰(zhàn)。

一、半導(dǎo)體貼裝工藝概述

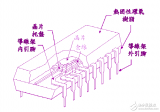

半導(dǎo)體貼裝工藝是將芯片通過有機(jī)膠、金屬焊料或其他連接方式精確地粘貼在基板或引線框架上的過程。這一工藝步驟在半導(dǎo)體封裝流程中占據(jù)重要地位,它實(shí)現(xiàn)了芯片與外部電路的電氣連接、機(jī)械連接和熱連接,確保了芯片的穩(wěn)定性和可靠性。

半導(dǎo)體貼裝工藝的主要目的是將切割后的裸芯片(晶粒)粘貼到基板上,形成芯片組件。這一過程中,需要確保芯片與基板之間的電氣連接良好,同時(shí)提供足夠的機(jī)械支撐和熱散失能力。為了實(shí)現(xiàn)這一目標(biāo),貼裝工藝需要高精度的定位、穩(wěn)定的貼裝壓力和可靠的連接方式。

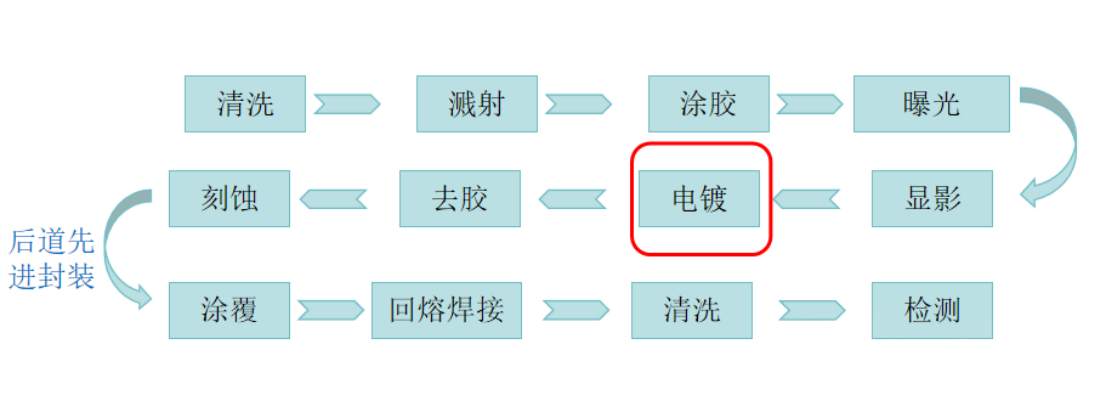

二、半導(dǎo)體貼裝工藝步驟

半導(dǎo)體貼裝工藝通常包括以下幾個(gè)關(guān)鍵步驟:

- 基板準(zhǔn)備:在貼裝芯片之前,需要對(duì)基板進(jìn)行清洗、涂膠等預(yù)處理工作。清洗基板可以去除表面的污垢和氧化物,提高貼裝質(zhì)量;涂膠則是為了增強(qiáng)芯片與基板之間的粘接力,防止芯片在使用過程中脫落。

- 芯片定位:使用高精度的貼裝設(shè)備將芯片準(zhǔn)確地放置在基板上的預(yù)定位置。這一過程需要高精度的定位系統(tǒng)和穩(wěn)定的機(jī)械結(jié)構(gòu),以確保芯片的位置精度和貼裝壓力均勻性。

- 芯片粘貼:將芯片粘貼到基板上的過程可以通過多種方式實(shí)現(xiàn),如銀膠粘貼、共晶粘貼、高分子膠粘貼等。不同的粘貼方式適用于不同的應(yīng)用場(chǎng)景和需求。

- 固化處理:粘貼完成后,需要對(duì)芯片進(jìn)行固化處理,以提高芯片與基板之間的粘接力。固化處理可以通過加熱、紫外線照射等方式實(shí)現(xiàn),具體方法取決于所使用的粘貼材料。

- 質(zhì)量檢測(cè):最后,需要對(duì)貼裝完成的芯片組件進(jìn)行質(zhì)量檢測(cè),包括外觀檢查、電氣性能測(cè)試等。這可以確保芯片組件的質(zhì)量符合設(shè)計(jì)要求,提高產(chǎn)品的可靠性和穩(wěn)定性。

三、半導(dǎo)體貼裝設(shè)備分析

半導(dǎo)體貼裝設(shè)備是實(shí)現(xiàn)半導(dǎo)體貼裝工藝的關(guān)鍵工具。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,貼裝設(shè)備也在不斷更新?lián)Q代,以滿足日益提高的貼裝精度和效率要求。

- 貼裝設(shè)備類型

半導(dǎo)體貼裝設(shè)備主要分為手動(dòng)貼裝設(shè)備和自動(dòng)貼裝設(shè)備兩大類。手動(dòng)貼裝設(shè)備適用于小批量、多品種的生產(chǎn)需求,具有靈活性高、成本低等優(yōu)點(diǎn);但貼裝精度和效率相對(duì)較低。自動(dòng)貼裝設(shè)備則適用于大批量、單一品種的生產(chǎn)需求,具有貼裝精度高、效率高、穩(wěn)定性好等優(yōu)點(diǎn);但設(shè)備成本較高,需要專業(yè)的操作和維護(hù)人員。

在自動(dòng)貼裝設(shè)備中,又可以根據(jù)貼裝方式的不同分為引腳插入式貼裝設(shè)備、表面貼裝設(shè)備(SMT)和倒裝芯片貼裝設(shè)備(FC)等。引腳插入式貼裝設(shè)備適用于引腳數(shù)量較少的芯片貼裝;表面貼裝設(shè)備則適用于引腳數(shù)量較多、體積較小的芯片貼裝;倒裝芯片貼裝設(shè)備則適用于高端芯片貼裝,如CPU、GPU等。

- 貼裝設(shè)備關(guān)鍵技術(shù)

半導(dǎo)體貼裝設(shè)備的關(guān)鍵技術(shù)包括高精度定位系統(tǒng)、穩(wěn)定的機(jī)械結(jié)構(gòu)、可靠的連接方式、智能控制系統(tǒng)等。

高精度定位系統(tǒng)是實(shí)現(xiàn)芯片精確定位的關(guān)鍵。現(xiàn)代貼裝設(shè)備通常采用光學(xué)或激光定位系統(tǒng),通過攝像頭捕捉芯片和基板的圖像,并通過算法計(jì)算出芯片在基板上的精確位置。同時(shí),設(shè)備還需要具備高速、高精度的運(yùn)動(dòng)控制系統(tǒng),以確保芯片在移動(dòng)過程中的穩(wěn)定性和準(zhǔn)確性。

穩(wěn)定的機(jī)械結(jié)構(gòu)是確保貼裝設(shè)備長(zhǎng)期穩(wěn)定運(yùn)行的基礎(chǔ)。貼裝設(shè)備需要承受高速、高頻次的運(yùn)動(dòng)沖擊和振動(dòng),因此機(jī)械結(jié)構(gòu)需要具備足夠的剛性和穩(wěn)定性。此外,設(shè)備還需要具備良好的散熱性能,以防止因過熱而導(dǎo)致的設(shè)備故障。

可靠的連接方式是確保芯片與基板之間電氣連接良好的關(guān)鍵。不同的芯片和基板材料需要采用不同的連接方式,如銀膠粘貼、共晶粘貼、高分子膠粘貼等。貼裝設(shè)備需要具備多種連接方式的選擇和切換能力,以滿足不同應(yīng)用場(chǎng)景的需求。

智能控制系統(tǒng)是實(shí)現(xiàn)貼裝設(shè)備自動(dòng)化、智能化的關(guān)鍵。現(xiàn)代貼裝設(shè)備通常采用先進(jìn)的控制算法和人工智能技術(shù),實(shí)現(xiàn)設(shè)備的自動(dòng)化控制和智能決策。例如,設(shè)備可以根據(jù)芯片和基板的不同特性自動(dòng)調(diào)整貼裝參數(shù)和工藝流程;同時(shí),還可以實(shí)時(shí)監(jiān)測(cè)設(shè)備的運(yùn)行狀態(tài)和貼裝質(zhì)量,及時(shí)發(fā)現(xiàn)并處理異常情況。

- 貼裝設(shè)備發(fā)展趨勢(shì)

隨著半導(dǎo)體技術(shù)的不斷發(fā)展,貼裝設(shè)備也在不斷更新?lián)Q代。未來,貼裝設(shè)備將朝著高精度、高效率、智能化、柔性化等方向發(fā)展。

高精度是貼裝設(shè)備永恒的追求。隨著芯片集成度的不斷提高和尺寸的不斷縮小,對(duì)貼裝精度的要求也越來越高。未來,貼裝設(shè)備將采用更先進(jìn)的定位系統(tǒng)和運(yùn)動(dòng)控制系統(tǒng),實(shí)現(xiàn)更高的貼裝精度和穩(wěn)定性。

高效率是貼裝設(shè)備發(fā)展的重要趨勢(shì)。隨著市場(chǎng)競(jìng)爭(zhēng)的加劇和生產(chǎn)成本的不斷上升,提高貼裝效率成為降低生產(chǎn)成本、提高競(jìng)爭(zhēng)力的關(guān)鍵。未來,貼裝設(shè)備將采用更先進(jìn)的生產(chǎn)流程和技術(shù)手段,實(shí)現(xiàn)更高的生產(chǎn)效率和產(chǎn)能。

智能化是貼裝設(shè)備發(fā)展的重要方向。隨著人工智能技術(shù)的不斷發(fā)展和應(yīng)用,貼裝設(shè)備將具備更強(qiáng)的智能控制和決策能力。例如,設(shè)備可以根據(jù)生產(chǎn)需求自動(dòng)調(diào)整工藝流程和參數(shù)設(shè)置;同時(shí),還可以實(shí)時(shí)監(jiān)測(cè)設(shè)備的運(yùn)行狀態(tài)和貼裝質(zhì)量,及時(shí)發(fā)現(xiàn)并處理異常情況。

柔性化是貼裝設(shè)備適應(yīng)多品種、小批量生產(chǎn)需求的關(guān)鍵。未來,貼裝設(shè)備將具備更強(qiáng)的柔性化生產(chǎn)能力,可以根據(jù)不同的生產(chǎn)需求快速切換工藝流程和參數(shù)設(shè)置。這將有助于降低生產(chǎn)成本、提高生產(chǎn)效率和靈活性。

四、半導(dǎo)體貼裝工藝與設(shè)備的挑戰(zhàn)與解決方案

盡管半導(dǎo)體貼裝工藝和設(shè)備取得了顯著的進(jìn)展和成就,但仍面臨一些挑戰(zhàn)和問題。以下是一些主要的挑戰(zhàn)及其解決方案:

- 挑戰(zhàn)一:貼裝精度要求高

隨著芯片集成度的不斷提高和尺寸的不斷縮小,對(duì)貼裝精度的要求也越來越高。微小的偏差都可能導(dǎo)致芯片與基板之間的電氣連接不良或機(jī)械支撐不足等問題。

解決方案:采用更先進(jìn)的定位系統(tǒng)和運(yùn)動(dòng)控制系統(tǒng),提高貼裝精度和穩(wěn)定性。同時(shí),加強(qiáng)對(duì)設(shè)備的維護(hù)和保養(yǎng)工作,確保設(shè)備的長(zhǎng)期穩(wěn)定運(yùn)行。

- 挑戰(zhàn)二:貼裝材料選擇困難

不同的芯片和基板材料需要采用不同的連接方式,如銀膠粘貼、共晶粘貼、高分子膠粘貼等。不同的連接方式具有不同的優(yōu)缺點(diǎn)和適用范圍,選擇不當(dāng)可能導(dǎo)致貼裝質(zhì)量下降或成本上升等問題。

解決方案:根據(jù)芯片和基板的不同特性選擇合適的連接方式。同時(shí),加強(qiáng)對(duì)新材料和新工藝的研究和開發(fā)工作,以提供更多選擇和可能性。

- 挑戰(zhàn)三:生產(chǎn)成本高

半導(dǎo)體貼裝設(shè)備和工藝的成本相對(duì)較高,這對(duì)企業(yè)的生產(chǎn)成本和競(jìng)爭(zhēng)力產(chǎn)生了一定影響。同時(shí),隨著市場(chǎng)競(jìng)爭(zhēng)的加劇和生產(chǎn)成本的不斷上升,降低生產(chǎn)成本成為提高企業(yè)競(jìng)爭(zhēng)力的關(guān)鍵。

解決方案:通過技術(shù)創(chuàng)新和工藝優(yōu)化降低生產(chǎn)成本。例如,采用更先進(jìn)的生產(chǎn)流程和技術(shù)手段提高生產(chǎn)效率;同時(shí),加強(qiáng)設(shè)備的維護(hù)和保養(yǎng)工作延長(zhǎng)設(shè)備使用壽命降低維修成本等。

- 挑戰(zhàn)四:環(huán)境要求嚴(yán)格

半導(dǎo)體貼裝工藝和設(shè)備對(duì)生產(chǎn)環(huán)境的要求非常嚴(yán)格,如溫度、濕度、潔凈度等都需要控制在一定范圍內(nèi)。否則可能導(dǎo)致芯片受潮、氧化或污染等問題影響貼裝質(zhì)量和可靠性。

解決方案:加強(qiáng)對(duì)生產(chǎn)環(huán)境的控制和管理工作。例如,采用先進(jìn)的溫濕度控制系統(tǒng)和潔凈室技術(shù)確保生產(chǎn)環(huán)境的穩(wěn)定性和可靠性;同時(shí)加強(qiáng)對(duì)員工的培訓(xùn)和管理提高員工的環(huán)境意識(shí)和操作技能等。

五、結(jié)論

半導(dǎo)體貼裝工藝與設(shè)備是半導(dǎo)體封裝過程中的關(guān)鍵環(huán)節(jié)之一,對(duì)芯片的性能、可靠性和成本具有重要影響。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,貼裝工藝和設(shè)備也在不斷更新?lián)Q代以滿足日益提高的貼裝精度和效率要求。然而,在發(fā)展過程中仍面臨一些挑戰(zhàn)和問題如貼裝精度要求高、貼裝材料選擇困難、生產(chǎn)成本高以及環(huán)境要求嚴(yán)格等。通過技術(shù)創(chuàng)新和工藝優(yōu)化等措施可以有效解決這些問題推動(dòng)半導(dǎo)體貼裝工藝與設(shè)備的進(jìn)一步發(fā)展。

未來,隨著人工智能、物聯(lián)網(wǎng)等新興技術(shù)的快速發(fā)展和應(yīng)用場(chǎng)景的不斷拓展半導(dǎo)體貼裝工藝與設(shè)備將迎來更廣闊的發(fā)展前景和機(jī)遇。企業(yè)需要密切關(guān)注市場(chǎng)動(dòng)態(tài)和技術(shù)發(fā)展趨勢(shì)加強(qiáng)技術(shù)創(chuàng)新和研發(fā)投入提高產(chǎn)品質(zhì)量和競(jìng)爭(zhēng)力以應(yīng)對(duì)日益激烈的市場(chǎng)競(jìng)爭(zhēng)和挑戰(zhàn)。同時(shí),政府和社會(huì)各界也應(yīng)加強(qiáng)對(duì)半導(dǎo)體產(chǎn)業(yè)的支持和引導(dǎo)推動(dòng)半導(dǎo)體產(chǎn)業(yè)的持續(xù)健康發(fā)展。

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465896 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30725瀏覽量

264005 -

貼裝

+關(guān)注

關(guān)注

0文章

95瀏覽量

17380

發(fā)布評(píng)論請(qǐng)先 登錄

有關(guān)半導(dǎo)體工藝的問題

半導(dǎo)體工藝講座

招聘半導(dǎo)體封裝工程師

半導(dǎo)體生產(chǎn)封裝工藝簡(jiǎn)介

半導(dǎo)體封裝工藝之模塑工藝類型

聊聊半導(dǎo)體產(chǎn)品的8大封裝工藝

半導(dǎo)體封裝工藝的研究分析

半導(dǎo)體封裝工藝面臨的挑戰(zhàn)

閑談半導(dǎo)體封裝工藝工程師

半導(dǎo)體溫控新突破:精度與效率的雙重提升

揭秘半導(dǎo)體電鍍工藝

半導(dǎo)體貼裝工藝大揭秘:精度與效率的雙重飛躍

半導(dǎo)體貼裝工藝大揭秘:精度與效率的雙重飛躍

評(píng)論