封裝工藝正從傳統(tǒng)保護(hù)功能向系統(tǒng)級(jí)集成演進(jìn),其核心在于平衡電氣性能、散熱效率與制造成本?。

一、封裝工藝的基本概念

芯片封裝是將半導(dǎo)體芯片通過特定工藝封裝于保護(hù)性外殼中的技術(shù),主要功能包括:

物理保護(hù)?:防止芯片受機(jī)械損傷、濕氣、灰塵等外界環(huán)境影響?;

電氣連接?:通過引腳或焊料凸點(diǎn)實(shí)現(xiàn)芯片與外部電路的穩(wěn)定信號(hào)傳輸?;

散熱管理?:優(yōu)化封裝材料與結(jié)構(gòu)設(shè)計(jì),提升芯片散熱效率?;

機(jī)械支撐?:增強(qiáng)芯片結(jié)構(gòu)強(qiáng)度以應(yīng)對(duì)振動(dòng)、沖擊等物理應(yīng)力?。

二、封裝工藝的主要分類

【傳統(tǒng)封裝技術(shù)】?

通孔插裝技術(shù)(1980年前)?:以DIP(雙列直插封裝)為代表,引腳數(shù)≤64,安裝密度約10引腳/cm2?;

表面貼裝技術(shù)(1980-1990年)?:采用SOP(小外形封裝)和QFP(四邊引腳扁平封裝),引腳數(shù)擴(kuò)展至3-300條,安裝密度達(dá)10-50引腳/cm2?。

?【先進(jìn)封裝技術(shù)】

系統(tǒng)級(jí)封裝(SiP)?:集成處理器、存儲(chǔ)器等多功能芯片于單一封裝內(nèi),支持2D、堆疊及3D結(jié)構(gòu),顯著縮短開發(fā)周期并降低成本?;

倒裝封裝(Flip Chip)?:芯片倒置并通過焊球直接連接基板,縮短信號(hào)傳輸路徑,提升I/O密度與高頻性能?;

多芯片封裝(MCP)?:基于2.5D/3D堆疊技術(shù),采用硅中介層或有機(jī)基板實(shí)現(xiàn)高密度互連,適用于移動(dòng)設(shè)備與高算力服務(wù)器?。

三、封裝工藝流程

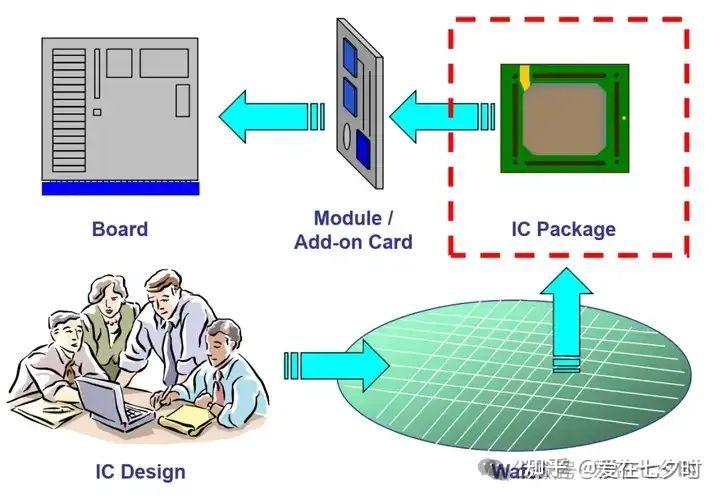

封裝等級(jí)劃分?

0級(jí)封裝?:晶圓切割為獨(dú)立芯片?;

1級(jí)封裝?:芯片級(jí)封裝(如倒裝焊、引線鍵合)?;

2級(jí)封裝?:封裝芯片安裝至模塊或電路卡?;

3級(jí)封裝?:系統(tǒng)級(jí)集成,完成電路卡到主板的安裝?。

關(guān)鍵制造步驟?

凸點(diǎn)制作?:在芯片I/O焊盤沉積金屬凸點(diǎn),結(jié)合UBM層增強(qiáng)導(dǎo)電性與附著力?;

芯片貼裝?:高精度對(duì)準(zhǔn)基板焊盤,通過加熱或加壓實(shí)現(xiàn)焊球連接?;

底部填充?:注入環(huán)氧樹脂材料固化,吸收熱應(yīng)力并提升機(jī)械穩(wěn)定性?;

塑封成型?:采用環(huán)氧模塑料包裹芯片,形成最終保護(hù)殼體?。

四、技術(shù)發(fā)展趨勢(shì)

高密度集成?:3D堆疊與Chiplet技術(shù)突破物理限制,實(shí)現(xiàn)超薄、異構(gòu)芯片集成?;

智能散熱方案?:集成熱界面材料(TIM)與液冷技術(shù),應(yīng)對(duì)200-400W高功耗場(chǎng)景?;

國產(chǎn)化突破?:國產(chǎn)封裝設(shè)備逐步替代進(jìn)口,兼容信創(chuàng)生態(tài)與邊緣計(jì)算需求?。

審核編輯 黃宇

-

芯片封裝

+關(guān)注

關(guān)注

13文章

614瀏覽量

32261

發(fā)布評(píng)論請(qǐng)先 登錄

短距離光模塊 COB 封裝與同軸工藝的區(qū)別有哪些

熱壓鍵合工藝的技術(shù)原理和流程詳解

SK海力士HBS存儲(chǔ)技術(shù),基于垂直導(dǎo)線扇出VFO封裝工藝

半導(dǎo)體“封裝過程”工藝技術(shù)的詳解;

芯片鍵合工藝技術(shù)介紹

詳解芯片封裝的工藝步驟

傳統(tǒng)封裝與晶圓級(jí)封裝的區(qū)別

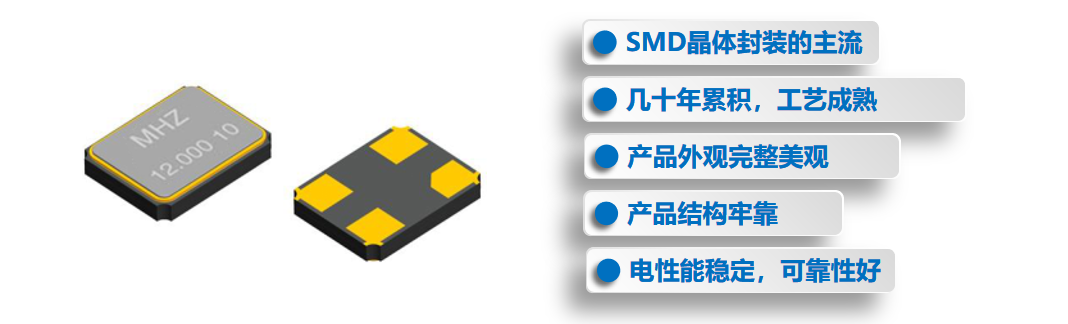

晶振常見封裝工藝及其特點(diǎn)

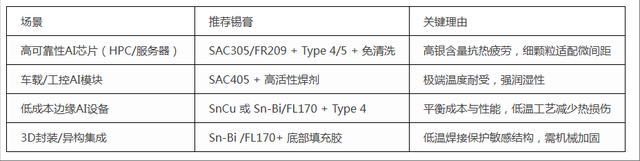

AI芯片封裝,選擇什么錫膏比較好?

先進(jìn)封裝工藝面臨的挑戰(zhàn)

全面剖析倒裝芯片封裝技術(shù)的內(nèi)在機(jī)制、特性優(yōu)勢(shì)、面臨的挑戰(zhàn)及未來走向

半導(dǎo)體貼裝工藝大揭秘:精度與效率的雙重飛躍

芯片封裝工藝詳解

芯片封裝工藝詳解

評(píng)論