【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

半導體的典型封裝工藝流程包括芯片減薄、芯片切割、芯片貼裝、芯片互連、成型固化、去飛邊毛刺、切筋成型、上焊錫、打碼、外觀檢查、成品測試和包裝出庫,涵蓋了前段(FOL)、中段(EOL)、電鍍(plating)、后段(EOL)以及終測(final test)等多個關鍵環節。

而我們常說的半導體封裝就是將通過測試的晶圓按照產品型號及功能需求加工得到獨立芯片的這一過程。在這個封裝過程中,首先是來自晶圓前道工藝的晶圓通過劃片工藝后被切割為小的晶片(Die),然后將切割好的晶片用膠水貼裝到相應的基板(引線框架)架的小島上,再利用超細的金屬(金錫銅鋁)導線或者導電性樹脂將晶片的接合焊盤(Bond Pad)連接到基板的相應引腳(Lead),并構成所要求的電路;然后再對獨立的晶片用塑料外殼加以封裝保護,塑封之后還要進行一系列操作,封裝完成后進行成品測試,通常經過入檢Incoming、測試Test和包裝Packing等工序,最后入庫出貨。

接下來,我要跟大家分享的就是半導體封裝工藝的過程。本人特意用了大量圖片和現場工程經驗來分享,希望大家能深刻領會到半導體封裝工藝的魅力。

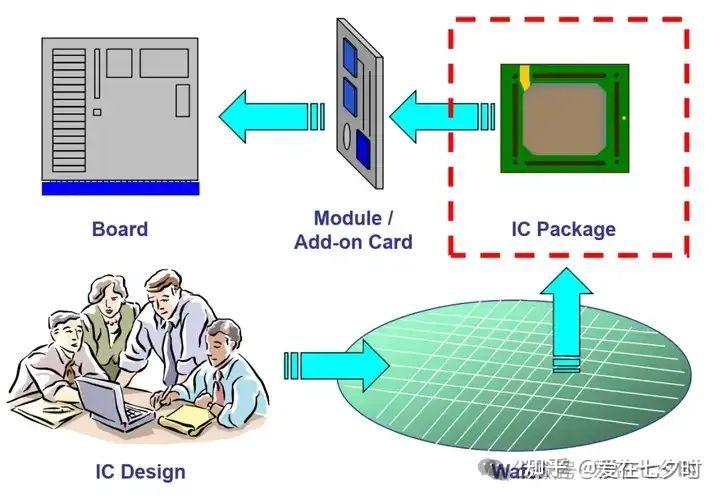

一、半導體產業鏈情況

半導體鏈中的集成電路封裝

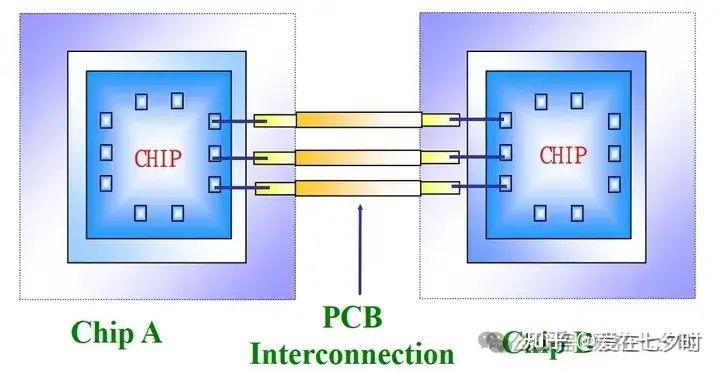

二、半導體封裝的層級

電子包裝體系—包裝層次結構

三、集成電路封裝(IC Packaging)的目的

1、Mechanic Protection for Chip 保護晶片

2、Power & Singal Transportation 與外腳連接

3、Heat Dissipation 提供散熱

4、Assist Testing and Mounting 方便測試與上板

四、半導體封裝的功能與目的

1、提供電氣傳導路徑(包括金線、引線框架及銅導線),讓微細的集成電路彼此做連結

2、保護IC晶片不受外力的破壞

3、避免濕氣滲透到IC內部

4、提供IC晶片散熱路徑

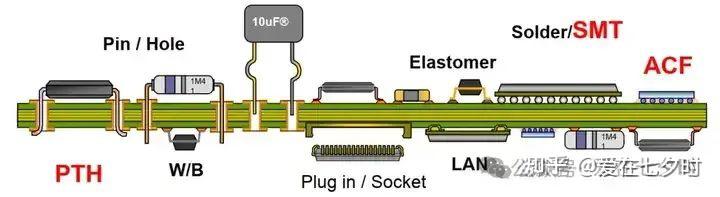

五、集成電路封裝的分類

1、IC構裝種類依其上板方式之差異,則可區分為:

(1) PTH (Pin Through Hole) 封裝

(2)SMT ( Surface Mount Technology)封裝

2、若以外連接腳之幾何外觀作分類則有,直立腳、海鷗腳、J-Lead、球型腳與Leadless等五種。

3、單就IC外面之封裝材料而言, 又可分為陶瓷、 塑膠兩類主要封裝方式。

六、集成電路(IC)封裝的分類

SMT (Surface Mount Technology)

PTH (Pin Through Hole)

IC元件上板模式

七、集成電路封裝的發展趨勢

1、ASE Package Trajectory

2、Lead Frame Package

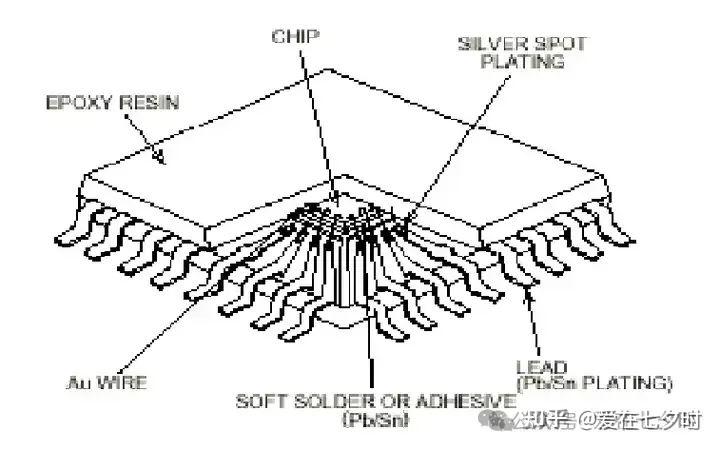

Lead frame package 是以金屬(導線架)為基板,并將晶片黏于導線架上進而進行引線鍵合,封膠及成型所完成的半導體封 裝 體 稱 為 Lead frame package。

3、P‐DIP封裝

4、QFP Package

5、SOP vs QFP

四方扁平封裝IC

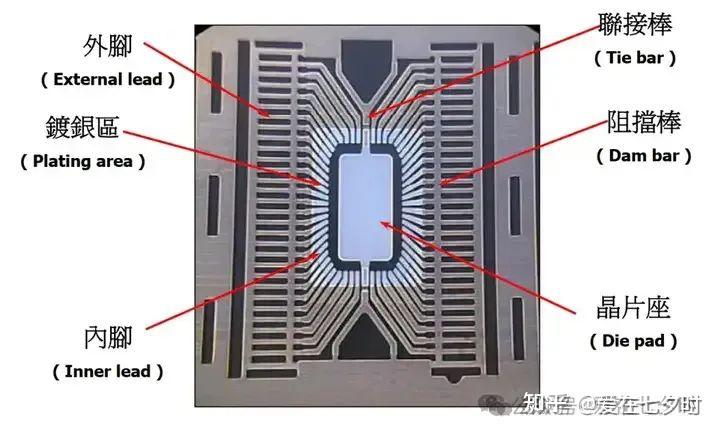

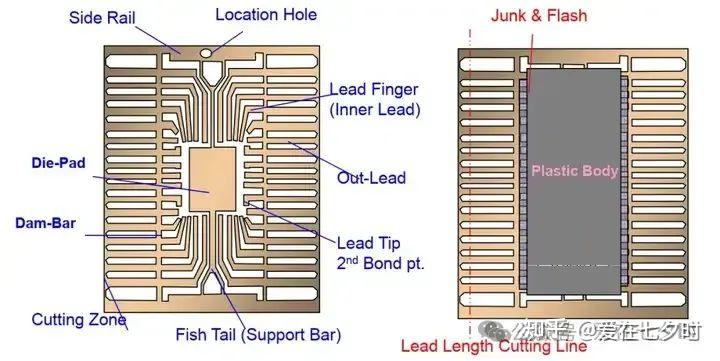

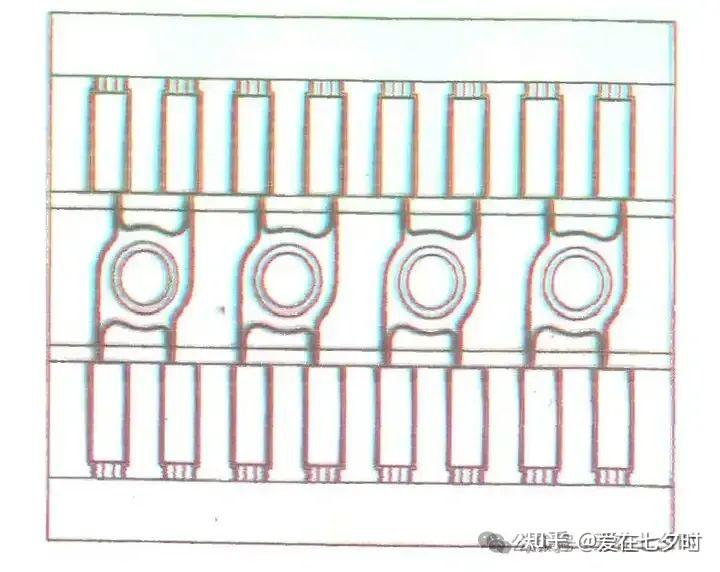

6、Lead Frame 各部名稱介紹

7、Lead-frame Structure

目前塑膠封裝佔有九成以上之市場,塑膠構裝方式之主要制程:

(1)封裝前晶圓處理 (Back Grinding & Wafer Mount)

(2)晶圓切割(Dicing)

(3)固晶(Die Bonding)

(4)引線鍵合(Wire Bonding)

(5)封膠(Molding)

(6)去膠去緯(Dejunk/Deflash)

(7)蓋印(Marking)

(8)電鍍(Plating)

(9)剪切成型(Trim/Form)

(10)檢測(Testing)

八、集成電路(IC)封裝的過程

1、封裝前晶圓處理

(Wafer Testing / Back Grinding /Back Grinding& Wafer Mount)

- 晶圓在晶圓廠生產后厚度約在675μm左右,因考慮封裝的包裝產品厚度而必須加以研磨成540μm / 380μm / 280μm / 200μm或者不做研磨,依厚度之不同,亦可考慮一次或二次磨。

Wafer Grinding

Purpose: To reduce wafer thickness depending onthe package type the wafer will be built into.

2、晶圓切割(Die Saw)

晶圓切割的目的, 主要是要將晶圓上的每一顆晶粒加以完全(100%)切割分離,首先將晶圓貼片( Wafer Mount )送至晶圓切割機, 以圓形鉅切刀進行切割,切割完成后一顆顆晶粒即井然有序地排列於晶圓藍膜上, 且經由藍膜張力與框架之支撐,晶粒可完全分離不致發生碰撞同時易于搬運。

Wafer Saw

Purpose: To cut the wafer according to the die sizes.

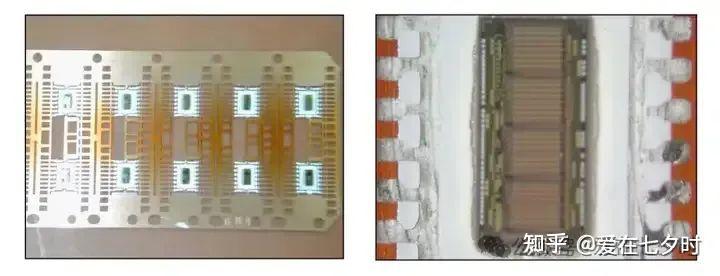

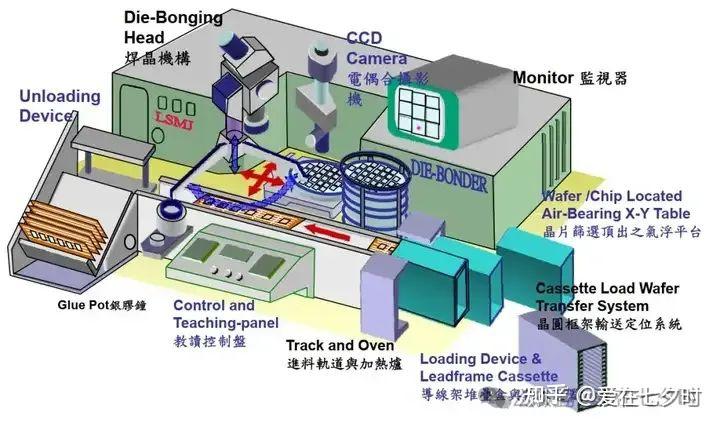

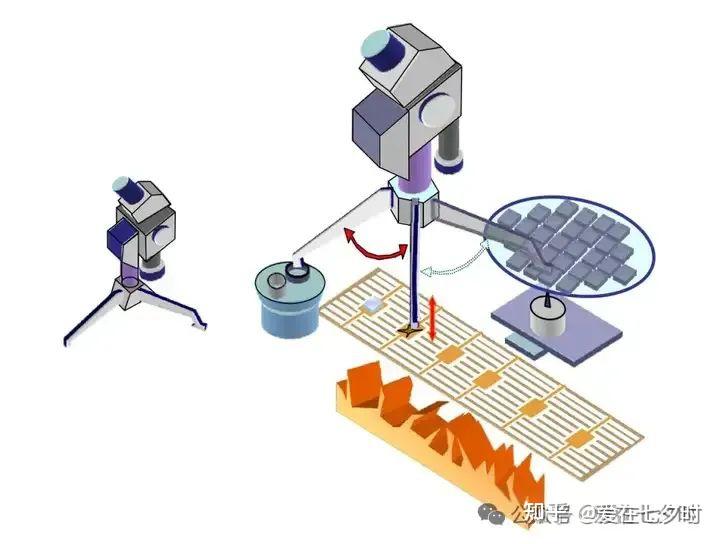

3、固晶(Die Bonding)

固晶的目的,主要是要將上一站切割完成之晶粒置放于導線架上,並利用環氧樹脂(業界俗稱銀膠)或熱固共晶( eutetic)接著(熱固式溫度大約在400℃ ~500℃ )等方式加以黏著固定于導線架之晶座(Die Pad)上。

Die Attach

Purpose: To attah the die to the lead frame ( pad) using epoxy.

Epoxy

(1)Component : Resin (liquid)

(2)Purpose : Attach dice on L/F pad

(3)Properties : Needs to store under - 40℃ and thaw for 30 minutes (min.) beforeusing.

(1)Die Bonder

(2)Die Pick-Up

(3)Die Pick & Attach

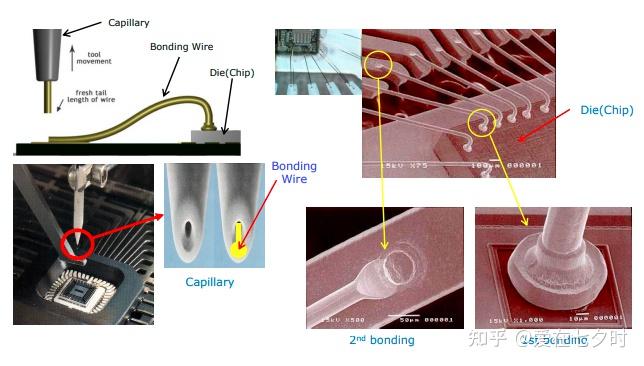

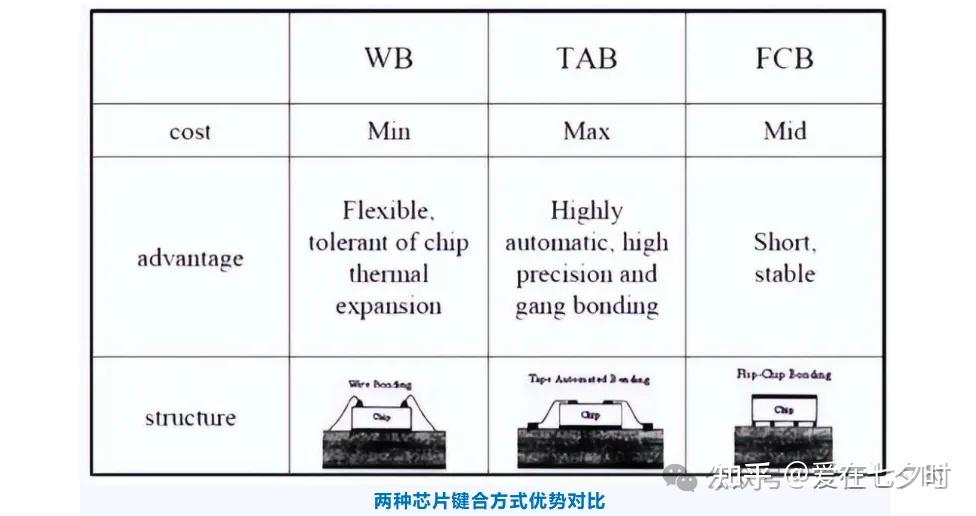

4、引線鍵合( Wire Bonding)

引線鍵合的目的,是要將晶粒上的訊號點,以金屬線(通常微金線)連接到導線架的內引腳,藉此將IC的訊號傳遞到外界, 焊線又分成金線 /鋁線 / 銅線,引線所用之金線直徑從25μm到50μm。

(1)Ball Bond (球焊)

(2)Wire bonding

Purpose: To connect the die and the leads using Goldwire.

(3)Gold Wire

1.Component : 99.99% gold

2 Diameter: 0.7 ~ 2.0 mil (Thinner than hair)

3.Function : To connect the die and the leads.

(4)Wire Bonding M/C

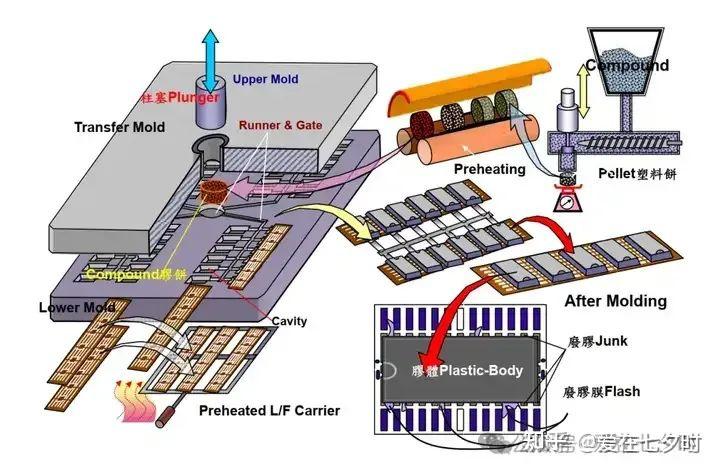

5、封膠(Moldiing)

封膠最主要是要將晶粒與外界隔離,以避免其上與外連接訊號之金線被破壞, 同時亦需具有防止濕氣進入之功能,以避免產生腐蝕與訊號破壞。其過程是將完成焊線之導線架置放于治具框架上,並加以預熱,再將此框架放入壓模機之封裝模具,並將半熔融態之環氧樹脂注入模具中, 待冷卻硬化后即可取出。

(1)Moldiing

(2)Mold

Purpose: To encapsulate the wire bonded die to protect from moisture and physical damage.

(3)Molding Equipment

(4)Mold Compound

A:Component : Resin (solid)

B:Purpose : Encapsulate the die for protection against moisture and physical damage.

(5)Conventional Mold

(6)Conventional Mold

Unbalanced Flow (Christmas tree)

(7)Conventional Mold(Gang-Pot Mold)

Schematic of Single Chase

(8)Multi-Plunger Mold (Gang-Pot Mold)

Balance Flow

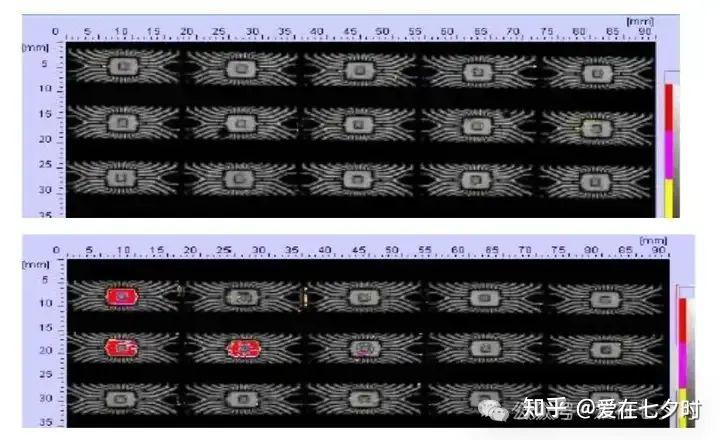

(9)Molding SAT Inspection

30C,60%RH,192hrs,IR*3 SAT result die surface delamination<10%

lead frame delamination <100%

LEVEL 3

6、去膠去緯(Dejunk/Deflash)

去膠去緯是將封膠后殘留在導線架上接腳與接腳間之溢膠連同腳間緯桿(Dam Bar)利用Punch之方式一起切除。而Deflash是要清除沾覆於接腳或連接杠表面之廢膠薄膜, 昔日有用人工刮除方式,毛刷輪機械刷除,噴砂去除或用高壓水(Water Jet)噴凈等。但隨著Molding與鑄模技術之提升Flash量趨少,從有存在亦漸薄化, 故有些過程將Deflash移至電鍍過程中,進行強酸清洗過程時將膠膜軟化自然脫落。

De-junk / Trim

Purpose: Trim - to cut dam bar

De-junk – to remove side flash.

7、蓋印(Marking)

蓋印主要是要於封膠體的上表面或背面印制IC型式編號廣告牌, 蓋印方式分印漆(INK)、鐳射( Laser),其中印漆式則考慮不會漏/ 漆,鐳射則需控制鐳射深度。

Bottom Mark (Ink/Laser)

Purpose: To mark molded units for tracing purposes of the device, lot no, date manufactured, etc.

8、電鍍(Plating)

為使IC元件成品容易上板(On Board)與配合表面接著技術(SMT)須與IC外接腳上鍍上一層錫鉛層電鍍。因考慮測試機刮錫的問題,錫鉛比已從 80% 比 20% 改 為 85% 比 或 90%比10%,且因應歐盟RoHS之實施,目前改善為Pb-free。

(1)Solder Plating

Purpose: To protect external leads from corrosi d on and to have good connection during board mount.

(2)Solder Plating Equipment

9、剪切成型(Trim/Form)

其主要目的是將導線架上封膠完成的IC體進行外接腳長剪切(Lead Length Triming),彎腳成型(Bending)與分離(Singulation)等工作。沖切彎腳機依導線架是單條或多條( matrix) 之設計方式而有不同的沖切方式(如Punch / roller Bend / cam Form),此站的品質要求為不能有毛邊 / 沖切不對稱 /平面度管制。而其中平面度在QFP產品尤其重要,至于BGA則有沖切( punch) 及切割( saw)二種方式。

(1)Trimming & Forming

(2)Form / Singulation

Purpose: To form the shape of the lead (J-bend, gull wing) and detach each unit from the lead frame.

(3)Solid Forming:

Molding 完成后之導線架由 L/F Magazine(線架匣) 送入輸送流道偵測方向,衝切外角尖端連接邊,切外接腳長度尺寸,再進入下一站作彎腳成型,最終成型,後送入塑膠管盒。

(4)Swimming Cam Forming:

Molding 完成后之導線架由 L/F Magazine(線架匣) 送入輸送流道偵測方,衝切外角尖端連接邊,再進行懸浮擺動凸輪彎腳成型,切外接腳長度尺寸,最終成型,后送入塑膠管盒。

10、測試(Testing/Inspection)

測試的目的主要是要確定經過封裝完畢之晶粒是否功能正常與符合規格,檢測項目包括:Go / Nogo、外引腳平整性、共面性、引腳曲、電鍍層均勻度,膠體完整與蓋印清晰度等。

總結一下

在電子信息化產業進一步完善和市場發展過程中,半導體生產企業應盡可能地提升其封裝工藝,通過半導體內部封裝連接方式相互關系的總結與梳理以及半導體前端制造工藝對整個封裝技術應用的影響關系梳理,充分感知半導體封裝技術的現階段應用現狀及未來創新方向,為半導體封裝技術應用水平的快速提升打下扎實基礎。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

半導體

+關注

關注

339文章

31085瀏覽量

265799 -

封裝

+關注

關注

128文章

9305瀏覽量

148946

發布評論請先 登錄

半導體金線鍵合(Gold Wire Bonding)封裝工藝技術簡介;

半導體芯片制造技術——“芯片鍵合”工藝技術的詳解;

熱壓鍵合工藝的技術原理和流程詳解

半導體封裝Wire Bonding (引線鍵合)工藝技術的詳解;

半導體芯片封裝“CoWoS工藝技術”的詳解;

關于先進碳化硅(Sic)功率半導體封裝工藝技術的詳解;

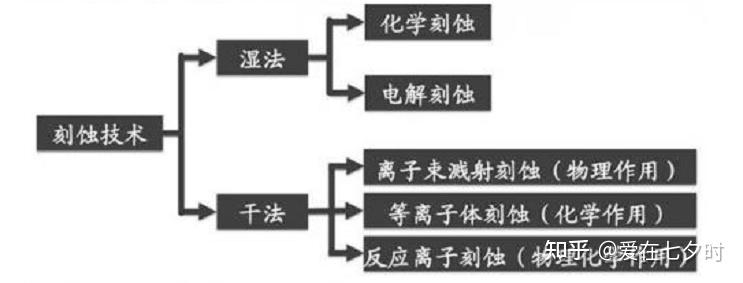

半導體“刻蝕(Etch)”工藝技術的詳解;

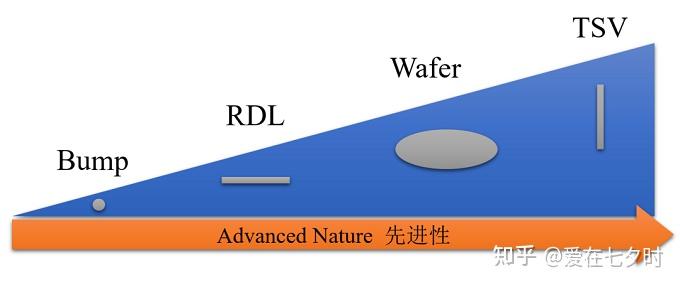

半導體先進封裝“Bumping(凸點)”工藝技術的詳解;

半導體“楔形鍵合(Wedge Bonding)”工藝技術的詳解;

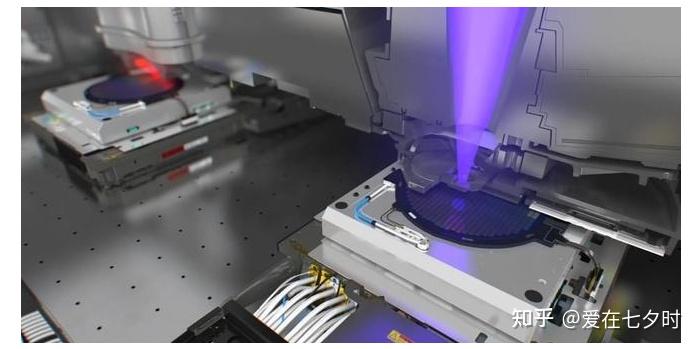

半導體“光刻(Photo)”工藝技術的詳解;

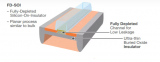

SOI工藝技術介紹

半導體后道制程“芯片鍵合(Die Bonding)”工藝技術的詳解;

半導體封裝中的裝片工藝介紹

半導體“封裝過程”工藝技術的詳解;

半導體“封裝過程”工藝技術的詳解;

評論