在最近舉辦的GSA存儲大會上,芯片制造業的四大聯盟組織-IMEC, ITRI, Sematech以及SEMI都展示了他們各自在基于TSV的3D芯片技術方面的最新進展

2011-04-14 18:38:31 7492

7492

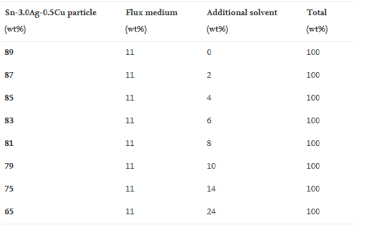

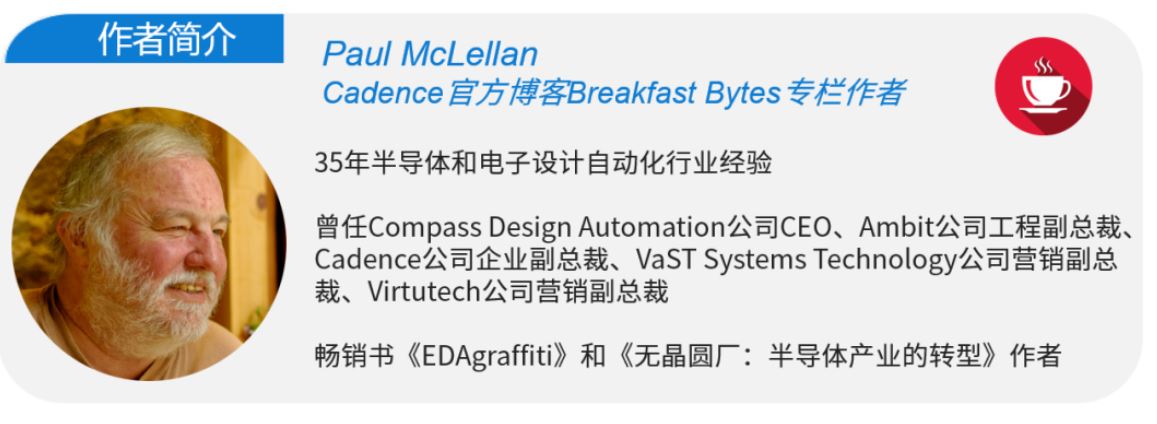

本文研究主要考慮基于CuSn金屬互化物的微凸點(μbump)作為芯片堆疊的手段。系統研究了形成金屬互化物凸點連接的兩種方法。

2012-03-08 16:29:24 6956

6956

據IC Insights發布的最新2020 McClean報告顯示,半導體行業研發的投入將在2024年出現明顯成效包括轉向EUV光刻,低于3納米制程技術,3D芯片堆疊技術和先進封裝在內的技術挑戰有望

2020-01-31 09:20:34 7042

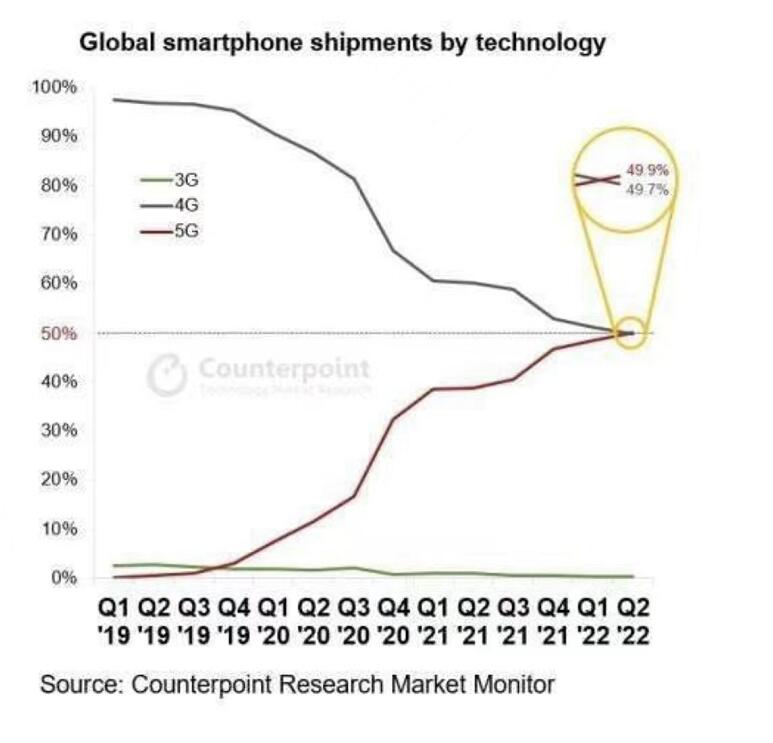

7042 3D堆疊、多芯片封裝大家想必都不陌生了,這年頭制造工藝已經沒有太多噱頭,有時甚至性能提升也有限,廠商只好從架構上入手。像蘋果的Ultra?Fusion拼接、Graphcore的3D WoW,都是在

2022-04-13 01:06:00 7527

7527 視為堆疊邏輯與內存、3D NAND,甚至可能在高帶寬存儲(HBM)中的多層DRAM堆疊的關鍵技術。垂直堆疊使得芯片制造商能夠將互連間距從35μm的銅微凸點提升到10μm甚至更小。

2025-05-22 11:24:18 1405

1405

半導體協會理事長盧超群指出,未來半導體將要做3D垂直堆疊,全球半導體產業未來會朝向類摩爾定律成長。

2016-06-10 00:14:00 2696

2696 三星作為全球首家量產3D NAND Flash的廠商的風光并沒有太久,日前東芝也研究出64層3D Flash,這樣的追趕速度讓人驚嘆。有消息顯示,英特可能暫緩擴建大連廠,而是通過直接收購美光科技擴大芯片領域實力。索尼PlayStation VR國行版來襲,紅米Pro三個版本還有什么發布會沒說的細節?

2016-07-28 09:44:26 1235

1235 據外媒報道,東芝今天宣布正式出貨BiCS FLASH 3D閃存,采用64層堆疊,單晶粒容量512Gb(64GB,TLC),相對于上一代48層256Gb,容量密度提升了65%,這樣封裝閃存芯片的最高容量將達到960GB。

2017-02-23 08:33:40 1752

1752 臺積電(中國)有限公司技術總監陳敏表示,TSMC 3D Fabric先進封裝技術涵蓋 2.5D 和垂直芯片堆疊產,是臺積電過去10年以來對于3D IC的不斷完善和開發。客戶采用臺積3D Fabric所生產的產品取得的整個系統效能的提升,都有非常良好的表現。

2022-09-20 10:35:47 2930

2930

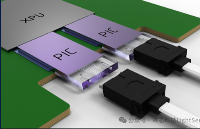

先進封裝從MCM發展到2.5D/3D堆疊封裝,目前發展最快的制造商是TSMC。TSMC從Foundry端延伸入2.5D/3D先進封裝,稱為3D Fabric。近十年來TSMC的2.5D先進封裝技術

2022-10-26 10:21:37 5940

5940 對于自動駕駛應用來說,3D 場景感知至關重要。3D點云數據就是具有3D特征的數據。一方面,3D 點云可以直接用來獲取障礙物的距離和大小,以及場景的語義信息。

2023-12-28 16:35:22 2712

2712

背景部分介紹了3D點云應用領域中公開可訪問的數據集的重要性,這些數據集對于分析和比較各種模型至關重要。研究人員專門設計了各種數據集,包括用于3D形狀分類、3D物體檢測和3D點云分割等任務的數據集。

2024-02-22 16:16:47 2454

2454

3D堆疊像素探測器芯片技術詳解

2024-11-01 11:08:07 4435

4435

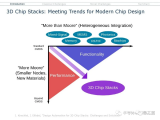

3D堆疊將不斷發展,以實現更復雜和集成的設備——從平面到立方體

2024-09-19 18:27:41 2348

2348

3D 集成電路的優勢有目共睹,因此現代芯片中也使用了 3D 結構,以提供現代高速計算設備所需的特征密度和互連密度。隨著越來越多的設計集成了廣泛的功能,并需要一系列不同的特征,3D 集成將與異構集成

2024-12-03 16:39:31 2918

2918

動力。 ? 據資料顯示,這項技術通過將銅金屬鍵合與介電層鍵合工藝結合,實現了亞微米級的垂直互連,使芯片堆疊密度提升兩個數量級,為突破摩爾定律物理極限提供了可行路徑。 ? 二十年來,錫基焊料凸點(Micro Bump)一直是芯片堆疊的標準導線。但當

2025-06-29 22:05:13 1519

1519 什么是3D圖形芯片?3D圖像生成算法的原理是什么?

2021-06-04 06:29:06

成微型的往往會導致很差的效果。比如建筑模型,在打印這種模型時尺寸非常關鍵,因為包含的細節非常之多,你將尺寸調的越小,3D 打印模型能展現出來的細節就越少。Sculpteo建議大家在打印精細的模型

2016-05-05 14:31:56

我公司專業從事3D全息風扇研發生產,主要生產供應3D全息風扇PCBA,也可出售整機,其他配件可免費提供供應商信息或者代購,歡迎咨詢 劉先生:*** 微信同號3d全息風扇燈條3d全息風扇PCBA3D全息風扇方案本廣告長期有效

2019-08-02 09:50:26

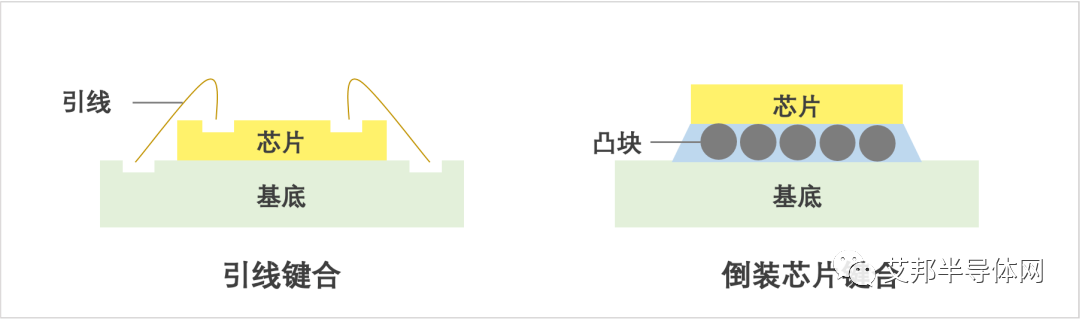

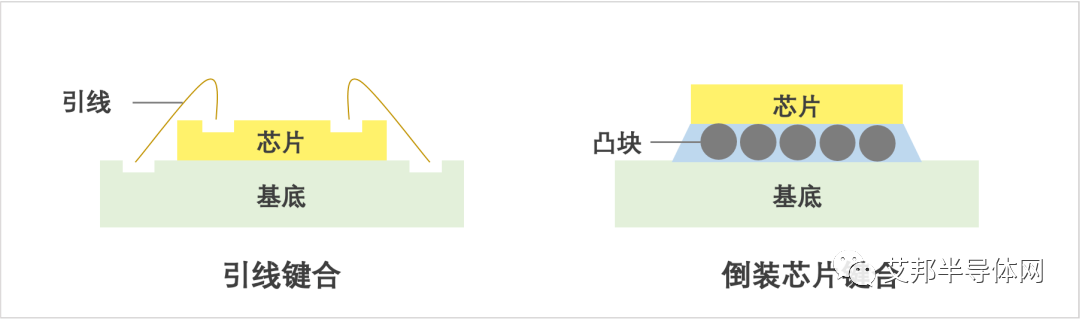

芯片封裝鍵合技術各種微互連方式簡介微互連技術簡介定義:將芯片凸點電極與載帶的引線連接,經過切斷、沖壓等工藝封裝而成。載帶:即帶狀載體,是指帶狀絕緣薄膜上載有由覆 銅箔經蝕刻而形成的引線框架,而且芯片

2012-01-13 14:58:34

正在從二維走向三維世界——芯片設計、芯片封裝等環節都在向3D結構靠攏。晶體管架構發生了改變當先進工藝從28nm向22nm發展的過程中,晶體管的結構發生了變化——傳統的平面型晶體管技術(包括體硅技術

2020-03-19 14:04:57

無線通信(CCWC),可以解決傳統芯片內采用金屬互連線、硅通孔燈通信的瓶頸,提高芯片的性能和能效,同時大大縮小面積。

CCWC面臨的挑戰:

2、3D堆疊

1)3D堆疊技術的發展

3D堆疊技術最早應用于

2025-09-15 14:50:58

世界首款3D芯片工藝即將由無晶圓半導體公司BeSang授權。 BeSang制造了一個示范芯片,在邏輯控制方面包含1.28億個縱向晶體管的記憶存儲單元。該芯片由韓國國家Nanofab和斯坦福

2008-08-18 16:37:37

如何同時獲取2d圖像序列和相應的3d點云?以上來自于谷歌翻譯以下為原文How to obtain the sequence of 2d image and corresponding 3d point cloud at the same time?

2018-11-13 11:25:01

`華爾街日報發布文章稱,科技產品下一個重大突破將在芯片堆疊領域出現。Apple Watch采用了先進的的3D芯片堆疊封裝技術作為幾乎所有日常電子產品最基礎的一個組件,微芯片正出現一種很有意思的現象

2017-11-23 08:51:12

大家好, 在Ultrascale FPGA中,使用單片和下一代堆疊硅互連(SSI)技術編寫。 “單片和下一代堆疊硅互連(SSI)技術”是什么意思?謝謝娜文G K.

2020-04-27 09:29:55

3D 點云。高度差異化 3D 機器視覺系統利用 DLP?(...)主要特色 集成型 API 和針對 DLP 芯片組的驅動程序支持,可實現快速以及可編程圖形針對同步捕捉的集成型攝像機支持投影儀和攝像機校準例程用于生成視差圖、景深圖和點云的結構光算法API 文檔應用和源代碼的完全訪問權限

2018-10-12 15:33:03

構建精細的 3D 點云。作為緊湊或手持解決方案的理想之選,此高分辨率 3D 掃描儀系統利用 DLP?(...)主要特色針對 DLP 芯片組的集成型 API 和驅動程序支持,可實現快速以及可編程圖形集成型攝像頭支持,實現同步捕捉投影儀和攝像頭校準例程用于生成視差圖、景深圖和點云的結構化照明算法

2018-09-18 08:38:28

3D 點云。高度差異化 3D 機器視覺系統利用 DLP? LightCrafter? 4500 估模塊 (EVM)(采用 DLP? 0.45 英寸 WXGA 芯片組),能夠靈活控制工業、醫療和安全

2022-09-22 10:20:04

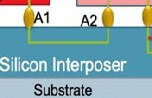

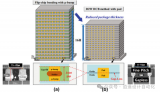

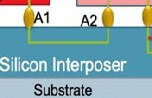

被稱之為“堆疊硅片互聯技術”的3D封裝方法采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術,實現了多芯

2010-10-29 17:54:25 1168

1168 單片型3D技術實現的關鍵在于如何將各層功能單元轉換到單片3D堆疊結構之中去,其采用的方法非常類似于Soitec在制作SOI晶圓時所采用的SMARTCUT技術

2011-05-04 11:27:21 2198

2198

據臺灣對外貿易發展協會(TAITRA)透露,芯片代工巨頭臺積電(TSMC)有望超過intel,在2011年底推出業內首款采用3-D芯片堆疊技術的半導體芯片產品。

2011-07-07 09:19:07 1168

1168 賽靈思采用了稱之為“堆疊硅片互聯技術”的 3D 封裝方法,該技術采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術,實現了多芯片可編程平臺

2011-10-26 14:35:26 3936

3936 2012年4月27日訊 - GLOBALFOUNDRIES今天宣布,在為新一代移動和消費電子應用實現3D芯片堆疊的道路上,公司達到了一個重要的里程碑。在其位于美國紐約薩拉托加郡的Fab 8,GLOBALFOUNDRIES已開始

2012-04-28 09:15:03 1772

1772 9月25日——全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)今天宣布,臺積電與Cadence合作開發出了3D-IC參考流程,該流程帶有創新的真正3D堆疊。該流程通過

2013-09-26 09:49:20 1717

1717 光固化3D打印技術憑借成型表面質量好、尺寸精度高以及能夠實現比較精細的細微之處等特點,在3D打印圈小有名氣,也得到了廣泛的應用。今天咱們不談技術,聊聊光固化3D打印技術的核心——光敏樹脂材料

2017-06-27 17:48:57 10848

10848 ;x>nkedIn上發表了一篇跟澳大利亞科技公司優立(Euclideon)所使用的點云數據有關的文章,并在業內引起了一番討論。 1. 點云的問題 點云是由3D掃描硬件收集的數據,如FARO的Focus 3D激光掃描儀和Shining 3D的Einscan Pro。捕獲3D對象的基本原理是3D掃描儀反饋光

2017-09-15 09:28:05 20

20 。即便是掃描最小的對象,系統都會創建上百萬這樣的點,所以要管理這樣的海量數據并不容易。CAD軟件可以連接各個點,但這一過程需要大量的計算資源,完善成品模型往往是一個艱苦的過程。 從點云(右)到完成的3D模型(左和中心) 優立的無限細節算法集成到SOLIDSCAN軟件中后能夠實時渲染點

2017-09-27 15:27:25 17

17 芯片晶粒在未來搭載愈來愈多晶體管可望成為趨勢,讓芯片運算能力達到人腦水平也可望有朝一日達成,對于這類新技術的發展,在芯片上以及在多層堆疊芯片之間打造先進3D結構成為一大主要驅動力,在2017年

2017-12-20 08:45:50 5710

5710 這款工業級3D相機使用動態結構光方案實現高精度三維點云輸出,采用知微傳感自有的MEMS微振鏡技術,實現了3D相機的小型化、低成本和高精度。

2018-09-14 10:59:48 5470

5470 被稱之為“堆疊硅片互聯技術”的3D封裝方法采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術,實現了多芯片可編程平臺。

2019-01-03 13:20:59 3796

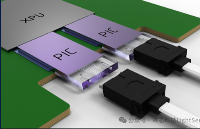

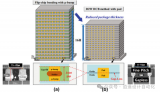

3796 在近日舉行的英特爾“架構日”活動中,英特爾不僅展示了基于10納米的PC、數據中心和網絡系統,支持人工智能和加密加速功能的下一代“Sunny Cove”架構,還推出了業界首創的3D邏輯芯片封裝技術——Foveros。這一全新的3D封裝技術首次引入了3D堆疊的優勢,可實現在邏輯芯片上堆疊邏輯芯片。

2018-12-14 15:35:32 8854

8854 英特爾近日向業界推出了首款3D邏輯芯片封裝技術“Foveros”,據悉這是在原來的3D封裝技術第一次利用3D堆疊的優點在邏輯芯片上進行邏輯芯片堆疊。也是繼多芯片互連橋接2D封裝技術之后的又一個顛覆技術。

2018-12-14 16:16:45 3316

3316 近日,武漢新芯研發成功的三片晶圓堆疊技術備受關注。有人說,該技術在國際上都處于先進水平,還有人說能夠“延續”摩爾定律。既然3D芯片堆疊技術有如此大的作用,那今天芯師爺就跟大家一起揭開它的面紗。

2018-12-31 09:14:00 34067

34067 對于目前的高端市場,市場上最流行的2.5D和3D集成技術為3D堆疊存儲TSV,以及異構堆疊TSV中介層。Chip-on-Wafer-on-Substrate(CoWos)技術已經廣泛用于高性能計算

2019-02-15 10:42:19 8043

8043

從英特爾所揭露的技術資料可看出,Foveros本身就是一種3D IC技術,透過硅穿孔(Through-Silicon Via, TSV)技術與微凸塊(micro-bumps)搭配,把不同的邏輯芯片堆疊起來。

2019-07-08 11:47:33 5835

5835 對于3D封裝技術,英特爾去年宣布了其對3D芯片堆疊的研究,AMD也談到了在其芯片上疊加3D DRAM和SRAM的方案。

2019-08-13 10:27:53 3414

3414 困于10nm的Intel也在這方面尋找新的機會,其在去年年底的“架構日”活動中,推出其業界首創的3D邏輯芯片封裝技術——Foveros,Foveros首次引入3D堆疊的優勢,可實現在邏輯芯片上堆疊

2020-01-28 16:10:00 4118

4118 德國3D打印機制造商EOS展示了其超精細細節分辨率(FDR,FINE DETAIL RESOLUTION)3D打印技術。

2020-05-18 14:51:35 3339

3339 SIP有多種定義和解釋,其中一說是多芯片堆疊的3D封裝內系統集成,在芯片的正方向堆疊2片以上互連的裸芯片的封裝。SIP是強調封裝內包含了某種系統的功能封裝,3D封裝僅強調在芯片方向上的多芯片堆疊

2020-05-28 14:51:44 7076

7076 與傳統的大面積SoC相比,3D IC具有許多優勢,其中大部分是由于縮短了互連。與2D SoC中的長線相反,功能塊彼此堆疊并通過TSV連接,因此3D IC能夠顯著縮短互連長度。

2020-09-14 16:52:22 2925

2925 三星計劃明年開始與臺積電在封裝先進芯片方面展開競爭,因而三星正在加速部署3D芯片封裝技術。

2020-09-20 12:09:16 3743

3743 在Intel、臺積電各自推出自家的3D芯片封裝技術之后,三星也宣布新一代3D芯片技術——X-Cube,基于TSV硅穿孔技術,可以將不同芯片搭積木一樣堆疊起來,目前已經可以用于7nm及5nm工藝。

2020-10-10 15:22:58 2004

2004 測量表面法向量估計 幾何測量平面提取 3D重建從離散點云得到光滑曲面 3D重建ICP點云配準 3D重建SDF表面重建 應用例子:從稀疏的點云中,構造出可以3D打印的模型 3D物體分割、識別與測量 應用算法流程3D物體分割、識別與測量 應用算法流程靜態手勢識別 應用算

2020-10-23 09:40:46 4061

4061

電子發燒友網為你提供3D堆疊技術的誘因資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:50:58 12

12 倒裝芯片技術正得到廣泛應用 ,凸點形成是其工藝過程的關鍵。介紹了現有的凸點制作方法 ,包括蒸發沉積、印刷、電鍍、微球法、黏點轉移法、SB2 - Jet 法、金屬液滴噴射法等。每種方法都各有其優缺點 ,適用于不同的工藝要求。可以看到要使倒裝芯片技術得到更廣泛的應用 ,選擇合適的凸點制作方法是極為重要的。

2021-04-08 15:35:47 26

26 堆疊技術也可以叫做3D堆疊技術,是利用堆疊技術或通過互連和其他微加工技術在芯片或結構的Z軸方向上形成三維集成,信號連接以及晶圓級,芯片級和硅蓋封裝具有不同的功能,針對包裝和可靠性技術的三維堆疊處理技術。

2022-05-10 15:58:13 4946

4946

融合標注使用的3D標注工具仍以3D立體框為主,但在3D點云數據以外,還需要使用2D標注工具在點云數據相對應的2D圖像中進行標注,3D點云數據中的標注對象與2D圖像中的標注對象一一對應,具體形式如下:

2022-07-21 15:52:36 10125

10125 異質整合需要通過先進封裝提升系統性能,以2.5D/3D IC封裝為例,可提供用于存儲器與小芯片集成的高密度互連,例如提供Sub-micron的線寬與線距,或五層的互連,是良好的Interposer(中介層)。

2022-08-24 09:35:53 5418

5418 目前有多種基于 3D 堆疊方法, 主要包括: 芯片與芯片的堆疊( D2D) 、芯片與圓片的堆疊( D2W ) 以及圓片與圓片的堆疊( W2W) 。

2022-11-01 09:52:51 2488

2488 當裸片尺寸無法繼續擴大時,開發者開始考慮投入對 3D 堆疊裸片方法的研究。考慮用于 3D 封裝的高端器件已經將當前的可測試性設計 (DFT) 解決方案推向了極限。

2023-02-28 11:39:26 2362

2362 我們之前見過的閃存多屬于Planar NAND平面閃存,也叫有2D NAND或者直接不提2D的,而3D 閃存,顧名思義,就是它是立體堆疊的,Intel之前用蓋樓為例介紹了3D NAND,普通NAND是平房,那么3D NAND就是高樓大廈,建筑面積一下子就多起來了,理論上可以無線堆疊。

2023-03-30 14:02:39 4227

4227 裸芯通過微凸點組裝到Interposer上,如上圖所示。其Interposer上堆疊了三顆裸芯。Interposer包括兩種類型的互聯:①由微凸點和Interposer頂部的RDL組成的水平互連,它連接各種裸芯②由微凸點、TSV簇和C4凸點組成的垂直互聯,它將裸芯連接至封裝。

2023-04-10 11:28:50 14215

14215 在Hybrid Bonding前,2D,2.5D及3D封裝都是采用焊錫球凸點(solder bump)或微凸點(Micro bump)來實現芯片與基板

2023-04-20 09:40:16 21819

21819 隨著計算機視覺技術的不斷發展,3D 數字化技術已經成為了當今工業制造領域和三維醫學影像領域的關鍵技術。然而,構建高精度、高分辨率的 3D 點云數據集對于實現這一技術至關重要。在這篇文章中,我們將深入探討 3D 點云數據集的構建、應用以及其在 3D 數字化技術中的重要性。

2023-05-06 16:46:17 2219

2219 凸塊制造技術(Bumping)是在芯片上制作凸塊,通過在芯片表面制作金屬凸塊提供芯片電氣互連的“點”接口,廣泛應用于 FC、WLP、CSP、3D 等先進封裝。

2023-05-15 16:42:19 7001

7001

3D NAND閃存是一種把內存顆粒堆疊在一起解決2D或平面NAND閃存限制的技術。這種技術垂直堆疊了多層數據存儲單元,具備卓越的精度,可支持在更小的空間內,容納更高的存儲容量,從而有效節約成本、降低能耗,以及大幅度地提升性能。

2023-06-15 09:37:56 3209

3209

隨著異構集成模塊功能和特征尺寸的不斷增加,三維集成技術應運而生。凸點之間的互連 是實現芯片三維疊層的關鍵,制備出高可靠性的微凸點對微電子封裝技術的進一步發展具有重要意 義。整理歸納了先進封裝中的凸點

2023-07-06 09:56:16 5076

5076

相對于傳統平面型的金絲鍵合焊接的MMIC應用,三維(3D)多芯片互連封裝MMIC以其高集成度、低損耗、高可靠性等性能優勢,正逐步在先進電路與系統中得到應用。而3D封裝引入的復雜電磁耦合效應,在傳統

2023-08-30 10:02:07 5731

5731

隨著摩爾定律接近物理界限,在3納米以下的先進工藝中,能夠負擔較高費用的顧客受到限制,晶片sip和邏輯芯片的3D堆疊概念正在成為重要的新一代趨勢。

2023-09-11 11:09:58 2010

2010 長期以來,個人計算機都可以選擇增加內存,以便提高處理超大應用和大數據量工作的速度。由于3D芯片堆疊的出現,CPU芯粒也有了這個選擇,但如果你想打造一臺更具魅力的計算機,那么訂購一款有超大緩存的處理器可能是正確的選擇。

2023-10-15 10:24:23 2733

2733

多個垂直堆疊的活動層(模具)較短的垂直互連:功耗、延遲、帶寬..分離的和小的模具:異構集成,產量,成本,尺寸山復雜設計、設計自動化和制造過程

2023-10-17 12:25:50 1388

1388

VT6000系列共聚焦顯微鏡擅長微納級粗糙輪廓的檢測,配備了真彩相機并提供還原的3D真彩圖像,具有很強的縱向深度的分辨能力,所展示的圖像形態細節更清晰更微細,橫向分辨率更高。為國內3D顯微檢測的應用場景提供更全的解決方案。

2023-02-03 10:31:49 3

3 3D實例分割(3DIS)是3D領域深度學習的核心問題。給定由點云表示的 3D 場景,我們尋求為每個點分配語義類和唯一的實例標簽。 3DIS 是一項重要的 3D 感知任務,在自動駕駛、增強現實和機器人導航等領域有著廣泛的應用,其中可以利用點云數據來補充 2D 圖像提供的信息。

2023-11-13 10:34:27 3744

3744

三星計劃在2024年先進3D芯片封裝技術SAINT(Samsung Advanced Interconnection Technology,三星高級互連技術),能以更小尺寸的封裝,將AI芯片等高性能芯片的內存和處理器集成。

2023-11-15 11:09:30 2499

2499 來源:《半導體芯科技》雜志 ASIC設計服務暨IP研發銷售廠商智原科技(Faraday Technology Corporation)宣布推出其2.5D/3D先進封裝服務。通過獨家的芯片中介層

2023-11-20 18:35:42 1107

1107 當芯片變身 3D 系統,3D 異構集成面臨哪些挑戰

2023-11-24 17:51:07 1969

1969

在3D實現方面,存儲器比邏輯更早進入實用階段。NAND閃存率先邁向3D 。隨著目前量產的20-15nm工藝,所有公司都放棄了小型化,轉而轉向存儲單元的三維堆疊,以提高每芯片面積的位密度。它被稱為“ 3D(三維)NAND ” 。

2023-12-02 16:38:40 2967

2967

中得到了廣泛的應用。隨著3D封裝技術的發展,凸點鍵合技術也被應用于芯片-芯片、芯片-圓片鍵合及封裝體的3D疊層封裝。

2023-12-05 09:40:00 3259

3259

隨著I/O數量的增加,對具有更高性能的微小電子設備的高需求使得集成電路 (IC) 更加復雜,封裝技術也更迎來變革。隨著元件尺寸的減小,IC芯片與焊盤或印刷電路板的互連結構需要用到焊料凸點陣列,從而

2024-01-22 10:04:37 1063

1063

三星將在IEEE國際固態電路研討會上展示其GDDR7產品以及280層堆疊的3D QLC NAND技術。

2024-02-01 10:35:31 1299

1299 日月光半導體宣布VIPack? 平臺先進互連技術最新進展,透過微凸塊(microbump)技術將芯片與晶圓互連間距制程能力從 40um提升到 20um,可以滿足人工智能 (AI)應用于多樣化小芯片(chiplet)整合日益增長的需求。

2024-03-22 14:15:08 1191

1191 上的先進封裝技術應運而生。微凸點作為實現芯片到圓片異構集成的關鍵結構,可有效縮短信號傳輸距離,提升芯片性能。利用電沉積法在 Si基板上以 Cu作支撐層、Ni作阻擋層淀積微米級別的 Au/Sn凸點,所制得的多層凸點直徑約 60 μm、高度約 54 μm,其高

2024-03-23 08:42:10 1560

1560

先進封裝技術持續朝著連接密集化、堆疊多樣化和功能系統化的方向發展,探索了扇出型封裝、2.5D/3D、系統級封 裝等多種封裝工藝。晶圓微凸點技術已被廣泛應用于各種先進封裝工藝技術中,是最重要的基礎技術

2024-10-16 11:41:37 2939

2939

市場對于產品小型化需求增長,讓SiP(系統級封裝)和 PoP(疊成封裝)奠定了先進封裝的初始階段。此后,倒裝芯片(Flip-Chip)、晶圓級封裝(WLP)和3D IC封裝技術出現, 不斷縮短芯片之間的互連距離。近年來,先進封裝的發展非常快,臺積電

2024-11-21 10:14:40 4681

4681

引言 Cu-Cu混合鍵合(Cu-Cu Hybrid Bonding) 技術正在成為先進3D集成的重要技術,可實現細間距互連和高密度芯片堆疊。本文概述了Cu-Cu混合鍵合的原理、工藝、主要挑戰和主要

2024-11-24 12:47:06 3760

3760

隨著集成電路技術的飛速發展,芯片封裝技術也在不斷進步,以適應日益增長的微型化、多功能化和高集成化的需求。其中,球柵陣列封裝(BGA)作為一種先進的封裝技術,憑借其硅片利用率高、互連路徑短、信號傳輸

2024-11-28 13:11:04 3498

3498

晶圓微凸點封裝,更常見的表述是晶圓微凸點技術或晶圓級凸點技術(Wafer Bumping),是一種先進的半導體封裝技術。以下是對晶圓微凸點封裝的詳細解釋:

2024-12-11 13:21:23 1416

1416 在半導體行業的快速發展歷程中,芯片封裝技術始終扮演著至關重要的角色。隨著集成電路設計復雜度的不斷提升和終端應用對性能、功耗、尺寸等多方面要求的日益嚴苛,傳統的2D封裝技術已經難以滿足市場的需求。在此背景下,芯片3D堆疊封裝技術應運而生,成為半導體技術發展的新里程碑。

2025-02-11 10:53:45 2820

2820

隨著電子設備向小型化、高性能化發展,芯片封裝技術也在不斷演進。高密度芯片封裝是滿足現代電子產品需求的關鍵技術之一,而芯片互連技術作為封裝的核心環節,經歷了從焊球到銅柱再到微凸點的技術革新。本文將從

2025-02-20 10:06:00 3303

3303

在摩爾定律逼近物理極限的當下,先進封裝技術正成為半導體行業突破性能瓶頸的關鍵路徑。以系統級封裝(SiP)、晶圓級封裝(WLP)、3D堆疊、Chiplet異構集成為代表的顛覆性方案,正重新定義芯片性能

2025-04-10 14:36:31 1189

1189

隨著臺積電在 2011年推出第一版 2.5D 封裝平臺 CoWoS、海力士在 2014 年與 AMD 聯合發布了首個使用 3D 堆疊的高帶寬存儲(HBM)芯片,先進封裝技術帶來的片上互連拓撲結構的改變和帶來的集成能力的提升,成為當前片上互連技術發展的主要驅動因素。

2025-05-22 10:17:51 975

975

先進封裝中,凸點作為芯片互連的 “微型橋梁”,材料選擇需匹配場景:錫基焊料(SAC系列、SnBi)性價比高,適用于消費電子;銅基凸點適合高頻場景;金錫合金、金屬間化合物則用于特殊領域。其性能需滿足低

2025-07-05 10:43:03 1652

1652

凸點(Bump)是倒裝芯片的“神經末梢”,其從金凸點到Cu-Cu鍵合的演變,推動了芯片從平面互連向3D集成的跨越。未來,隨著間距縮小至亞微米級、材料與工藝的深度創新,凸點將成為支撐異構集成、高帶寬芯片的核心技術,在AI、5G、汽車電子等領域發揮關鍵作用。

2025-08-12 09:17:55 3767

3767

、3D及5.5D的先進封裝技術組合與強大的SoC設計能力,Socionext將提供高性能、高品質的解決方案,助力客戶實現創新并推動其業務增長。

2025-09-24 11:09:54 2350

2350

3D封裝架構主要分為芯片對芯片集成、封裝對封裝集成和異構集成三大類,分別采用TSV、TCB和混合鍵合等先進工藝實現高密度互連。

2025-10-16 16:23:32 1553

1553

在晶圓級封裝(WLP)中,Bump 凸點是芯片與基板互連的關鍵,主流實現方式有電鍍法、焊料印刷法、蒸發 / 濺射法、球放置法四類,差異顯著。選型需結合凸點密度、成本預算與應用特性,平衡性能與經濟性。

2025-10-23 14:49:14 1709

1709

?在芯片成品制造的環節中,堆疊封裝(StackedPackaging)是一種將多個芯片垂直堆疊在一起,通過微型互連方式(如TSV硅通孔、RDL重布線層、微凸點等)

2025-10-27 16:40:34 428

428

堅固的 IP67 防護等級,即便在強光直射下也能提供穩定的深度信息。無論是用于精細結構掃描,還是高性價比的 3D 采集,對于既需要高細節度又要求可靠深度數據的應用而言,Nion 都是理想之選。 二

2025-12-15 14:59:41 171

171

燒結銀:3D封裝中高功率密度和高密度互連的核心材料

2025-12-29 11:16:01 119

119

電子發燒友App

電子發燒友App

評論