倒裝芯片(Flip Chip)中的凸點(Bump)是實現(xiàn)芯片與基板/封裝體電氣互連的核心結(jié)構(gòu),其替代傳統(tǒng)引線鍵合的關(guān)鍵在于縮短信號路徑、提升I/O密度和散熱效率。下面作為微電子和半導(dǎo)體焊料廠家,傲牛科技工程師嘗試從焊料廠家的視角,從凸點(Bump)制作的工藝、材料、設(shè)備、演變歷程及未來趨勢展開詳細解析:

一、Bump 的制作工藝

凸點制作需經(jīng)歷底部金屬化(UBM,Under Bump Metallurgy)和凸點成型兩大核心步驟,具體工藝因精度、成本和材料需求分為以下幾類:

1. 底部金屬化(UBM)工藝

UBM是連接芯片Pad與凸點的過渡層,其作用包括:增強凸點與芯片表面的附著力、阻止凸點材料與芯片金屬(如 Al)之間的擴散、提供良好的導(dǎo)電性等。常見制作工藝包括:

濺射(Sputtering):在真空環(huán)境中通過離子轟擊靶材,將金屬(如 Ti/Cu/Ni/Au)沉積到芯片表面,形成多層薄膜(如 Ti(粘附層)+ Cu(擴散阻擋層)+ Au(抗氧化層))。適合高精度、小尺寸凸點,是目前主流工藝。

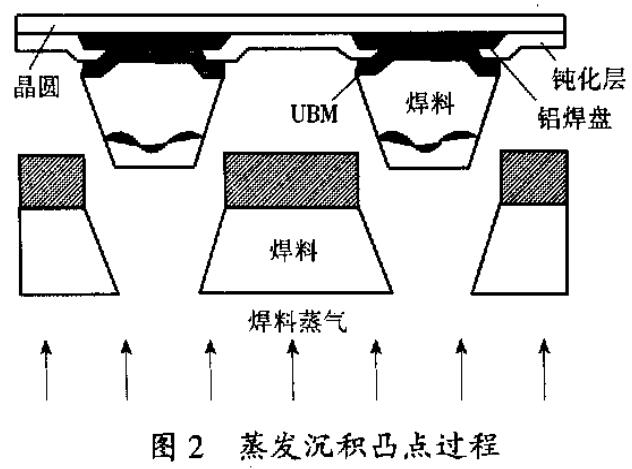

蒸發(fā)(Evaporation):通過加熱使金屬(如 Cr/Au)蒸發(fā)并沉積到芯片表面,工藝簡單但膜層均勻性較差,多用于早期低精度場景。

化學(xué)鍍(Electroless Plating):無需通電,通過化學(xué)反應(yīng)在芯片Pad表面沉積Ni/Au層,成本低但厚度控制精度差,適合中低端產(chǎn)品。

2. 凸點成型工藝

根據(jù)材料和精度需求,凸點成型工藝主要分為以下 5 類:

工藝類型 | 核心步驟 | 精度(間距) | 優(yōu)勢 | 劣勢 | 適用場景 |

電鍍法 | 光刻定義凸點圖形→電鍍金屬(Cu/SnAgCu 等)→去膠→刻蝕 UBM 多余部分 | 10-50μm | 精度高、一致性好、適合大批量 | 光刻成本高、工藝復(fù)雜 | |

蒸發(fā)法 | 真空蒸發(fā)金屬(如 Au/Sn)→通過掩膜板定義凸點形狀 | 50-200μm | 工藝簡單、無光刻步驟 | 凸點高度均勻性差、成本高 | 早期軍用 / 航天芯片 |

焊膏印刷法 | 用鋼網(wǎng)將焊膏(SnAgCu 等)印刷到 UBM 上→回流焊使焊膏熔融成型 | 50-300μm | 成本低、效率高 | 精度低、不適合小間距 | |

球焊法 | 用金絲球焊機在 Pad 上形成金球→熱壓使金球變形→鍍 Sn 層(形成 Au-Sn 合金) | 100-500μm | 設(shè)備兼容性強、適合中小批量 | 凸點高度一致性差 | 汽車電子(低 I/O 密度場景) |

電鍍 - 回流法 | 電鍍 Cu 核→電鍍 Sn 層→回流焊使 Sn 層熔融包裹 Cu 核(形成核殼結(jié)構(gòu)) | 10-30μm | 結(jié)合 Cu 的高導(dǎo)電與 Sn 的焊接性 | 工藝步驟多 | 高密度互連(如 HBM 封裝) |

二、Bump的材料體系

凸點材料需滿足導(dǎo)電性、焊接性、機械強度和可靠性(抗熱循環(huán)、抗腐蝕)要求,核心材料分為以下幾類:

1. 凸點主體材料

錫基合金(無鉛為主):SnAgCu(最主流,熔點 217℃)、SnBi(低溫,熔點 138℃,適合不耐高溫芯片)、SnCu(成本低,熔點 227℃)。優(yōu)勢是焊接性好、工藝成熟,缺點是導(dǎo)電率低于Cu/Au,且易產(chǎn)生電遷移。

銅(Cu):導(dǎo)電率高(約58×10? S/m)、成本低于Au,適合高電流場景。但表面易氧化,需鍍層保護(如Sn、Ni/Au),形成“Cu核+鍍層”的核殼結(jié)構(gòu)。

金(Au):可靠性極高(抗腐蝕、抗遷移),但成本昂貴,僅用于高端軍工、航天芯片(如Au-Sn共晶合金,熔點280℃)。

其他材料:銀(Ag)導(dǎo)電性優(yōu)異但易遷移;鎳(Ni)作為阻擋層,常與Au結(jié)合形成Ni/Au凸點(適合金絲鍵合轉(zhuǎn)倒裝場景)。

2. UBM 材料

UBM 通常為多層結(jié)構(gòu),典型組合包括:

Ti(粘附層,增強與芯片SiO?的結(jié)合)+ Cu(擴散阻擋層+導(dǎo)電層)+ Au(抗氧化層):適合Cu凸點或錫基凸點。

Cr(粘附層)+ Au(導(dǎo)電+抗氧化):適合Au凸點,成本高但可靠性強。

Ni(擴散阻擋層)+ Au(抗氧化層):適合化學(xué)鍍工藝,用于中低端錫基凸點。

三、Bump 制作的核心設(shè)備

不同工藝對應(yīng)的關(guān)鍵設(shè)備如下:

工藝環(huán)節(jié) | 核心設(shè)備 | 技術(shù)要求 |

UBM 制備 | 磁控濺射機 | 薄膜厚度均勻性 ±5%,臺階覆蓋率>80%(適應(yīng)芯片表面不平坦區(qū)域) |

光刻(電鍍法) | 步進光刻機 / 納米壓印設(shè)備 | 最小線寬<5μm(對應(yīng)凸點間距 10μm 以下),套刻精度 ±1μm |

電鍍 | 電鍍槽(含攪拌、溫控系統(tǒng)) | 電流密度均勻性 ±3%,避免凸點頂部 “尖化” 或 “凹陷” |

焊膏印刷 | 高精度絲網(wǎng)印刷機 | 鋼網(wǎng)開孔精度 ±2μm,焊膏轉(zhuǎn)移率>90% |

回流焊 | 熱風(fēng)回流爐 / 激光回流爐 | 溫度曲線控制精度 ±1℃(防止凸點氧化或芯片損傷),氮氣氛圍(氧含量<50ppm) |

檢測 | 3D 光學(xué)輪廓儀、X 射線檢測儀 | 可檢測凸點高度(±0.5μm)、直徑(±1μm)及內(nèi)部空洞(分辨率>5μm) |

四、Bump 技術(shù)的演變歷程

凸點技術(shù)的發(fā)展始終圍繞 “更小間距、更高密度、更低成本、更高可靠性” 展開,可分為4個階段:

1. 起步階段(1960s-1990s):金凸點主導(dǎo)

1960 年代,IBM首次提出倒裝芯片概念,采用蒸發(fā)法制備Au凸點,間距>200μm,主要用于大型計算機。特點:可靠性高但成本昂貴,凸點尺寸大(直徑50-100μm),I/O密度低(<1000個)。

2. 發(fā)展階段(1990s-2010s):錫基凸點與電鍍法普及

1990 年代,無鉛化趨勢推動SnPb(后轉(zhuǎn)向SnAgCu)凸點替代Au凸點,電鍍法逐漸成為主流,實現(xiàn)間距50-100μm。

2000 年代,手機、電腦等消費電子推動I/O密度提升,Cu核-Sn殼凸點出現(xiàn),平衡導(dǎo)電性與焊接性,間距縮小至30-50μm。

3. 精進階段(2010s-2020s):小間距與異構(gòu)集成

隨著移動終端和AI芯片對高密度互連的需求,凸點間距突破20μm,電鍍Cu凸點結(jié)合混合鍵合(Hybrid Bonding)技術(shù)出現(xiàn)(如臺積電CoWoS、英特爾 Foveros)。2015年后,HBM內(nèi)存堆疊推動凸點向“微凸塊(Micro Bump)” 演進,間距達10-15μm,單芯片I/O數(shù)量突破10萬。

4. 創(chuàng)新階段(2020s 至今):超小間距與鍵合融合

凸點間距進入10μm以下,部分場景開始用Cu-Cu直接鍵合替代傳統(tǒng)凸點(無需焊料),如三星X-Cube技術(shù)的混合鍵合,間距達1-5μm。核殼結(jié)構(gòu)凸點(如Cu-Sn、Cu-Ni-Sn)成為主流,兼顧高導(dǎo)電、低電阻和可靠性。

五、未來發(fā)展趨勢

1. 間距持續(xù)縮小,向“無凸點”演進

短期(2023-2027):凸點間距從當(dāng)前10μm縮小至5μm,依賴高精度電鍍和納米壓印光刻技術(shù)。

長期:Cu-Cu直接鍵合將逐步替代傳統(tǒng)凸點,實現(xiàn)1μm以下間距(如臺積電3D Fabric技術(shù)),信號傳輸延遲降低50%以上。

2. 材料與結(jié)構(gòu)創(chuàng)新

新型核殼結(jié)構(gòu):如Cu-Ag核殼(高導(dǎo)電+抗遷移)、Cu-SnBi(低溫焊接,適配異質(zhì)集成)。

自修復(fù)材料:在凸點中引入形狀記憶合金(如NiTi),通過熱循環(huán)自動修復(fù)微裂紋,提升汽車電子等場景的可靠性。

3. 工藝與設(shè)備升級

無光刻工藝:采用納米壓印、自組裝技術(shù)替代傳統(tǒng)光刻,降低小間距凸點的成本(預(yù)計成本下降 30%)。

原子層沉積(ALD):用于 UBM 的超薄阻擋層(厚度<10nm),抑制金屬擴散,提升長期可靠性。

4. 與3D集成深度融合

凸點將與 TSV(硅通孔)、RDL(重新布線層)協(xié)同,實現(xiàn)“芯片-芯片”、“芯片-基板”的立體互連,支撐存算一體、光電共封裝(CPO)等新興架構(gòu)。

凸點技術(shù)是倒裝芯片的“神經(jīng)末梢”,其從金凸點到Cu-Cu鍵合的演變,推動了芯片從平面互連向3D集成的跨越。未來,隨著間距縮小至亞微米級、材料與工藝的深度創(chuàng)新,凸點將成為支撐異構(gòu)集成、高帶寬芯片的核心技術(shù),在AI、5G、汽車電子等領(lǐng)域發(fā)揮關(guān)鍵作用。

-

錫膏

+關(guān)注

關(guān)注

1文章

993瀏覽量

18298 -

TSV

+關(guān)注

關(guān)注

4文章

137瀏覽量

82703 -

倒裝芯片

+關(guān)注

關(guān)注

1文章

120瀏覽量

16853 -

Flip Chip

+關(guān)注

關(guān)注

0文章

7瀏覽量

6508 -

UBM

+關(guān)注

關(guān)注

0文章

12瀏覽量

8298

發(fā)布評論請先 登錄

恒壓變壓器的發(fā)展史

5G的發(fā)展史

Bump Mapping有何功能

unix系統(tǒng)發(fā)展史

倒裝芯片,挑戰(zhàn)越來越大

晶圓級封裝(WLP)中Bump凸點工藝:4大實現(xiàn)方式的技術(shù)細節(jié)與場景適配

聊聊倒裝芯片凸點(Bump)制作的發(fā)展史

聊聊倒裝芯片凸點(Bump)制作的發(fā)展史

評論