本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3470

3470

microblaze和jtag-to-axi(jtag2axi)雖然也提供了訪問axi總線的能力,但是依賴于xilinx平臺。而uart-to-axi(uart2axi4)橋接器并不依賴任何平臺

2025-12-02 10:05:43 1846

1846

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內的控制寄存器進行通信。AXI-Lite允許構建簡單的元件接口。這個接口規模較小,對設計和驗證方面的要求更少

2020-09-27 11:33:02 9823

9823

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI4

2020-12-04 12:22:44 9055

9055

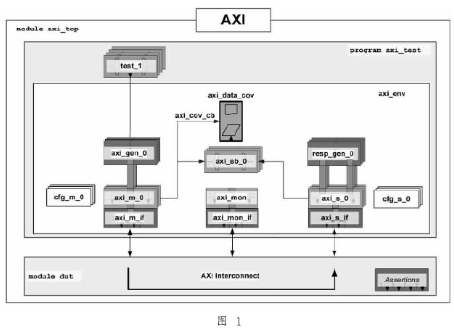

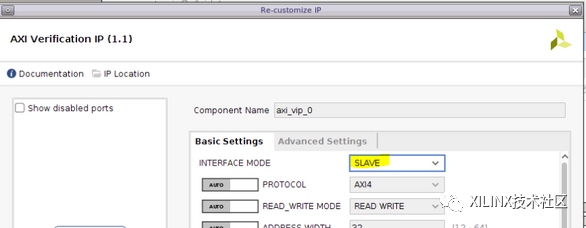

賽靈思 AXI Verification IP (AXI VIP) 是支持用戶對 AXI4 和 AXI4-Lite 進行仿真的 IP。它還可作為 AXI Protocol Checker 來使用。

2022-07-08 09:24:17 2976

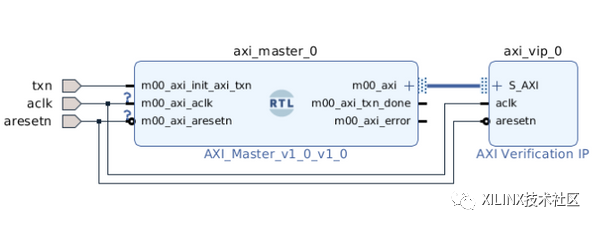

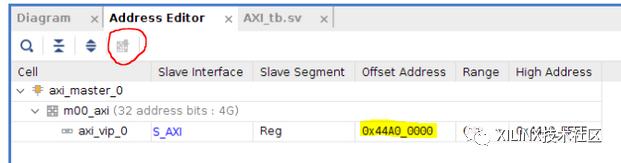

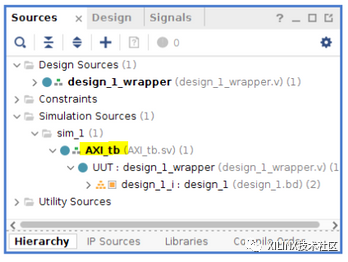

2976 在這篇新博文中,我們來聊一聊如何將 AXI VIP 添加到 Vivado 工程中,并對 AXI4-Lite 接口進行仿真。隨后,我們將在仿真波形窗口中講解用于AXI4-Lite 傳輸事務的信號。

2022-07-08 09:27:14 2742

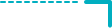

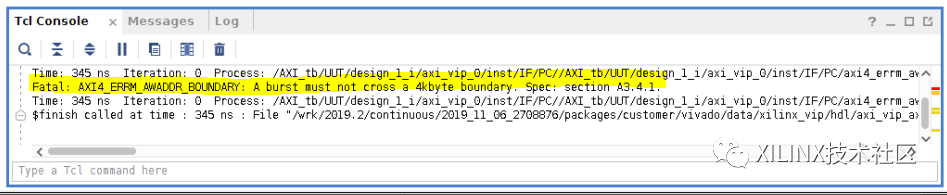

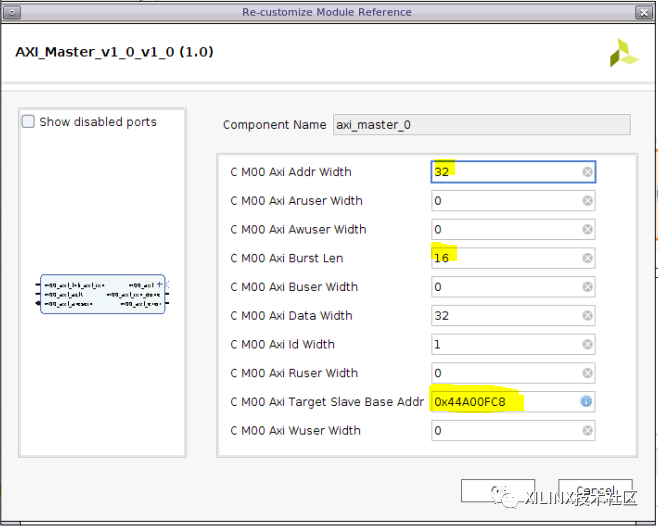

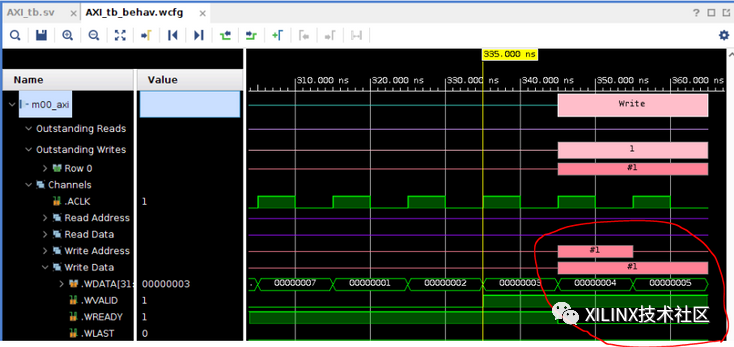

2742 首先對本次工程進行簡要說明:本次工程使用AXI-Full接口的IP進行DDR的讀寫測試。在我們的DDR讀寫IP中,我們把讀寫完成和讀寫錯誤信號關聯到PL端的LED上,用于指示DDR讀寫IP的讀寫運行

2022-07-18 09:53:49 7008

7008

MPSoC有六個PL側高性能(HP)AXI主接口連接到PS側的FPD(PL-FPD AXI Masters),可以訪問PS側的所有從設備。這些高帶寬的接口主要用于訪問DDR內存。有四個HP AXI

2022-07-22 09:25:24 4483

4483 ??AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下

2023-07-27 09:19:33 2206

2206

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測試源或者AXI外設的初始化配置接口。

2023-11-23 16:03:45 5162

5162

AXI接口FIFO是從Native接口FIFO派生而來的。AXI內存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應用外,AXI FIFO還可以用于AXI系統總線和點對點高速應用。

2025-03-17 10:31:11 1914

1914

AXI直接數值存取(Drect Memory Access,DMA)IP核在AXI4內存映射和AXI4流IP接口之間提供高帶寬的直接內存訪問。DMA可以選擇分散收集(Scatter Gather

2025-04-03 09:32:24 2246

2246

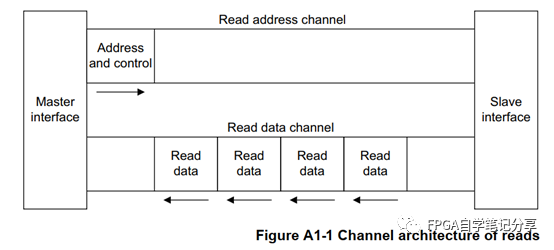

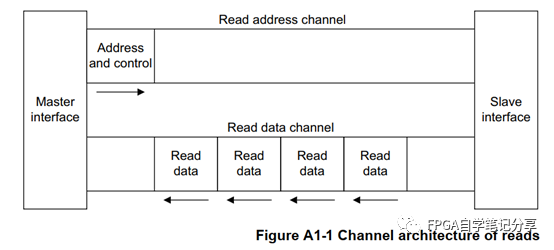

AXI4協議基于猝發式傳輸機制。在地址通道上,每個交易有地址和控制信息,這些信息描述了需要傳輸的數據性質。主從設備間的數據傳輸有兩種情況,一種是主設備經過寫通道向從設備寫數據(簡稱寫交易

2021-01-08 16:58:24

,那么它適應為每個活動從接口提供相等的加權”,以進行真正的循環仲裁。在我的例子中,我有4個從設備和1個主設備通過AXI4互連連接。考慮到SLAVE1正在向后發送數據并且沒有其他從設備正在發送數據的情況

2020-05-20 14:51:06

個恒定的6個32位字,所以必須注意幀數據或控制數據的緩沖區填滿的條件。防止無序狀況。“我還說在AXI4-Stream接口中“數據是以數據包的形式傳輸而不是連續流”。最大9Kb“幀”大小是否也適用于通過AXI4-Stream接口發送的最大“數據包大小”?問候。

2020-05-25 09:37:36

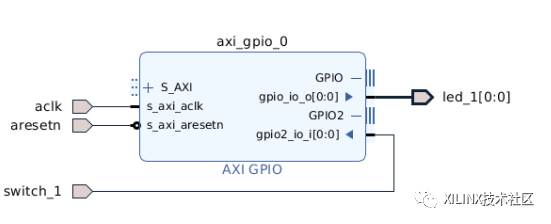

,將GPIO引腳設置為輸出模式,并循環控制GPIO引腳輸出高低電平。每次輸出后,延時一會,以便觀察輸出結果。最后返回0,表示程序執行成功。

注意事項

需要在e203_subsys_mems.v文件找到AXI4的地址

2025-10-22 08:14:59

AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據突發傳輸規模

2021-01-08 16:52:32

AXI 總線上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協議。其中三種AXI總線分別為:AXI4

2022-04-08 10:45:31

分別為: AXI4:(For high-performance memory-mappedrequirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據

2022-10-14 15:31:40

AXI有哪些性能?AXI的特點是什么?AXI4有哪些工作模式?

2021-06-23 08:13:52

;arready),若沒有新的指令到來,那么readCmd.addr需保持不變,否則pendingels及pendingError將會變化可能導致讀數據通道的譯碼錯誤。而在Axi4 Spec里并無此要求。有了上面

2022-08-04 14:28:56

您可以將協議斷言與任何旨在實現AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協議通過一系列斷言根據協議檢查測試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

XHB將AXI4協議轉換為AHB-Lite協議,并具有AXI4從接口和AHB-Lite主接口。有關AXI4事務如何通過XHB橋接到AHB-Lite的信息,請參閱第2-2頁的表2-1

2023-08-02 06:51:45

針對不同的應用場景,制定了三個不同類型的接口,其中包括AXI4-Full、AXI4-Lite以及AXI4-Stream。表1為三種AXI4總線的對比。

表1三種AXI4總線對比

總線名稱

2025-06-02 23:05:19

高性能、高帶寬、低延時的片內互連需求。AXI4總線則是AXI總線的第四代版本,主要包含三種類型的接口,分別是面向高性能地址映射通信的AXI4接口、面向輕量級單次地址映射通信的AXI4-Lite接口和面

2025-05-17 10:27:56

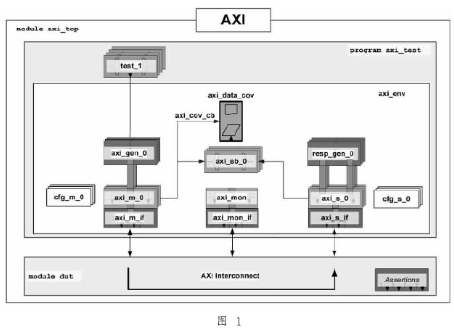

子系統模型組成。UVM驗證包用于構建測試用例、提供激勵、監測接口、對比分析統計測試結果;DUT 為待測試對象即 NoP 邏輯加速引擎;AXI BRAM IP 用于模擬外部存儲,對接 DUT 的AXI4

2025-07-31 16:39:09

子系統模型組成。UVM驗證包用于構建測試用例、提供激勵、監測接口、對比分析統計測試結果;DUT 為待測試對象即 NoP 邏輯加速引擎;AXI BRAM IP 用于模擬外部存儲,對接 DUT 的AXI4

2025-08-26 09:49:46

和計分板; 序列發生器根據測試用例產生事務。

Axi4_agent 負責監測 AXI4 總線接口。 由于 AXI4 總線接口用于進行數據傳輸,在驗證平臺中該總線接口實際與 AXI BRAM IP 對接

2025-08-29 14:33:19

的fifo接口),用戶只要操作fifo接口,無需關心PCIE的內部驅動。為了便于讀者更加明白,可以深入了解PCIE,我們將會制作一個PCIE的連載系列。今天,首先說一下自定義AXI4的IP核,至于AXI4

2019-12-13 17:10:42

,分別為:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也稱為 AXI4-Full 是一種基于地址的高性能傳輸接口,其支持亂序傳輸、突發傳輸等傳輸方式,同時通過獨立

2025-06-24 18:00:11

? 這里以功能完備的 AXI4 接口舉例說明 AXI4 總線的相關特點。AXI4 總線采用讀寫通道分離且數據通道與控制通道分離的方式,這樣的總線通道使其具有多主多從的連接特性和并行處理的能力,能夠

2025-06-24 18:02:23

這是SoC Designer AXI4協議包的用戶指南。該協議包包含SoC Designer組件、探針和ARM AXI4協議的事務端口接口(包括對AMBA4 AXI的支持)。

2023-08-10 06:30:18

或起點嗎?此外,我的VHDL模塊具有AXI4流接口,而其他模塊具有自定義接口。如何使它們兼容?將等待有用的回復。問候

2020-05-22 09:24:26

你好,我有一個關于XADC及其AXI4Lite接口輸入的問題。我想在Microzed 7020主板上測試XADC,在通過AXI4Lite接口將Zynq PL連接到XADC向導(參見第一個附件)之后

2018-11-01 16:07:36

,具備獨立的數據寫入和讀取AXI4接口,不但適用高性能、順序訪問的應用,也適用于隨機訪問的應用,同時結合外部存儲器(比如DDR),使得Host端的數據訪問管理更加靈活。NVMe是基于PCIe之上的協議

2025-11-14 22:40:50

Vivado中實現一個AXI4接口的IP核,用于對DDR3進行讀寫測試。本章包括以下幾個部分:99.1簡介9.2實驗任務9.3硬件設計9.4軟件設計9.5下載驗證9.1簡介我們在前面的實驗中介紹了一些

2020-10-22 15:16:34

原子公眾號,獲取最新資料第十五章AXI4接口之DDR讀寫實驗Xilinx從Spartan-6和Virtex-6系列開始使用AXI協議來連接IP核。在7系列和ZYNQ-7000 AP SoC器件中

2020-09-04 11:10:32

問候,因此,我在創建IP外設并在VIVADO中使用ZYBO板單擊“使用AXI4 BFM仿真接口驗證外設IP”選項時收到此錯誤消息。我只想看到AXI接口的模擬我甚至沒有它的邏輯,我創建了一個虛擬項目

2019-04-12 15:17:23

你好,我正在EDK中使用axi4stream。有人可以幫助我如何使用通過Vivado高級綜合(HLS)生成的ap_fifo / axi4stream接口可以在EDK中使用嗎?我正在使用Export

2019-02-28 13:47:30

嗨,大家好,我目前正在創建一個PCIe接口卡,我正處于項目的調試階段。我試圖監視用戶_clkrate的AXI突發。關于ILA核心和PCIe端點(在VC709上)我有一些問題。1.當我嘗試將

2019-09-25 09:26:14

使用Vivado生成AXI VIP(AXI Verification IP)來對自己設計的AXI接口模塊進行全方位的驗證(如使用VIP的Master、Passthrough、Slave三種模式對自己寫的AXI

2022-10-09 16:08:45

多選一的抉擇相較于Axi4寫通路,多通路的多選一就容易多了。對于Axi4ReadOnlyArbiter,其僅需處理兩個問題:Ar通路多端口仲裁,其處理和寫通路aw通路基本相同,采用多端口RR調度即可

2022-08-08 14:32:20

大家好,我正在使用zedboard創建一個AXI接口應用程序,以突發模式從ARM發送64字節數據到FPGA。為此,我在vivado中創建了一個自定義AXI從站,選擇它作為AXI FULL(因為AXI

2020-08-12 10:37:46

元素(如混合端序結構)的支持。

本文檔重點介紹AXI4中定義的AXI的關鍵概念,并強調了差異

適用時,適用于AXI3。AXI5擴展了AXI4,并引入了一些性能和Arm

架構特征。此處描述的關鍵概念仍然適用,但

AXI5在此未涵蓋

2023-08-09 07:37:45

大家好。我目前正在使用GTH收發器實現更復雜的設計,這些收發器工作在2.8 GHz(5.6GB),我想知道我是否可以使用AXI4流以某種方式從收發器中提取輸入數據。有沒有辦法將數據寫入內存并

2019-05-05 13:14:10

你好是否可以使用帶有AXI4接口的邏輯核心ip reed solomon編碼器版本9。問候Rose Varghese

2020-05-20 15:44:58

讀寫分離的設計在Axi4總線中,讀和寫通道是完全相互獨立,互不干擾。故而無論是在設計Decoder還是Arbiter時,均可以采用讀寫分離的方式。如前文所述,SpinalHDL在基于Axi4總線

2022-08-03 14:27:09

,ar)共用一組信號的接口(arw,w,b,r)。關于總線互聯的設計凡是設計中用到Axi4總線的設計總離不開總線互聯。在Xilinx FPGA使用中,VIvado針對Axi4總線提供了豐富的IP,對于

2022-08-02 14:28:46

microblaze通過串口讀寫FPGA內部axi4總線上的寄存器

2020-12-23 06:16:11

和低功耗接口。AXI頻道AXI主站和從站之間有五個獨立的通道。它們是: 讀取地址通道讀取數據通道寫地址通道寫數據通道寫響應通道地址通道用于在執行主從之間的基本握手時發送地址和控制信息。數據通道是要交換信息

2020-09-28 10:14:14

: AXI4-Stream—使用DMA時,從Zynq SoC的XDAC流式接口到內存映射,提供高性能輸出 AXI4-Lite —配置和控制XADC以及DMA控制器 AXI4 —配置

2017-02-08 08:10:39 527

527 Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個IP的作用。 下面看一下這個IP 的接口: 所以要把標準的VESA信號 轉為

2017-02-08 08:36:19 887

887

本文包含兩部分內容:1)AXI接口簡介;2)AXI IP核的創建流程及讀寫邏輯分析。 1AXI簡介(本部分內容參考官網資料翻譯) 自定義IP核是Zynq學習與開發中的難點,AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

了解如何使用Xilinx AXI驗證IP有效驗證和調試AXI接口。

該視頻回顧了使用的好處,以及如何使用示例設計進行模擬。

2018-11-20 06:38:00 4660

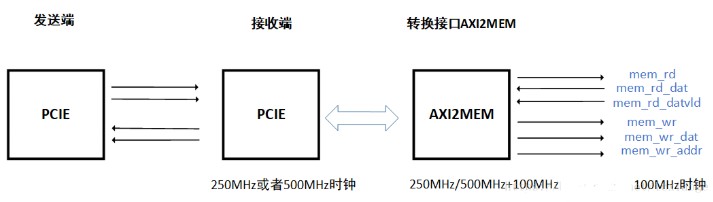

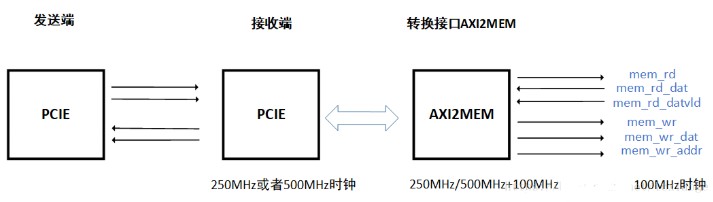

4660 AXI2MEM轉換接口需要將來自PCIE的AXI信號(時鐘為250MHz或者500MHz)轉換成100MHz時鐘的MEM接口。MEM接口用于SOC總線主端口,用于讀寫芯片內部模塊或者配置寄存器。

2019-05-12 09:19:31 2755

2755

這將創建一個附帶 BD 的 Vivado 工程,此 BD 包含 AXI VIP (設置為 AXI4-Lite 主接口) 和 AXI GPIO IP。這與我們在 AXI 基礎第 3 講一文 中完成的最終設計十分相似。

2020-04-30 16:24:50 3097

3097

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,從下面的示例圖中就可見一斑。最直接的體現是AXI-4 Lite的突發長度是固定值1。

2020-09-23 11:18:06 4269

4269

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協議的基礎,其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個通道構成,如下圖所示:寫地址通道、寫數據通道、寫響應通道、讀地址通道和讀數據通道。

2020-09-23 11:20:23 6924

6924

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI-Lite或

2020-09-24 09:50:30 7203

7203

在FPGA程序設計的很多情形都會使用到AXI接口總線,以PCIe的XDMA應用為例,XDMA有兩個AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過

2020-10-30 12:32:37 5118

5118

新的賽靈思器件設計中不可或缺的一部分。充分了解其基礎知識對于賽靈思器件的設計和調試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關基礎知識。首先,我們將從一些通俗易懂的知識、理論

2020-09-27 11:06:45 7722

7722

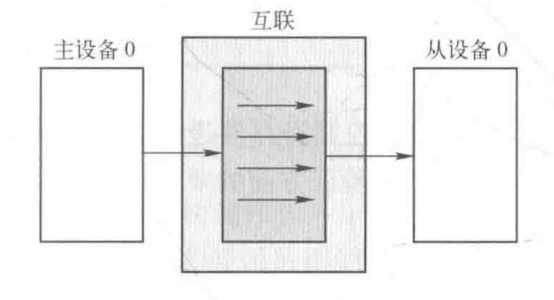

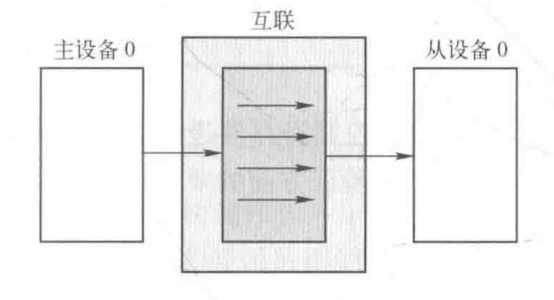

連接。在這種模式下,沒有延遲,同時不消耗邏輯資源。 2. 只轉換模式 當連接一個主設備和一個從設備時,AXI互聯執行不同的轉換和流水線功能:數據位寬轉換、時鐘速率轉換、AXI-Lite從適應、AXI-3從適應、流水線。在只轉換模式下,AXI互聯不包含仲裁、解碼或布

2020-11-16 17:39:24 4213

4213

和低功耗接口。AXI頻道AXI主站和從站之間有五個獨立的通道。它們是:讀取地址通道讀取數據通道寫地址通道寫數據通道寫響應通道地址通道用于在執行主從之間的基本握手時發送地址和控制信息。數據通道是要交換信息

2020-09-29 11:44:22 7591

7591

和接口的構架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過

2020-11-02 11:27:51 5033

5033

AXI-Stream代碼詳解 AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據

2020-11-05 17:40:36 4706

4706

本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 ,它使用通用的AXI4接口在系統中移動或轉換數據,而不解釋數據。 這些基礎的IP各自有自己的常用的功能,下面列舉出一部分AXI接口的基礎構架IP。 ° AXI Register slices

2021-05-11 14:52:55 7870

7870

本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的區別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時。由于AXI4-Stream協議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒有時序圖,

2022-06-23 10:08:47 3052

3052 學習關于ZYNQ IP核中的GP接口和HP接口的異同,介紹關于AXI_GP接口和AXI_HP接口的相關內容。

2022-07-03 14:17:34 4898

4898 本文主要介紹關于AXI4-Stream Video 協議和AXI_VDMA的IP核相關內容。為后文完成使用帶有HDMI接口的顯示器構建圖像視頻顯示的測試工程做準備。

2022-07-03 16:11:05 10566

10566 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數據流。從字面意思去理解

2022-07-04 09:40:14 10523

10523 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2022-08-29 14:58:44 2981

2981 使用Vivado生成AXI VIP(AXI Verification IP)來對自己設計的AXI接口模塊進行全方位的驗證(如使用VIP的Master、Passthrough、Slave三種模式對自己寫的AXI

2022-10-08 16:07:11 7395

7395 Xilinx vivado下通常的視頻流設計,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 7574

7574 上面兩圖的區別是相比AXI3,AXI4協議需要確認AWVALID、AWREADY握手完成才能回復BVALID。為什么呢?

2023-03-30 09:59:49 1852

1852 AXI4 協議定義了五個不同的通道,如 AXI 通道中所述。所有這些通道共享基于 VALID 和 READY 信號的相同握手機制

2023-05-08 11:37:50 2040

2040

AMBA AXI協議支持高性能、高頻系統設計。

2023-05-24 15:05:12 1916

1916

上文FPGA IP之AXI4協議1_協議構架對協議框架進行了說明,本文對AXI4接口的信號進行說明。

2023-05-24 15:05:46 2767

2767

上文FPGA IP之AXI4協議1_信號說明把AXI協議5個通道的接口信息做了說明,本文對上文說的信號進行詳細說明。

2023-05-24 15:06:41 2083

2083

ACLK,ARESETn,AXI所有信號都在時鐘的上升沿采樣.

2023-06-07 15:24:12 4012

4012

AXI4協議是ARM的AMBA總線協議重要部分,ARM介紹AXI4總線協議是一種性能高,帶寬高,延遲低的總線協議。

2023-06-19 11:17:42 5678

5678

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 3091

3091

AXI4協議是一個點對點的主從接口協議,數據可以同時在主機(Master)和從機(Slave)之間**雙向** **傳輸** ,且數據傳輸大小可以不同。

2023-06-21 15:26:43 4254

4254

AXI4:高性能內存映射需求(如讀寫DDR、使用BRAM控制器讀寫BRAM等),為了區別,有時候也叫這個為 AXI4-Full;

2023-06-25 16:23:14 2574

2574

?AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下AXI VIP當作master時如何使用。

2023-07-27 09:16:13 3103

3103

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

本文主要集中在AMBA協議中的AXI4協議。之所以選擇AXI4作為講解,是因為這個協議在SoC、IC設計中應用比較廣泛。

2024-01-17 12:21:22 4273

4273

Transaction layer的所有功能特性,不僅內置DMA控制器,而且具備AXI4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時適用于ASIC和FPGA。

2024-02-22 09:15:46 3

3 AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協處理器接口(AXI4-Lite)、AXI主外設接口(AXI4)、AXI外設到主處理器接口(AXI4-Lite)等。

2024-04-18 11:41:39 2500

2500 AXI4和AXI3是高級擴展接口(Advanced eXtensible Interface)的兩個不同版本,它們都是用于SoC(System on Chip)設計中的總線協議,用于處理器和其它外設之間的高速數據傳輸。

2024-05-10 11:29:50 13098

13098

NVMe AXI4 Host Controller IP可以連接高速存儲PCIe SSD,無需CPU,自動加速處理所有的NVMe協議命令,具備獨立的數據寫入和讀取AXI4接口,不但適用高性能、順序

2024-07-18 09:17:19 1441

1441

AMBA AXI4(高級可擴展接口 4)是 ARM 推出的第四代 AMBA 接口規范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導體產業首個符合 AXI4 標準的即插即用型 IP 進一步擴展了 AMD 平臺設計方法。

2024-10-28 10:46:42 1383

1383

AXI4 總線是第四代 AXI 總線,其定義了三種總線接口,分別為:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也稱為 AXI4-Full 是一種基于地址的高性能

2025-06-24 23:22:33 523

523

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務,而 PCIe 接口信號可被

2025-08-04 16:52:09 677

677

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務,而 PCIe 接口信號可被

2025-08-25 18:53:01 2817

2817

電子發燒友App

電子發燒友App

評論