在FPGA程序設計的很多情形都會使用到AXI接口總線,以PCIe的XDMA應用為例,XDMA有兩個AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過M_AXI接口對數據進行讀取操作,此時設計一個基于AXI-Slave接口的IP進行數據傳輸操作就非常的方便。

封裝的形式并不復雜,只是略微繁瑣,接下來一步一步演示如何封裝AXI_SLAVE接口IP:

1、創建工程

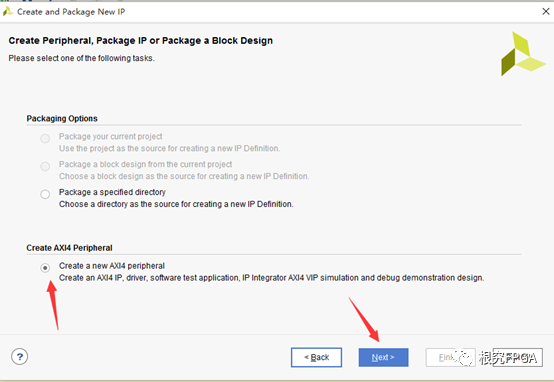

2、選擇Create AXI4 Perpheral,點擊next

設置保存路徑,也可默認:

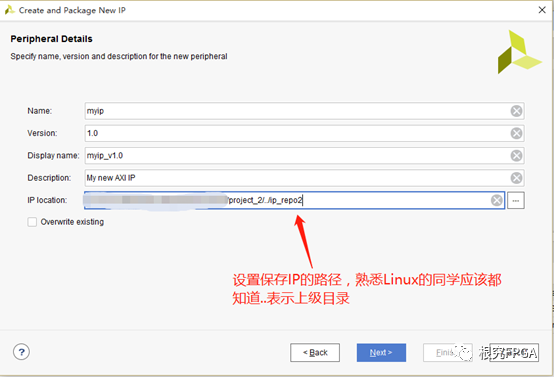

3、設置保存路徑:

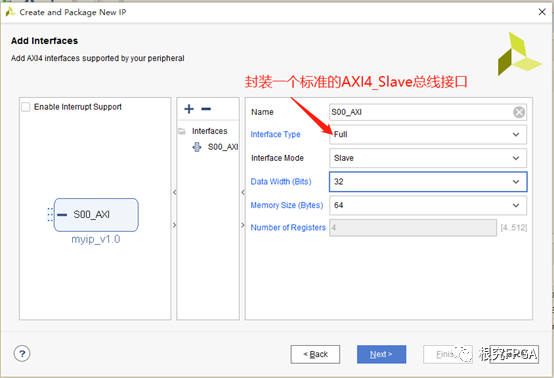

4、設置封裝的接口類型:

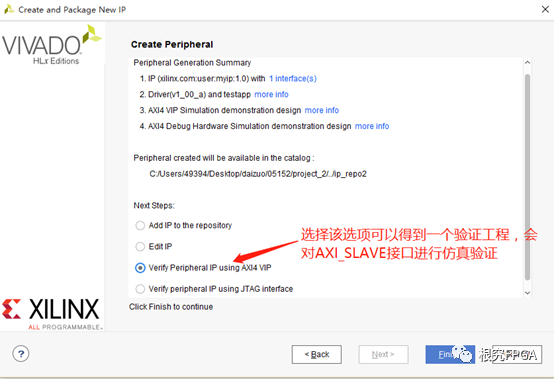

5、選擇Verify Peripheral IP using AXI4 IP

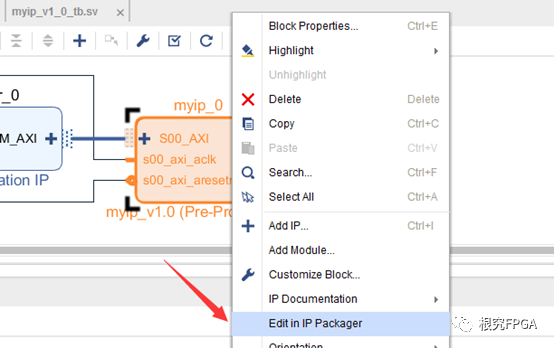

6、對IP進行修改:

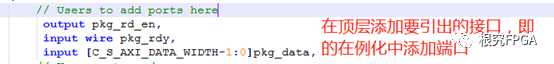

在S00_AXI.v中編輯:

7、保存工程

如果不慎將初始的IP封裝界面關掉的話,在Tools下選擇Create and Package New IP,選擇Package your current project,NEXT之后選擇open(你會看到的)。

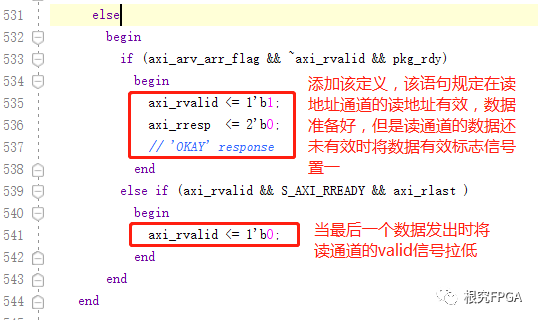

設置ID位寬,該選項主要用于outstanding傳輸:

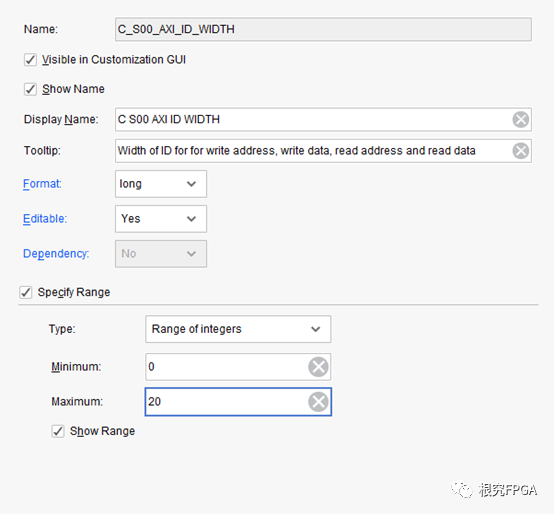

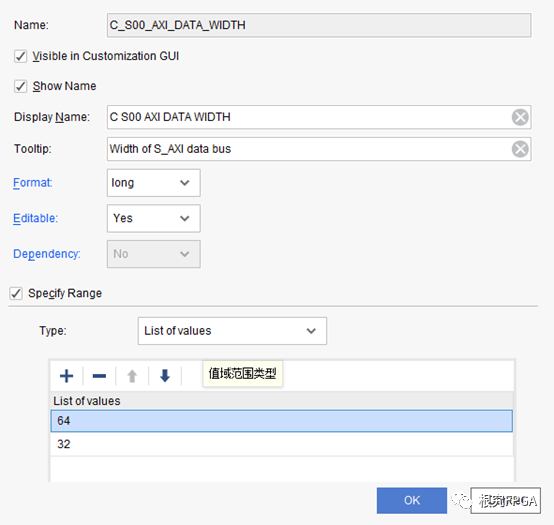

設置數據位寬,根據需要自行設計:

如果出現Merge提示的話,點擊,選擇覆蓋參數。

最后選擇重新封裝IP,就得到屬于自己的AXI_SLAVE接口IP啦!

在剛剛設置的ip_repo2文件目錄下可以看到IP:

編輯:hfy

-

FPGA

+關注

關注

1663文章

22483瀏覽量

638583 -

AXI

+關注

關注

1文章

145瀏覽量

18003

發布評論請先 登錄

利用開源uart2axi4實現串口訪問axi總線

RDMA設計6:IP架構2

Xilinx高性能NVMe Host控制器IP+PCIe 3.0軟核控制器IP,純邏輯實現,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

NVMe高速傳輸之擺脫XDMA設計43:如何上板驗證?

將e203 例化AXI總線接口

VDMA IP核簡介

AXI GPIO擴展e203 IO口簡介

RDMA over RoCE V2設計2:ip 整體框架設計考慮

NVMe IP之AXI4總線分析

NVMe控制器IP設計之接口轉換

智多晶eSPI_Slave IP介紹

FPGA程序設計:如何封裝AXI_SLAVE接口IP

FPGA程序設計:如何封裝AXI_SLAVE接口IP

評論