AXI 總線是一種高速片內(nèi)互連總線,其定義于由 ARM 公司推出的 AMBA 協(xié)議中,主要用于高性能、高帶寬、低延遲、易集成的片內(nèi)互連需求。AXI4 總線是第四代 AXI 總線,其定義了三種總線接口,分別為:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也稱為 AXI4-Full 是一種基于地址的高性能傳輸接口,其支持亂序傳輸、突發(fā)傳輸?shù)葌鬏敺绞剑瑫r通過獨立的地址總線,實現(xiàn)高性能的數(shù)據(jù)地址映射;

AXI4-Lite 則在 AXI4 的基礎(chǔ)上去掉了亂序傳輸、突發(fā)傳輸、Outstanding 等特性,主要用于簡單的單次地址映射通信。而 AXI4-Stream 則為點對點連接總線,其去掉了地址總線,主要用于點對點間的高速數(shù)據(jù)流傳輸。三種接口的對比如表 1 所示:

表1 AXI4、AXI4-Lite 和 AXI4-Stream接口總線

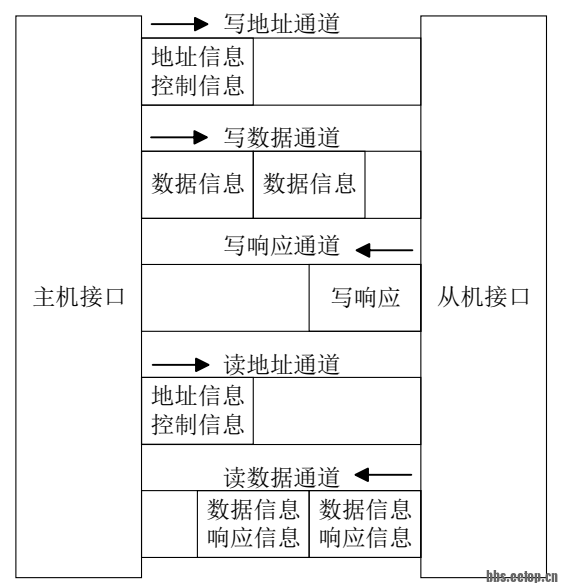

? 這里以功能完備的 AXI4 接口舉例說明 AXI4 總線的相關(guān)特點。AXI4 總線采用讀寫通道分離且數(shù)據(jù)通道與控制通道分離的方式,這樣的總線通道使其具有多主多從的連接特性和并行處理的能力,能夠大幅提高總線的數(shù)據(jù)吞吐量。AXI4 總線共有五個通道。其中,寫地址通道和寫數(shù)據(jù)通道數(shù)據(jù)流由主機指向從機,分別用于發(fā)送地址信息和數(shù)據(jù)信息。寫響應(yīng)通道數(shù)據(jù)流由從機指向主機,用于反饋寫指令的完成狀態(tài)。

讀通道與寫通道類似,讀地址通道由主機指向從機,用于發(fā)送地址信息和控制信息,讀數(shù)據(jù)通道數(shù)據(jù)流由從機指向主機,用于從發(fā)送數(shù)據(jù)信息。但與寫通道不同的是,讀通道并沒有響應(yīng)通道,讀響應(yīng)信息包含在讀數(shù)據(jù)通道中,與數(shù)據(jù)流一同反饋給主機。AXI4 總線的通道結(jié)構(gòu)如圖 1所示。

圖1 AXI4 總線的通道結(jié)構(gòu)圖

?

相關(guān)視頻感興趣者,請搜B站用戶名: 專注與守望

或鏈接:

https://space.bilibili.com/585132944/upload/video

?審核編輯 黃宇

-

RDMA

+關(guān)注

關(guān)注

0文章

99瀏覽量

9649 -

AXI

+關(guān)注

關(guān)注

1文章

145瀏覽量

17985

發(fā)布評論請先 登錄

RDMA設(shè)計36:驗證環(huán)境設(shè)計

RDMA設(shè)計35:基于 SV 的驗證平臺

Xilinx高性能低延時8通道PCIe-DMA控制器IP,SGDMA,QDMA,CDMA,RDMA, V4L2驅(qū)動,高速視頻采集, 高速AD采集

RDMA設(shè)計5:RoCE V2 IP架構(gòu)

RDMA設(shè)計4:技術(shù)需求分析2

RDMA設(shè)計2:開發(fā)必要性之性能簡介

RDMA設(shè)計1:開發(fā)必要性1之設(shè)計考慮

RDMA簡介9之AXI 總線協(xié)議分析2

RDMA簡介8之AXI 總線協(xié)議分析1

RDMA簡介4之ROcE V2初析

RDMA簡介3之四種子協(xié)議對比

RDMA簡介2之A技術(shù)優(yōu)勢分析

RDMA簡介1之RDMA開發(fā)必要性

NVMe簡介之AXI總線

RDMA簡介8之AXI分析

RDMA簡介8之AXI分析

評論