本文將使用 Clocking Wizard 文檔 PG321 中的“通過(guò) AXI4-Lite 進(jìn)行動(dòng)態(tài)重配置的示例”章節(jié)作為參考。

2025-05-27 10:42:03 1046

1046

,可以實(shí)現(xiàn)跨fpga平臺(tái)使用。利用uart2axi4我們可以通過(guò)python,輕松訪問(wèn)axi4_lite_slave寄存器,大大方便fpga工程師進(jìn)行系統(tǒng)調(diào)試和定位bug。

2025-12-02 10:05:43 1846

1846

本小節(jié)通過(guò)使用XPS中的定制IP向?qū)?ipwiz),為已經(jīng)存在的ARM PS 系統(tǒng)添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結(jié)構(gòu),并掌握AXI Lite IP的定制方法,為后續(xù)編寫復(fù)雜AXI IP打下基礎(chǔ)。同時(shí)本小

2012-12-23 15:39:12 19162

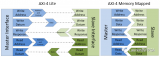

19162 映射通信的需求,是面向地址映射的接口,允許最大256輪的數(shù)據(jù)突發(fā)傳輸; AXI4-Lite:(For simple, low-throughput memory-mapped communication

2018-01-09 14:10:42 9365

9365

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內(nèi)的控制寄存器進(jìn)行通信。AXI-Lite允許構(gòu)建簡(jiǎn)單的元件接口。這個(gè)接口規(guī)模較小,對(duì)設(shè)計(jì)和驗(yàn)證方面的要求更少

2020-09-27 11:33:02 9823

9823

,是面向地址映射的接口,允許最大256輪的數(shù)據(jù)突發(fā)傳輸; (B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個(gè)輕量級(jí)的地址映射單次傳輸接口,占用很少的邏輯單元。 (C)AXI4-Stream:(F

2020-12-04 12:22:44 9055

9055

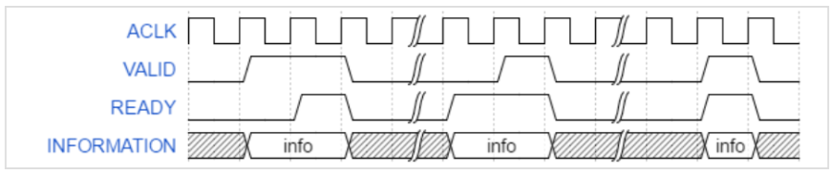

前面一節(jié)我們學(xué)會(huì)了創(chuàng)建基于AXI總線的IP,但是對(duì)于AXI協(xié)議各信號(hào)的時(shí)序還不太了解。這個(gè)實(shí)驗(yàn)就是通過(guò)SDK和Vivado聯(lián)合調(diào)試觀察AXI總線的信號(hào)。由于我們創(chuàng)建的接口是基于AXI_Lite協(xié)議

2020-12-23 15:32:37 3253

3253 賽靈思 AXI Verification IP (AXI VIP) 是支持用戶對(duì) AXI4 和 AXI4-Lite 進(jìn)行仿真的 IP。它還可作為 AXI Protocol Checker 來(lái)使用。

2022-07-08 09:24:17 2976

2976 在這篇新博文中,我們來(lái)聊一聊如何將 AXI VIP 添加到 Vivado 工程中,并對(duì) AXI4-Lite 接口進(jìn)行仿真。隨后,我們將在仿真波形窗口中講解用于AXI4-Lite 傳輸事務(wù)的信號(hào)。

2022-07-08 09:27:14 2742

2742 在 AXI 基礎(chǔ)第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協(xié)議檢查工具。在本次第4講中,我們將來(lái)了解下如何使用它在 AXI4 (Full) 主接口中執(zhí)行驗(yàn)證(和查找錯(cuò)誤)。

2022-07-08 09:31:38 4371

4371 在某些情況下,通過(guò)嗅探 AXI 接口來(lái)分析其中正在發(fā)生的傳輸事務(wù)是很有用的。在本文中,我將為大家演示如何創(chuàng)建基本 AXI4-Lite Sniffer IP 以對(duì)特定地址上正在發(fā)生的讀寫傳輸事務(wù)進(jìn)行計(jì)數(shù)。

2022-07-08 09:35:34 1394

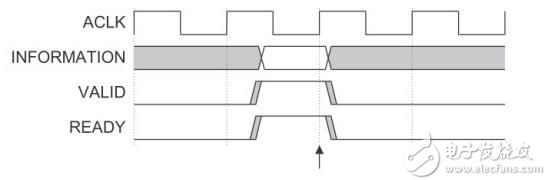

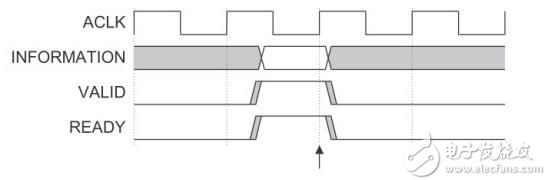

1394 由于ZYNQ架構(gòu)和常用接口IP核經(jīng)常出現(xiàn) AXI協(xié)議,賽靈思的協(xié)議手冊(cè)講解時(shí)序比較分散。所以筆者收藏AXI協(xié)議的幾種時(shí)序,方便編程。

2022-08-02 12:42:17 9566

9566 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統(tǒng)外設(shè)上生成特定序列(流量)。它根據(jù)IP的編程和選擇的操作模式生成各種類型的AXI事務(wù)。是一個(gè)比較好用的AXI4協(xié)議測(cè)試源或者AXI外設(shè)的初始化配置接口。

2023-11-23 16:03:45 5162

5162

AXI接口FIFO是從Native接口FIFO派生而來(lái)的。AXI內(nèi)存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應(yīng)用外,AXI FIFO還可以用于AXI系統(tǒng)總線和點(diǎn)對(duì)點(diǎn)高速應(yīng)用。

2025-03-17 10:31:11 1914

1914

,SG)功能還可以將數(shù)據(jù)移動(dòng)任務(wù)從位于于處理器系統(tǒng)中的中央處理器(CPU)中卸載出來(lái)。可以通過(guò)一個(gè)AXI4-Lite從接口訪問(wèn)初始化、狀態(tài)和管理寄存器。如圖4. 8展現(xiàn)了DMA IP的功能構(gòu)成核心。

2025-04-03 09:32:24 2246

2246

我必須通過(guò)AXI4-lite接口配置Jesd204b核心,或者我可以簡(jiǎn)單地將AXI4-lite端口保持未連接狀態(tài)(強(qiáng)制接地)?Jesd204核心示例top沒(méi)有提供有關(guān)AXI4-Lite端口配置的指導(dǎo)。

2020-05-15 09:30:54

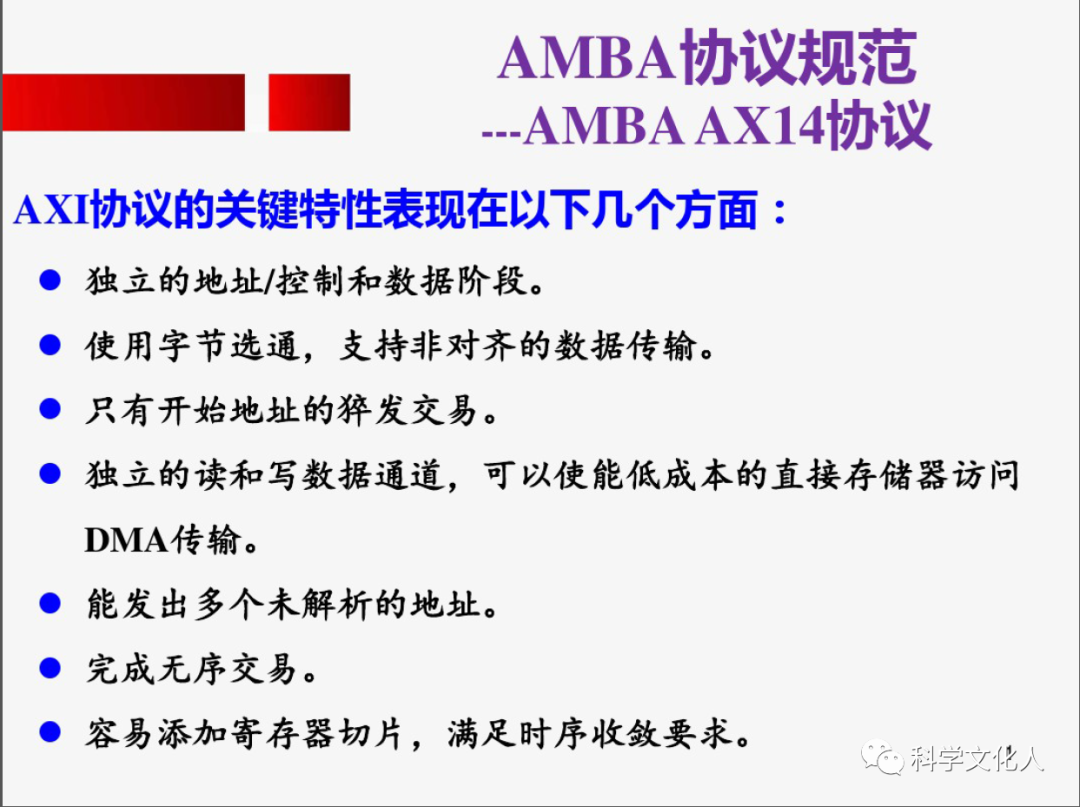

不可能說(shuō)是撇開(kāi)總線單講協(xié)議,因?yàn)?b class="flag-6" style="color: red">協(xié)議的制定也是要建立在總線構(gòu)成之上的。雖然說(shuō)AXI4, AXI4-Lite, AXI4-Stream都是AXI4協(xié)議,但是各自細(xì)節(jié)上還是不同的。總的來(lái)說(shuō), AXI總線協(xié)議

2022-04-08 10:45:31

突發(fā)傳輸; AXI4-Lite:(For simple, low-throughput memory-mapped communication)是一個(gè)輕量級(jí)的地址映射單次傳輸接口,占用很少的邏輯單元

2022-10-14 15:31:40

提示:文章寫完后,目錄可以自動(dòng)生成,如何生成可參考右邊的幫助文檔目錄一、總覽二、實(shí)戰(zhàn)效果1.PL 寫數(shù)據(jù)給PS效果2.PS寫數(shù)據(jù)給PL效果總結(jié)前言沒(méi)看過(guò)上一篇的去看一下上一章節(jié)對(duì)AXI_Lite在

2022-01-10 08:00:55

框圖。這個(gè)看起來(lái)好像不是很復(fù)雜,下面咱們一起來(lái)學(xué)習(xí)學(xué)習(xí)這個(gè)ip。在這里我還沒(méi)搞明白sda和scl的_t,_o是什么意思,后面慢慢了解。接著手冊(cè)講解了這幾個(gè)模塊的作用到這里,我大概理解一下,axi_lite接口接收到主機(jī)發(fā)送過(guò)來(lái)的指令,將指令寫到寄存器去,寄存器接收到控制信號(hào)后,將控制命令發(fā)送給Dyn

2022-01-18 07:00:13

本指南介紹了高級(jí)微控制器總線體系結(jié)構(gòu)(AMBA)AXI的主要功能。

該指南解釋了幫助您實(shí)現(xiàn)AXI協(xié)議的關(guān)鍵概念和細(xì)節(jié)。

在本指南中,我們介紹:

?AMBA是什么。

?為什么AMBA在現(xiàn)代SoC設(shè)計(jì)中

2023-08-09 07:37:45

您可以將協(xié)議斷言與任何旨在實(shí)現(xiàn)AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協(xié)議通過(guò)一系列斷言根據(jù)協(xié)議檢查測(cè)試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

本書(shū)是為系統(tǒng)設(shè)計(jì)者、系統(tǒng)集成商和驗(yàn)證工程師編寫的,他們希望確認(rèn)設(shè)計(jì)符合相關(guān)AMBA4協(xié)議。這可以是ACE或ACE Lite

2023-08-10 07:01:12

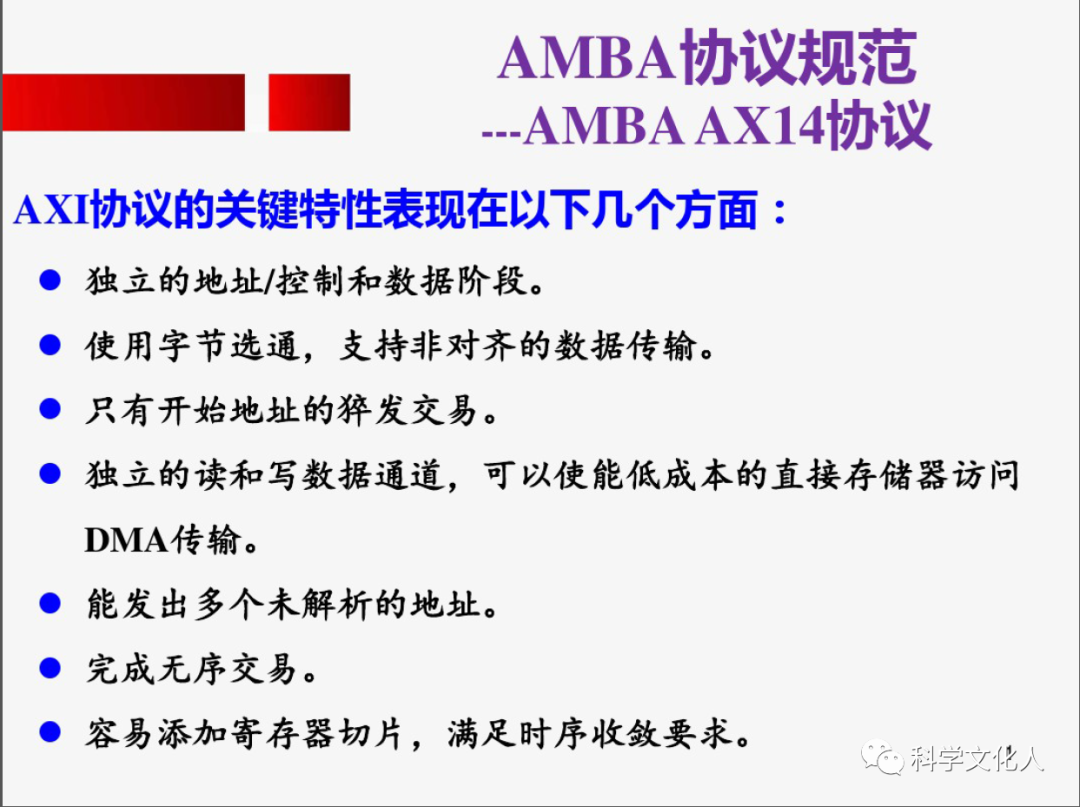

AXI協(xié)議支持高性能、高頻的系統(tǒng)設(shè)計(jì),用于

管理器和下屬組件。

AXI協(xié)議的特點(diǎn)是:

?適用于高帶寬和低延遲設(shè)計(jì)。

?在不使用復(fù)雜橋梁的情況下提供高頻操作。

?該協(xié)議滿足各種組件的接口要求

2023-08-02 09:44:08

XHB將AXI4協(xié)議轉(zhuǎn)換為AHB-Lite協(xié)議,并具有AXI4從接口和AHB-Lite主接口。有關(guān)AXI4事務(wù)如何通過(guò)XHB橋接到AHB-Lite的信息,請(qǐng)參閱第2-2頁(yè)的表2-1

2023-08-02 06:51:45

Arm AMBA協(xié)議集中,AXI協(xié)議是基于burst的嗎?

2022-09-28 10:21:03

in the reference design consist of AXI4, AXI4-Lite, andAXI4-Stream interfaces as described in the AMBA AXI4

2012-01-26 18:57:03

傳輸和亂序傳輸?shù)龋⑶覕?shù)據(jù)位寬也受到限制。由于不需要支持大多數(shù)高性能功能,AXI4-Lite所需的資源也較少。

AXI4-Stream:主要用于高速數(shù)據(jù)流數(shù)據(jù)傳輸。相比于其他總線協(xié)議

2025-06-02 23:05:19

的方式實(shí)現(xiàn)功能的控制和狀態(tài)的監(jiān)測(cè)。 為方便用戶訪問(wèn)這些寄存器組, 系統(tǒng)控制模塊采用 AXI4-Lite 總線作為接口, AXI4-Lite 接口具有低帶寬、 低延時(shí)、 低復(fù)雜度的特點(diǎn), 采用該接口可以簡(jiǎn)化

2025-06-29 18:07:38

高性能、高帶寬、低延時(shí)的片內(nèi)互連需求。AXI4總線則是AXI總線的第四代版本,主要包含三種類型的接口,分別是面向高性能地址映射通信的AXI4接口、面向輕量級(jí)單次地址映射通信的AXI4-Lite接口和面

2025-05-17 10:27:56

為通用的AXI4接口,從而實(shí)現(xiàn)與其他模塊之間的高效互聯(lián)。

接口轉(zhuǎn)換模塊內(nèi)部包含AXI4-Lite寫轉(zhuǎn)換模塊、AXI4讀轉(zhuǎn)換模塊、AXI4寫轉(zhuǎn)換模塊。AXI4-Lite寫轉(zhuǎn)換模塊是用于將內(nèi)部信號(hào)

2025-05-10 14:33:03

。

Axi4_lite_agent 負(fù)責(zé)對(duì)接 AXI4-Lite 接口。 在 DUT 使用的三個(gè)接口中, AXI4-Lite接口用于連接系統(tǒng)控制模塊, 實(shí)現(xiàn)系統(tǒng)控制功能, 所以激勵(lì)的添加主要通過(guò) AXI4-Lite接口。 在

2025-08-29 14:33:19

,分別為:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也稱為 AXI4-Full 是一種基于地址的高性能傳輸接口,其支持亂序傳輸、突發(fā)傳輸?shù)葌鬏敺绞剑瑫r(shí)通過(guò)獨(dú)立

2025-06-24 18:00:11

這是SoC Designer AXI4協(xié)議包的用戶指南。該協(xié)議包包含SoC Designer組件、探針和ARM AXI4協(xié)議的事務(wù)端口接口(包括對(duì)AMBA4 AXI的支持)。

2023-08-10 06:30:18

你好,我有一個(gè)關(guān)于XADC及其AXI4Lite接口輸入的問(wèn)題。我想在Microzed 7020主板上測(cè)試XADC,在通過(guò)AXI4Lite接口將Zynq PL連接到XADC向?qū)В▍⒁?jiàn)第一個(gè)附件)之后

2018-11-01 16:07:36

memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數(shù)據(jù)突發(fā)傳輸;AXI4-Lite:(For simple

2018-01-08 15:44:39

。

●AXI4: 主要面向高性能地址映射通信的需求,允許最大256輪的數(shù)據(jù)突發(fā)傳輸。

●AXI4-Lite: 是一個(gè)輕量級(jí)的,適用于吞吐量較小的地址映射通信總線,占用較少的邏輯資源

2023-11-03 10:51:39

地傳輸信息,這一組信號(hào)就組成了接口。AXI4協(xié)議支持以下三種類型的接口:1、AXI4:高性能存儲(chǔ)映射接口。2、AXI4-Lite:簡(jiǎn)化版的AXI4接口,用于較少數(shù)據(jù)量的存儲(chǔ)映射通信。3

2020-10-22 15:16:34

ap_none接口的IP核。在本章我們將通過(guò)呼吸燈實(shí)驗(yàn),來(lái)學(xué)習(xí)如何使用Vivado HLS工具生成一個(gè)帶有AXI4-Lite總線接口的IP核,并學(xué)習(xí)Vivado HLS工具C/RTL協(xié)同仿真平臺(tái)的使用,以及在

2020-10-10 17:01:29

大家好,我正在使用vivado 2014.4制作zc702板,我想使用axi lite ipif ip。首先我不能把它稱為IP,因?yàn)閂ivado找不到它,所以我直接使用vhdl文件到我的項(xiàng)目

2020-04-09 12:23:27

關(guān)于AXI Lite的問(wèn)題

為什么我寫的AXI Lite在使用AXI Lite Slave IP的時(shí)候可以正常握手,但是在使用AXI Lite接口的BRAM的時(shí)候就沒(méi)有辦法正常握手了,我找不到問(wèn)題在

2025-07-16 18:50:54

result [64])核心有兩個(gè)端口,一個(gè)64個(gè)整數(shù)/元素的輸入數(shù)組(合成為ap_memory),輸出端口合成為ap_fifo。我使用Axi4Lite / Slave向頂級(jí)模塊發(fā)出指令,以便將生成

2019-02-28 13:47:30

Arm AMBA協(xié)議集中,LPI 在AMBA4 出現(xiàn),協(xié)議和鏈路層 與 AXI/AHB 無(wú)關(guān) 獨(dú)立的嗎? AHB-lite 可否使用?

2022-09-08 11:35:56

嗨,我將通過(guò)測(cè)試驗(yàn)證這一點(diǎn),但我對(duì)AXI-Lite外設(shè)“寄存器寫入”如何出現(xiàn)在AXI-Lite總線上有疑問(wèn)。AXI標(biāo)準(zhǔn)表明數(shù)據(jù)和地址可以非常相互獨(dú)立地出現(xiàn),從靈活性的角度來(lái)看這是很好的,但是

2019-04-12 13:45:01

的FPGA開(kāi)始引入的一個(gè)接口協(xié)議(AXI3)。在ZYNQ中繼續(xù)使用,版本是AXI4,ZYNQ內(nèi)部設(shè)備都有AXI接口。AXI4-Lite則是AXI4的一個(gè)簡(jiǎn)化版本,實(shí)現(xiàn)AXI4運(yùn)行起來(lái)的最少接口

2019-05-06 16:55:32

你好,有人可以發(fā)給我們規(guī)格嗎?時(shí)序規(guī)范謝謝,Muuu

2020-08-10 06:35:55

,portis僅顯示為S_AXI。接口引腳與AXI lite兼容。我需要知道S_AXI端口是否遵循AXI_Lite協(xié)議。請(qǐng)注意屏幕截圖的標(biāo)記部分。

2020-05-14 09:09:35

PowerLogic 圖形化簡(jiǎn)明學(xué)習(xí)教程:本圖形化的教程由“威利馬電器(深圳)有限公司開(kāi)發(fā)部/高級(jí)工程師王萬(wàn)軍”于2004年3月26日創(chuàng)作編寫.本教程為免費(fèi)教程,可以自由傳插播和轉(zhuǎn)載,主要奉獻(xiàn)

2010-01-04 15:20:53 0

0 AMBA AXI 總線學(xué)習(xí)筆記,非常詳細(xì)的AXI總線操作說(shuō)明

2015-11-11 16:49:33 12

12 : AXI4-Stream—使用DMA時(shí),從Zynq SoC的XDAC流式接口到內(nèi)存映射,提供高性能輸出 AXI4-Lite —配置和控制XADC以及DMA控制器 AXI4 —配置

2017-02-08 08:10:39 527

527 本小節(jié)通過(guò)使用XPS中的定制IP向?qū)?ipwiz),為已經(jīng)存在的ARM PS 系統(tǒng)添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結(jié)構(gòu),并掌握AXI Lite IP的定制方法,為后續(xù)編寫復(fù)雜AXI IP打下基礎(chǔ)。

2017-02-10 20:37:12 6313

6313 了解System Generator如何提供AXI4-Lite抽象,從而可以將DSP設(shè)計(jì)融入嵌入式系統(tǒng)。

完全支持包括集成到IP目錄,接口連接自動(dòng)化和軟件API。

2018-11-27 07:24:00 3713

3713 由于ZYNQ架構(gòu)和常用接口IP核經(jīng)常出現(xiàn) AXI協(xié)議,賽靈思的協(xié)議手冊(cè)講解時(shí)序比較分散。所以筆者收藏AXI協(xié)議的幾種時(shí)序,方便編程。

2019-05-12 09:10:33 11737

11737

這將創(chuàng)建一個(gè)附帶 BD 的 Vivado 工程,此 BD 包含 AXI VIP (設(shè)置為 AXI4-Lite 主接口) 和 AXI GPIO IP。這與我們?cè)?AXI 基礎(chǔ)第 3 講一文 中完成的最終設(shè)計(jì)十分相似。

2020-04-30 16:24:50 3097

3097

在本教程中,我們將來(lái)聊一聊有關(guān)如何在 Vitis HLS 中使用 AXI4-Lite 接口創(chuàng)建定制 IP 的基礎(chǔ)知識(shí)。

2020-09-13 10:04:19 7397

7397

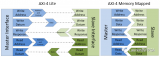

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,從下面的示例圖中就可見(jiàn)一斑。最直接的體現(xiàn)是AXI-4 Lite的突發(fā)長(zhǎng)度是固定值1。

2020-09-23 11:18:06 4269

4269

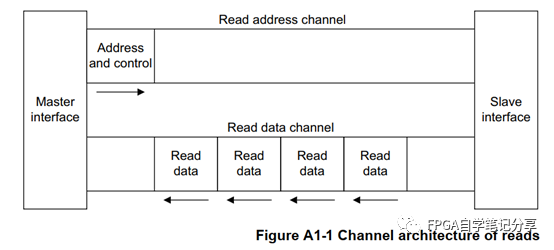

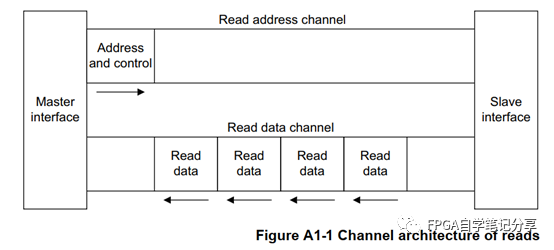

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協(xié)議的基礎(chǔ),其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個(gè)通道構(gòu)成,如下圖所示:寫地址通道、寫數(shù)據(jù)通道、寫響應(yīng)通道、讀地址通道和讀數(shù)據(jù)通道。

2020-09-23 11:20:23 6924

6924

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過(guò)AXI-Lite或

2020-09-24 09:50:30 7203

7203

在《AXI-Lite 自定義IP》章節(jié)基礎(chǔ)上,添加ilavio等調(diào)試ip,完成后的BD如下圖: 圖4?53 添加測(cè)試信號(hào) 加載到SDK,并且在Vivado中連接到開(kāi)發(fā)板。 Trigger Setup

2020-10-30 17:10:22 2961

2961

和接口的構(gòu)架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過(guò)

2020-11-02 11:27:51 5033

5033

在介紹AXI之前,先簡(jiǎn)單說(shuō)一下總線、接口以及協(xié)議的含義。總線、接口和協(xié)議,這三個(gè)詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。

2021-02-04 06:00:15 10

10 本文介紹了AMBA 3.0 AXI的結(jié)構(gòu)和特點(diǎn),分析了新的AMBA 3.0 AXI協(xié)議相對(duì)于AMBA 2. 0的優(yōu)點(diǎn)。它將革新未來(lái)高性能SOC總線互連技術(shù),其特點(diǎn)使它更加適合未來(lái)的高性能、低延遲

2021-04-12 15:47:39 28

28 在 AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡(jiǎn)介中,使用 C 語(yǔ)言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。 在本篇博文中,我們將學(xué)習(xí)如何導(dǎo)出 IP

2021-04-26 17:32:26 5440

5440

學(xué)習(xí)內(nèi)容 學(xué)習(xí)關(guān)于AXI總線的信號(hào)接口的具體要求(包括不同通道之間的關(guān)系,握手機(jī)制說(shuō)明等)和AXI4-Lite的相關(guān)信息,在文章后半部分對(duì)AXI讀寫時(shí)序進(jìn)行了簡(jiǎn)要講解,主要針對(duì)ARM公司

2021-04-30 11:22:13 5137

5137

學(xué)習(xí)內(nèi)容 學(xué)習(xí)關(guān)于AXI總線的信號(hào)接口的具體要求(包括不同通道之間的關(guān)系,握手機(jī)制說(shuō)明等)和AXI4-Lite的相關(guān)信息,在文章后半部分對(duì)AXI讀寫時(shí)序進(jìn)行了簡(jiǎn)要講解,主要針對(duì)ARM公司

2021-06-01 10:57:38 3463

3463

AXI總線學(xué)習(xí)AXI協(xié)議的主要特征主要結(jié)構(gòu)通道定義讀寫地址通道讀數(shù)據(jù)通道寫數(shù)據(jù)通道寫操作回應(yīng)信號(hào)接口和互聯(lián)寄存器片基本傳輸Read burstOverlapping read burstWrite

2021-12-05 16:21:03 5

5 目錄SPI主線協(xié)議——ESP32學(xué)習(xí)筆記零、前言一、什么是SPI?二、通信過(guò)程?三、極性和相位四、總結(jié)SPI主線協(xié)議——ESP32學(xué)習(xí)筆記零、前言在學(xué)習(xí)ESP32的過(guò)程中,了解到了IIC和SPI主線

2021-12-22 19:23:26 18

18 ARM 的 AXI 是一種面向突發(fā)的協(xié)議,旨在提供高帶寬同時(shí)提供低延遲。每個(gè) AXI 端口都包含獨(dú)立的讀寫通道。要求不高的接口使用的 AXI 協(xié)議的一個(gè)版本是 AXI4-Lite,它是一種更簡(jiǎn)單

2022-05-10 09:52:12 4734

4734 XI4-Stream跟AXI4的區(qū)別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數(shù)據(jù)的概念了,只有簡(jiǎn)單的發(fā)送與接收說(shuō)法,減少了延時(shí)。由于AXI4-Stream協(xié)議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒(méi)有時(shí)序圖,

2022-06-23 10:08:47 3052

3052 本文主要介紹關(guān)于AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核相關(guān)內(nèi)容。為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測(cè)試工程做準(zhǔn)備。

2022-07-03 16:11:05 10566

10566 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡(jiǎn)單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

2022-07-04 09:40:14 10523

10523 您是否想創(chuàng)建自己帶有 AXI4-Lite 接口的 IP 卻感覺(jué)無(wú)從著手?本文將為您講解有關(guān)如何在 Vitis HLS 中使用 C 語(yǔ)言代碼創(chuàng)建 AXI4-Lite 接口的基礎(chǔ)知識(shí)。

2022-07-08 09:40:43 2809

2809 前面簡(jiǎn)單學(xué)習(xí)了關(guān)于GPIO的操作,本次將使用PL 端調(diào)用 AXI GPIO IP 核, 并通過(guò) AXI4-Lite 接口實(shí)現(xiàn) PS 與 PL 中 AXI GPIO 模塊的通信。

2022-07-19 17:36:52 6444

6444 對(duì) AXI master的全面討論變得困難。我還沒(méi)有(還)想出如何簡(jiǎn)化材料來(lái)寫一篇關(guān)于如何構(gòu)建通用 AXI master器的帖子,這已經(jīng)夠難了——通常來(lái)說(shuō),尋址就是那么難。

2022-07-29 11:27:17 1543

1543 在 AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡(jiǎn)介中,使用 C 語(yǔ)言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學(xué)習(xí)如何導(dǎo)出 IP

2022-08-02 09:43:05 1247

1247

AXI (高性能擴(kuò)展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機(jī)總線系列中的一個(gè)協(xié)議,是計(jì)劃用于高性能、高主頻的系統(tǒng)設(shè)計(jì)的。AXI協(xié)議是被優(yōu)化

2022-10-10 09:22:22 11273

11273 上面兩圖的區(qū)別是相比AXI3,AXI4協(xié)議需要確認(rèn)AWVALID、AWREADY握手完成才能回復(fù)BVALID。為什么呢?

2023-03-30 09:59:49 1852

1852 之前文章為大家介紹了AXI的協(xié)議與架構(gòu),本篇我們接著往下講AXI的讀寫傳輸

內(nèi)容概括

2023-05-04 14:41:27 3072

3072

發(fā),同時(shí)提高部分功能模塊工作性能,集成的IP通常采用業(yè)界比較規(guī)范的總線協(xié)議,完成功能處理和數(shù)據(jù)傳輸。目前,常用的IP基本上均提供AXI4、 AXI4-Lite和 AXI4-Stream接口。

2023-05-04 14:51:53 2377

2377

AXI 協(xié)議有幾個(gè)關(guān)鍵特性,旨在改善數(shù)據(jù)傳輸和事務(wù)的帶寬和延遲

2023-05-06 09:49:45 1795

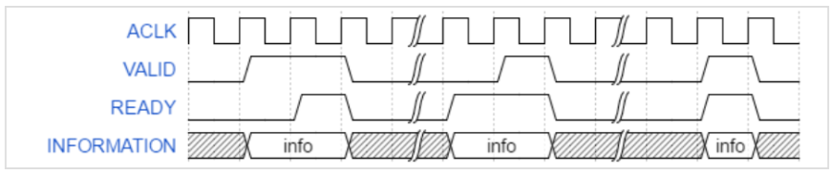

1795 AXI4 協(xié)議定義了五個(gè)不同的通道,如 AXI 通道中所述。所有這些通道共享基于 VALID 和 READY 信號(hào)的相同握手機(jī)制

2023-05-08 11:37:50 2040

2040

AMBA AXI協(xié)議支持高性能、高頻系統(tǒng)設(shè)計(jì)。

2023-05-24 15:05:12 1916

1916

上文FPGA IP之AXI4協(xié)議1_協(xié)議構(gòu)架對(duì)協(xié)議框架進(jìn)行了說(shuō)明,本文對(duì)AXI4接口的信號(hào)進(jìn)行說(shuō)明。

2023-05-24 15:05:46 2767

2767

上文FPGA IP之AXI4協(xié)議1_信號(hào)說(shuō)明把AXI協(xié)議5個(gè)通道的接口信息做了說(shuō)明,本文對(duì)上文說(shuō)的信號(hào)進(jìn)行詳細(xì)說(shuō)明。

2023-05-24 15:06:41 2083

2083

從 FPGA 應(yīng)用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 3091

3091

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實(shí)現(xiàn)一個(gè)簡(jiǎn)單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯(lián)結(jié)構(gòu)上,通過(guò) ZYNQ 主機(jī)控制,后面對(duì) Xilinx 提供的整個(gè) AXI4-Lite 源碼進(jìn)行分析。

2023-06-25 16:31:25 4882

4882

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關(guān)IP核中,經(jīng)常見(jiàn)到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

由數(shù)據(jù)線、地址線、控制線等構(gòu)成。 接口是一種連接標(biāo)準(zhǔn),又常常被稱之為物理接口。 協(xié)議是傳輸數(shù)據(jù)的規(guī)則。 1.簡(jiǎn)介 AXI4總線協(xié)議是 ARM 公司 提出的AMBA( Ad vanced Microcontroller Bus Archi te cture)3.0協(xié)議中最重要的部分,是一種面向高性能、高帶

2023-12-16 15:55:01 1879

1879 本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因?yàn)檫@個(gè)協(xié)議在SoC、IC設(shè)計(jì)中應(yīng)用比較廣泛。

2024-01-17 12:21:22 4273

4273

AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協(xié)處理器接口(AXI4-Lite)、AXI主外設(shè)接口(AXI4)、AXI外設(shè)到主處理器接口(AXI4-Lite)等。

2024-04-18 11:41:39 2500

2500 AXI4和AXI3是高級(jí)擴(kuò)展接口(Advanced eXtensible Interface)的兩個(gè)不同版本,它們都是用于SoC(System on Chip)設(shè)計(jì)中的總線協(xié)議,用于處理器和其它外設(shè)之間的高速數(shù)據(jù)傳輸。

2024-05-10 11:29:50 13098

13098

AMBA AXI4(高級(jí)可擴(kuò)展接口 4)是 ARM 推出的第四代 AMBA 接口規(guī)范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導(dǎo)體產(chǎn)業(yè)首個(gè)符合 AXI4 標(biāo)準(zhǔn)的即插即用型 IP 進(jìn)一步擴(kuò)展了 AMD 平臺(tái)設(shè)計(jì)方法。

2024-10-28 10:46:42 1383

1383

AXI4 總線是第四代 AXI 總線,其定義了三種總線接口,分別為:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也稱為 AXI4-Full 是一種基于地址的高性能

2025-06-24 23:22:33 523

523

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務(wù),而 PCIe 接口信號(hào)可被

2025-08-04 16:52:09 677

677

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務(wù),而 PCIe 接口信號(hào)可被

2025-08-25 18:53:01 2817

2817

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論