本章的實(shí)驗(yàn)任務(wù)是在 PL 端自定義一個(gè) AXI4 接口的 IP 核,通過(guò) AXI_HP 接口對(duì) PS 端 DDR3 進(jìn)行讀寫(xiě)測(cè)試,讀寫(xiě)的內(nèi)存大小是 4K 字節(jié)。

2025-11-24 09:19:42 3470

3470

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協(xié)議, Xilinx從 6 系列的 FPGA 開(kāi)始對(duì) AXI 總線提供支持,目前使用 AXI4

2020-12-04 12:22:44 9055

9055

FPGA+ARM是ZYNQ的特點(diǎn),那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個(gè)實(shí)驗(yàn)是創(chuàng)建一個(gè)基于AXI總線的GPIO IP,利用PL的資源來(lái)擴(kuò)充GPIO資源。通過(guò)這個(gè)實(shí)驗(yàn)迅速入門(mén)

2020-12-25 14:07:02 6725

6725

賽靈思 AXI Verification IP (AXI VIP) 是支持用戶對(duì) AXI4 和 AXI4-Lite 進(jìn)行仿真的 IP。它還可作為 AXI Protocol Checker 來(lái)使用。

2022-07-08 09:24:17 2976

2976 在 AXI 基礎(chǔ)第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協(xié)議檢查工具。在本次第4講中,我們將來(lái)了解下如何使用它在 AXI4 (Full) 主接口中執(zhí)行驗(yàn)證(和查找錯(cuò)誤)。

2022-07-08 09:31:38 4371

4371 首先對(duì)本次工程進(jìn)行簡(jiǎn)要說(shuō)明:本次工程使用AXI-Full接口的IP進(jìn)行DDR的讀寫(xiě)測(cè)試。在我們的DDR讀寫(xiě)IP中,我們把讀寫(xiě)完成和讀寫(xiě)錯(cuò)誤信號(hào)關(guān)聯(lián)到PL端的LED上,用于指示DDR讀寫(xiě)IP的讀寫(xiě)運(yùn)行

2022-07-18 09:53:49 7008

7008

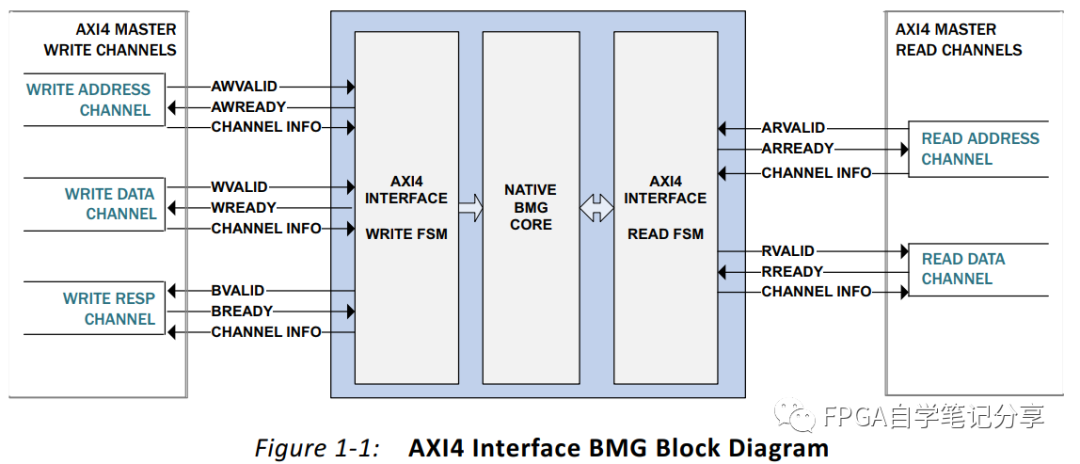

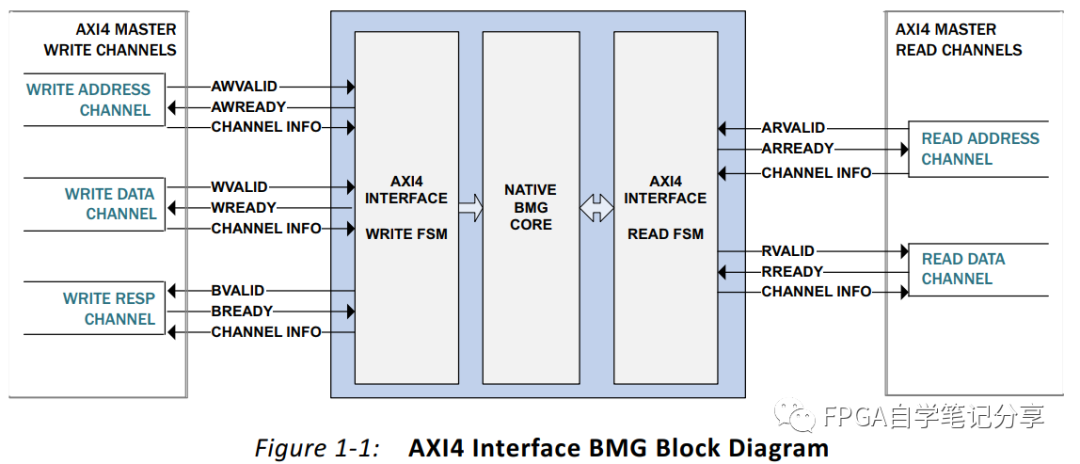

之前的文章對(duì)Block Memory Generator的原生接口做了說(shuō)明和仿真,本文對(duì)AXI接口進(jìn)行說(shuō)明。

2023-11-14 18:25:10 3670

3670

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統(tǒng)外設(shè)上生成特定序列(流量)。它根據(jù)IP的編程和選擇的操作模式生成各種類型的AXI事務(wù)。是一個(gè)比較好用的AXI4協(xié)議測(cè)試源或者AXI外設(shè)的初始化配置接口。

2023-11-23 16:03:45 5162

5162

AXI接口FIFO是從Native接口FIFO派生而來(lái)的。AXI內(nèi)存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應(yīng)用外,AXI FIFO還可以用于AXI系統(tǒng)總線和點(diǎn)對(duì)點(diǎn)高速應(yīng)用。

2025-03-17 10:31:11 1914

1914

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號(hào)的時(shí)鐘并行視頻數(shù)據(jù),即同步sync或消隱blank信號(hào)或者而后者皆有)轉(zhuǎn)換成AXI4-Stream接口形式,實(shí)現(xiàn)了接口轉(zhuǎn)換。該IP還可使用VTC核,VTC在視頻輸入和視頻處理之間起橋梁作用。

2025-04-03 09:28:14 2427

2427

AXI直接數(shù)值存取(Drect Memory Access,DMA)IP核在AXI4內(nèi)存映射和AXI4流IP接口之間提供高帶寬的直接內(nèi)存訪問(wèn)。DMA可以選擇分散收集(Scatter Gather

2025-04-03 09:32:24 2246

2246

,2GB的DDR3。 6、標(biāo)準(zhǔn)JTAG接口。 7、支持BPI模式快速加載。 基于賽靈思的V7 的FPGA開(kāi)發(fā)的PCIe DMA IP支持8.0Gbps(Gen3)at x8,x4,x2和x1的硬核,包括

2016-03-11 10:57:58

數(shù)據(jù)和輔助數(shù)據(jù)包不會(huì)通過(guò)AXI4-Stream上的視頻協(xié)議傳輸。Table 1-1 和Table 1-2 中列出AXI4S接口視頻IP需要的所有信號(hào)。Table 1-1 顯示了輸入(從)側(cè)連接器的接口信號(hào)名稱

2022-11-14 15:15:13

AXI4協(xié)議基于猝發(fā)式傳輸機(jī)制。在地址通道上,每個(gè)交易有地址和控制信息,這些信息描述了需要傳輸?shù)臄?shù)據(jù)性質(zhì)。主從設(shè)備間的數(shù)據(jù)傳輸有兩種情況,一種是主設(shè)備經(jīng)過(guò)寫(xiě)通道向從設(shè)備寫(xiě)數(shù)據(jù)(簡(jiǎn)稱寫(xiě)交易

2021-01-08 16:58:24

最近在搞AXI4總線協(xié)議,有一個(gè)問(wèn)題困擾了兩天,真的,最后知道真相的我,差點(diǎn)吐血。 問(wèn)題是這樣的,我設(shè)置了突發(fā)長(zhǎng)度為8,結(jié)果,讀了兩個(gè)輪回不到,斷了,沒(méi)有AWREDATY信號(hào)了,各種找,最后發(fā)現(xiàn)設(shè)置

2016-06-23 16:36:27

我想知道AXI4流互連IP 2中True Round-Robin和Round-Robin仲裁方案之間的區(qū)別,特別是當(dāng)所有從接口都不活動(dòng)時(shí)。我已經(jīng)參考了文檔PG085,并提到“如果所有從接口都不活動(dòng)

2020-05-20 14:51:06

的數(shù)據(jù)流標(biāo)識(shí)符。xilinx封裝的ip中沒(méi)有此信號(hào)。 9.TDEST 用于提供路由信息,xilinx封裝的ip中沒(méi)有此信號(hào)。 10.TUSER AXI4協(xié)議留給用戶自定義的。xilinx封裝的ip中沒(méi)有此信號(hào)

2021-01-08 16:52:32

說(shuō)明首先說(shuō)AXI4總線和AXI4-Lite總線具有相同的組成部分:(1)讀地址通道,包含ARVALID, ARADDR, ARREADY信號(hào);(2)讀數(shù)據(jù)通道,包含RVALID, RDATA

2022-04-08 10:45:31

分別為: AXI4:(For high-performance memory-mappedrequirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數(shù)據(jù)

2022-10-14 15:31:40

您可以將協(xié)議斷言與任何旨在實(shí)現(xiàn)AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協(xié)議通過(guò)一系列斷言根據(jù)協(xié)議檢查測(cè)試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

XHB將AXI4協(xié)議轉(zhuǎn)換為AHB-Lite協(xié)議,并具有AXI4從接口和AHB-Lite主接口。有關(guān)AXI4事務(wù)如何通過(guò)XHB橋接到AHB-Lite的信息,請(qǐng)參閱第2-2頁(yè)的表2-1

2023-08-02 06:51:45

Centronics標(biāo)準(zhǔn)接口信號(hào)說(shuō)明2)數(shù)據(jù)傳送時(shí)序圖12-13 并行打印機(jī)接口數(shù)據(jù)傳送時(shí)序

2009-03-10 11:58:18

廣泛應(yīng)用 。隨著時(shí)間的推移,AXI4的影響不斷擴(kuò)大。目前,由Xilinx提供的大部分IP接口都支持AXI4總線,使得系統(tǒng)中不同模塊之間的互連更加高效。這也讓基于這些IP的開(kāi)發(fā)變得更加快捷、方便和可靠

2025-06-02 23:05:19

高性能、高帶寬、低延時(shí)的片內(nèi)互連需求。AXI4總線則是AXI總線的第四代版本,主要包含三種類型的接口,分別是面向高性能地址映射通信的AXI4接口、面向輕量級(jí)單次地址映射通信的AXI4-Lite接口和面

2025-05-17 10:27:56

的轉(zhuǎn)換工作。接口轉(zhuǎn)換模塊的框圖如圖1所示。

圖1 接口轉(zhuǎn)換示意圖

?

?由于AXI4接口協(xié)議的實(shí)現(xiàn)會(huì)占用大量的邏輯資源,為了節(jié)約資源,控制器內(nèi)部的接口信號(hào)均采用邏輯簡(jiǎn)單的自定義接口,對(duì)外通過(guò)此模塊轉(zhuǎn)換

2025-05-10 14:33:03

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務(wù),而 PCIe 接口信號(hào)可被

2025-07-31 16:39:09

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務(wù),而 PCIe 接口信號(hào)可被

2025-08-26 09:49:46

)、 監(jiān)測(cè)器( monitor) 和序列發(fā)生器(sequencer)。 驅(qū)動(dòng)器從序列發(fā)生器獲取事務(wù), 并將其轉(zhuǎn)換為 AXI4-Lite 接口信號(hào);監(jiān)測(cè)器從接口上監(jiān)測(cè)信號(hào), 將其組成事務(wù)發(fā)送到參考模型

2025-08-29 14:33:19

的fifo接口),用戶只要操作fifo接口,無(wú)需關(guān)心PCIE的內(nèi)部驅(qū)動(dòng)。為了便于讀者更加明白,可以深入了解PCIE,我們將會(huì)制作一個(gè)PCIE的連載系列。今天,首先說(shuō)一下自定義AXI4的IP核,至于AXI4

2019-12-13 17:10:42

AXI 總線是一種高速片內(nèi)互連總線,其定義于由 ARM 公司推出的 AMBA 協(xié)議中,主要用于高性能、高帶寬、低延遲、易集成的片內(nèi)互連需求。AXI4 總線是第四代 AXI 總線,其定義了三種總線接口

2025-06-24 18:00:11

? 這里以功能完備的 AXI4 接口舉例說(shuō)明 AXI4 總線的相關(guān)特點(diǎn)。AXI4 總線采用讀寫(xiě)通道分離且數(shù)據(jù)通道與控制通道分離的方式,這樣的總線通道使其具有多主多從的連接特性和并行處理的能力,能夠

2025-06-24 18:02:23

這是SoC Designer AXI4協(xié)議包的用戶指南。該協(xié)議包包含SoC Designer組件、探針和ARM AXI4協(xié)議的事務(wù)端口接口(包括對(duì)AMBA4 AXI的支持)。

2023-08-10 06:30:18

或起點(diǎn)嗎?此外,我的VHDL模塊具有AXI4流接口,而其他模塊具有自定義接口。如何使它們兼容?將等待有用的回復(fù)。問(wèn)候

2020-05-22 09:24:26

)讀寫(xiě)、DMA讀寫(xiě)和數(shù)據(jù)擦除功能,提供用戶一個(gè)簡(jiǎn)單高效的接口實(shí)現(xiàn)高性能存儲(chǔ)解決方案。NVMe AXI4 Host Controller IP讀寫(xiě)的順序傳輸長(zhǎng)度是RTL運(yùn)行時(shí)動(dòng)態(tài)可配置的,最小

2025-11-14 22:40:50

接口,圖中已用紅色方框標(biāo)記出來(lái),我們可以清楚的看出接口連接與總線的走向:AXI協(xié)議之握手協(xié)議AXI4所采用的是一種READY,VALID握手通信機(jī)制,簡(jiǎn)單來(lái)說(shuō)主從雙方進(jìn)行數(shù)據(jù)通信前,有一個(gè)握手的過(guò)程

2018-01-08 15:44:39

是Vivado中十分常用的自定義IP核,使用AXI接口的IP,能夠方便的連接到軟核(MicroBlaze)或硬核(Zynq)的總線上,方便軟核或硬核對(duì)其進(jìn)行讀寫(xiě)操作。本設(shè)計(jì)的重點(diǎn)是使用FPGA邏輯設(shè)計(jì)獨(dú)立

2016-12-16 11:00:37

其添加到工程的IP庫(kù)中。我們?cè)凇蹲远xIP核-呼吸燈實(shí)驗(yàn)》中介紹了如何定義一個(gè)帶有AXI-Lite Slave接口的IP核,在本次實(shí)驗(yàn)中定義IP的方法與之相同,只是這次我們要選擇AXI4 Master接口

2020-10-22 15:16:34

的方式來(lái)自定義IP核,支持將當(dāng)前工程、工程中的模塊或者指定文件目錄封裝成IP核,當(dāng)然也可以創(chuàng)建一個(gè)帶有AXI4接口的IP核,用于MicroBlaze軟核處理器和可編程邏輯的數(shù)據(jù)通信。本次實(shí)驗(yàn)選擇常用的方式

2020-10-19 16:04:35

,當(dāng)然也可以創(chuàng)建一個(gè)帶有AXI4接口的IP核,用于MicroBlaze軟核處理器和可編程邏輯的數(shù)據(jù)通信。本次實(shí)驗(yàn)選擇常用的方式,即創(chuàng)建一個(gè)帶有AXI接口的IP核,該IP核通過(guò)AXI協(xié)議實(shí)現(xiàn)

2020-10-17 11:52:28

Vivado軟件中,通過(guò)創(chuàng)建和封裝IP向?qū)У姆绞絹?lái)自定義IP核,支持將當(dāng)前工程、工程中的模塊或者指定文件目錄封裝成IP核,當(dāng)然也可以創(chuàng)建一個(gè)帶有AXI4接口的IP核,用于PS和PL的數(shù)據(jù)通信。本次實(shí)驗(yàn)

2020-09-09 17:01:38

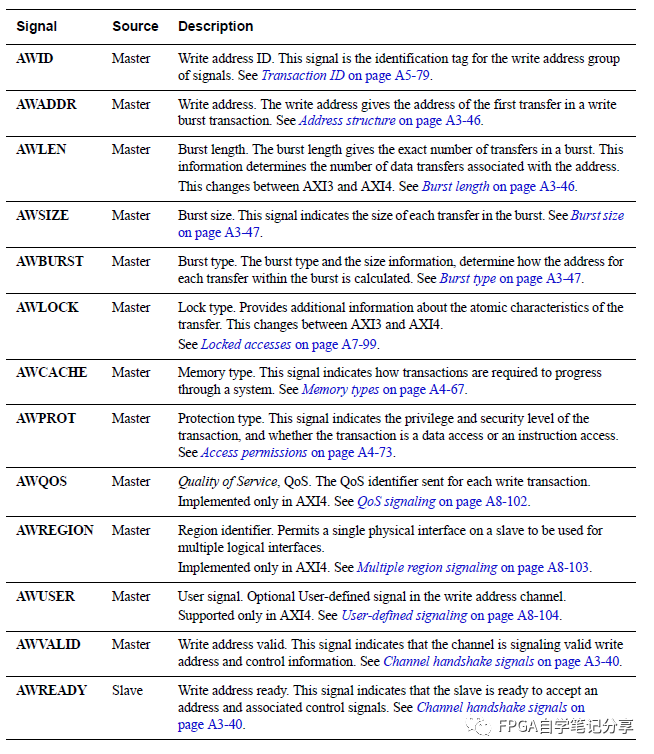

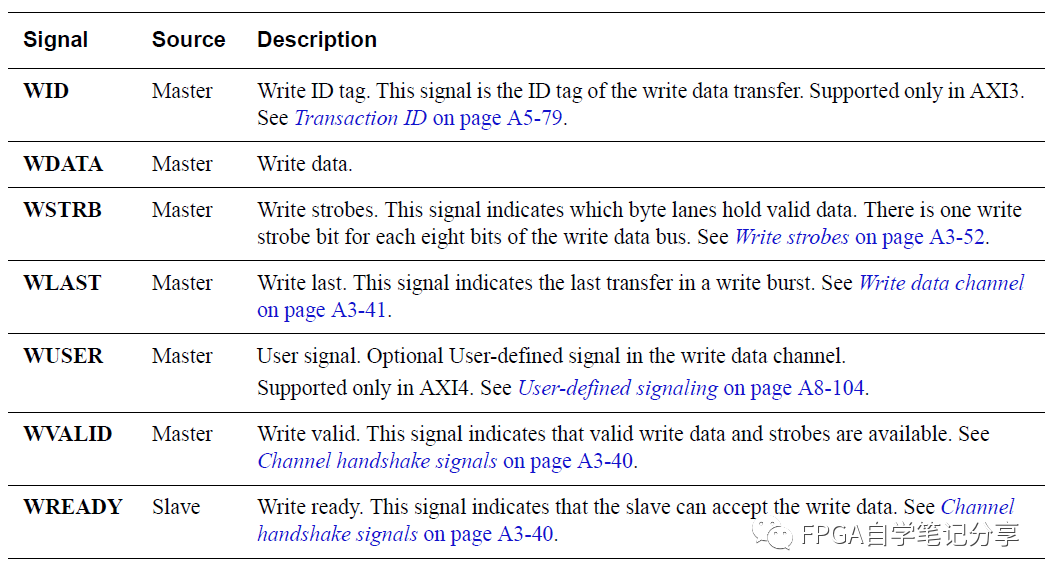

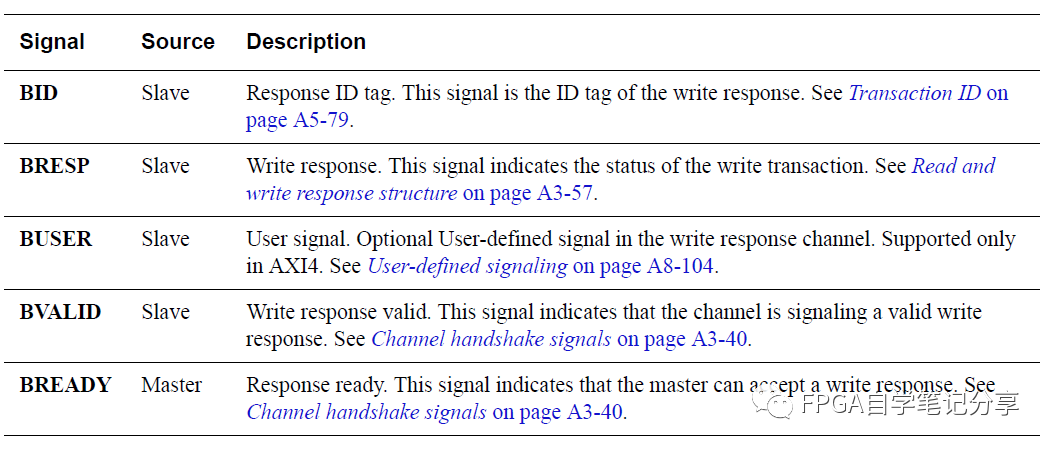

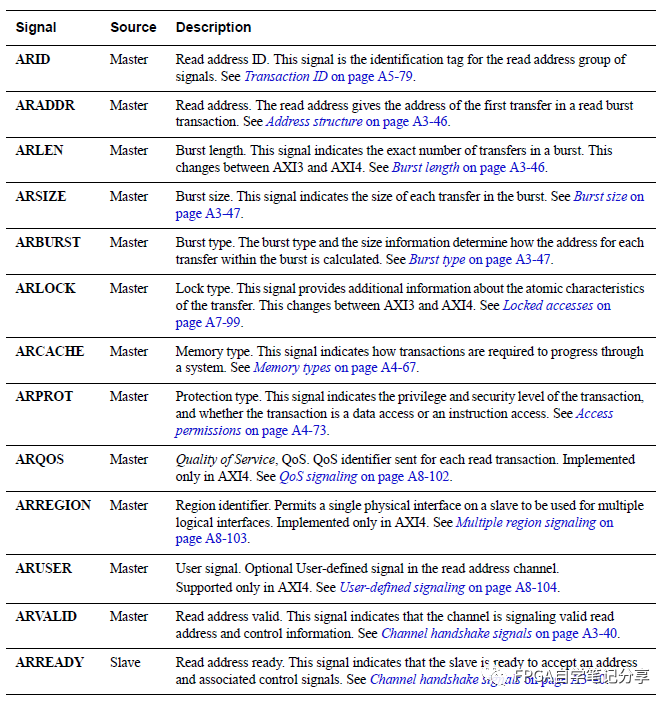

地址。數(shù)據(jù)傳輸使用寫(xiě)數(shù)據(jù)通道來(lái)實(shí)現(xiàn)主機(jī)到從機(jī)的寫(xiě)數(shù)據(jù)傳輸,數(shù)據(jù)傳輸使讀數(shù)據(jù)通道用來(lái)實(shí)現(xiàn)從機(jī)到主機(jī)的讀數(shù)據(jù)傳輸。下面以AXI4 IP核為例,詳細(xì)介紹AXI4協(xié)議的各通道和通道接口。在本實(shí)驗(yàn)中FPGA從外部

2020-10-22 15:27:28

原子公眾號(hào),獲取最新資料第十五章AXI4接口之DDR讀寫(xiě)實(shí)驗(yàn)Xilinx從Spartan-6和Virtex-6系列開(kāi)始使用AXI協(xié)議來(lái)連接IP核。在7系列和ZYNQ-7000 AP SoC器件中

2020-09-04 11:10:32

BRAM控制器來(lái)對(duì)BRAM進(jìn)行讀寫(xiě)操作。AXI BRAM控制器是集成在Vivado設(shè)計(jì)軟件中的軟核,可以配置成AXI4-lite接口模式或者AXI4接口模式。AXI4-Lite 接口模式的框圖如圖

2020-09-04 11:08:46

問(wèn)候,因此,我在創(chuàng)建IP外設(shè)并在VIVADO中使用ZYBO板單擊“使用AXI4 BFM仿真接口驗(yàn)證外設(shè)IP”選項(xiàng)時(shí)收到此錯(cuò)誤消息。我只想看到AXI接口的模擬我甚至沒(méi)有它的邏輯,我創(chuàng)建了一個(gè)虛擬項(xiàng)目

2019-04-12 15:17:23

多選一的抉擇相較于Axi4寫(xiě)通路,多通路的多選一就容易多了。對(duì)于Axi4ReadOnlyArbiter,其僅需處理兩個(gè)問(wèn)題:Ar通路多端口仲裁,其處理和寫(xiě)通路aw通路基本相同,采用多端口RR調(diào)度即可

2022-08-08 14:32:20

大家好。我目前正在使用GTH收發(fā)器實(shí)現(xiàn)更復(fù)雜的設(shè)計(jì),這些收發(fā)器工作在2.8 GHz(5.6GB),我想知道我是否可以使用AXI4流以某種方式從收發(fā)器中提取輸入數(shù)據(jù)。有沒(méi)有辦法將數(shù)據(jù)寫(xiě)入內(nèi)存并

2019-05-05 13:14:10

你好是否可以使用帶有AXI4接口的邏輯核心ip reed solomon編碼器版本9。問(wèn)候Rose Varghese

2020-05-20 15:44:58

怎么判斷他到底采用了這三種握手里面的哪種握手,這實(shí)在令人費(fèi)解。還是PS端的DDR的機(jī)制的問(wèn)題。

5.31 update:

問(wèn)題找到部分:

情形一:接口的設(shè)置上,如果是設(shè)置為AXI4,如圖所示,

那么

2024-05-31 12:04:29

我想在ZYNQ上的PS也就是ARM上跑linux系統(tǒng),然后PL中有加入一個(gè)AXI4的IP,IP中有多個(gè)寄存器,我不知道該如何開(kāi)發(fā)驅(qū)動(dòng)程序來(lái)對(duì)這個(gè)寄存器列表進(jìn)行讀寫(xiě)。然后單個(gè)寄存器在Embedded

2015-07-22 19:11:29

讀寫(xiě)分離的設(shè)計(jì)在Axi4總線中,讀和寫(xiě)通道是完全相互獨(dú)立,互不干擾。故而無(wú)論是在設(shè)計(jì)Decoder還是Arbiter時(shí),均可以采用讀寫(xiě)分離的方式。如前文所述,SpinalHDL在基于Axi4總線

2022-08-03 14:27:09

,ar)共用一組信號(hào)的接口(arw,w,b,r)。關(guān)于總線互聯(lián)的設(shè)計(jì)凡是設(shè)計(jì)中用到Axi4總線的設(shè)計(jì)總離不開(kāi)總線互聯(lián)。在Xilinx FPGA使用中,VIvado針對(duì)Axi4總線提供了豐富的IP,對(duì)于

2022-08-02 14:28:46

microblaze通過(guò)串口讀寫(xiě)FPGA內(nèi)部axi4總線上的寄存器

2020-12-23 06:16:11

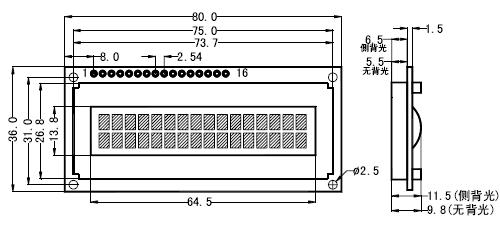

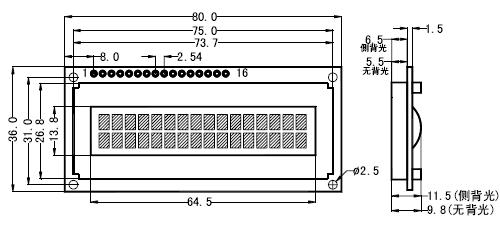

SMC1602液晶顯示屏的封裝尺寸及接口說(shuō)明

SMC1602液晶顯示屏接口信號(hào)說(shuō)明

2008-11-01 10:11:16 5498

5498

In the past decade, the size and complexity of manyFPGA designs exceeds the time

2012-03-07 14:37:03 18

18 Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個(gè)IP的作用。 下面看一下這個(gè)IP 的接口: 所以要把標(biāo)準(zhǔn)的VESA信號(hào) 轉(zhuǎn)為

2017-02-08 08:36:19 887

887

本文包含兩部分內(nèi)容:1)AXI接口簡(jiǎn)介;2)AXI IP核的創(chuàng)建流程及讀寫(xiě)邏輯分析。 1AXI簡(jiǎn)介(本部分內(nèi)容參考官網(wǎng)資料翻譯) 自定義IP核是Zynq學(xué)習(xí)與開(kāi)發(fā)中的難點(diǎn),AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

自定義sobel濾波IP核 IP接口遵守AXI Stream協(xié)議

2019-08-06 06:04:00 4566

4566 用xilinx fpgas中塊ram的性能和特性。BMG核心支持本機(jī)和Axi4接口。本機(jī)接口BMG核心配置支持由塊內(nèi)存生成器的早期版本(4.3版及之前的版本)提供的相同標(biāo)準(zhǔn)BMG功能。端口接口名稱相同。BMG核心的Axi4接口配置源自本機(jī)接口BMG配置,并在核心中添加了一個(gè)行業(yè)標(biāo)準(zhǔn)總線協(xié)議接口。提供兩種

2019-10-30 08:00:00 5

5 AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協(xié)議的基礎(chǔ),其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個(gè)通道構(gòu)成,如下圖所示:寫(xiě)地址通道、寫(xiě)數(shù)據(jù)通道、寫(xiě)響應(yīng)通道、讀地址通道和讀數(shù)據(jù)通道。

2020-09-23 11:20:23 6924

6924

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過(guò)AXI-Lite或

2020-09-24 09:50:30 7203

7203

在FPGA程序設(shè)計(jì)的很多情形都會(huì)使用到AXI接口總線,以PCIe的XDMA應(yīng)用為例,XDMA有兩個(gè)AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過(guò)

2020-10-30 12:32:37 5118

5118

引言 近來(lái),幾乎每個(gè)賽靈思 IP 都使用 AXI 接口。Zynq、Zynq MP、MicroBlaze 和全新的 Versal 處理器都無(wú)一例外使用 AXI 接口。因此,AXI 接口已成為幾乎所有

2020-09-27 11:06:45 7722

7722

AXI-Lite或AXI4轉(zhuǎn)接。PS與PL之間的物理接口有9個(gè),包括4個(gè)AXI-GP接口和4個(gè)AXI-HP接口、1個(gè)AXI-ACP接口。 Xilinx提供的從AXI到AXI-Stream轉(zhuǎn)換的IP核有:AXI-DMA,AXI-Datam

2020-11-02 11:27:51 5033

5033

本系列我想深入探尋 AXI4 總線。不過(guò)事情總是這樣,不能我說(shuō)想深入就深入。當(dāng)前我對(duì) AXI總線的理解尚談不上深入。但我希望通過(guò)一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 學(xué)習(xí)內(nèi)容 學(xué)習(xí)關(guān)于AXI總線的信號(hào)接口的具體要求(包括不同通道之間的關(guān)系,握手機(jī)制說(shuō)明等)和AXI4-Lite的相關(guān)信息,在文章后半部分對(duì)AXI讀寫(xiě)時(shí)序進(jìn)行了簡(jiǎn)要講解,主要針對(duì)ARM公司

2021-04-30 11:22:13 5137

5137

,它使用通用的AXI4接口在系統(tǒng)中移動(dòng)或轉(zhuǎn)換數(shù)據(jù),而不解釋數(shù)據(jù)。 這些基礎(chǔ)的IP各自有自己的常用的功能,下面列舉出一部分AXI接口的基礎(chǔ)構(gòu)架IP。 ° AXI Register slices

2021-05-11 14:52:55 7870

7870

學(xué)習(xí)內(nèi)容 學(xué)習(xí)關(guān)于AXI總線的信號(hào)接口的具體要求(包括不同通道之間的關(guān)系,握手機(jī)制說(shuō)明等)和AXI4-Lite的相關(guān)信息,在文章后半部分對(duì)AXI讀寫(xiě)時(shí)序進(jìn)行了簡(jiǎn)要講解,主要針對(duì)ARM公司

2021-06-01 10:57:38 3463

3463

本系列我想深入探尋 AXI4 總線。不過(guò)事情總是這樣,不能我說(shuō)想深入就深入。當(dāng)前我對(duì) AXI總線的理解尚談不上深入。但我希望通過(guò)一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的區(qū)別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫(xiě)數(shù)據(jù)的概念了,只有簡(jiǎn)單的發(fā)送與接收說(shuō)法,減少了延時(shí)。由于AXI4-Stream協(xié)議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒(méi)有時(shí)序圖,

2022-06-23 10:08:47 3052

3052 本文主要介紹關(guān)于AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核相關(guān)內(nèi)容。為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測(cè)試工程做準(zhǔn)備。

2022-07-03 16:11:05 10566

10566 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡(jiǎn)單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

2022-07-04 09:40:14 10523

10523 在 AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡(jiǎn)介中,使用 C 語(yǔ)言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學(xué)習(xí)如何導(dǎo)出 IP

2022-08-02 09:43:05 1247

1247

Xilinx vivado下通常的視頻流設(shè)計(jì),都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 7574

7574 AXI4S攜帶實(shí)際的視頻數(shù)據(jù)(無(wú)行場(chǎng)消隱),由主機(jī)和從機(jī)接口驅(qū)動(dòng),如Figure 1-1所示。

2022-11-14 09:15:25 2222

2222 上面兩圖的區(qū)別是相比AXI3,AXI4協(xié)議需要確認(rèn)AWVALID、AWREADY握手完成才能回復(fù)BVALID。為什么呢?

2023-03-30 09:59:49 1852

1852 AXI4 協(xié)議定義了五個(gè)不同的通道,如 AXI 通道中所述。所有這些通道共享基于 VALID 和 READY 信號(hào)的相同握手機(jī)制

2023-05-08 11:37:50 2040

2040

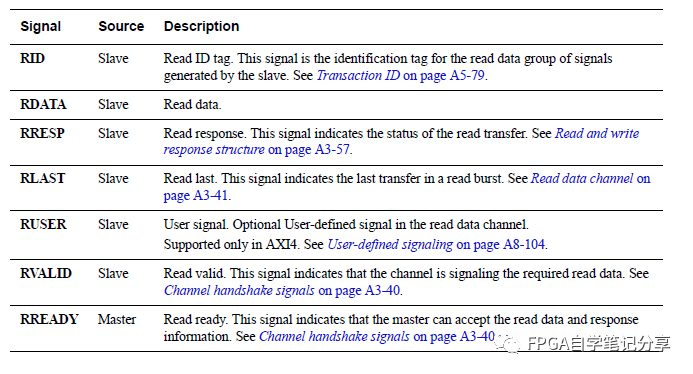

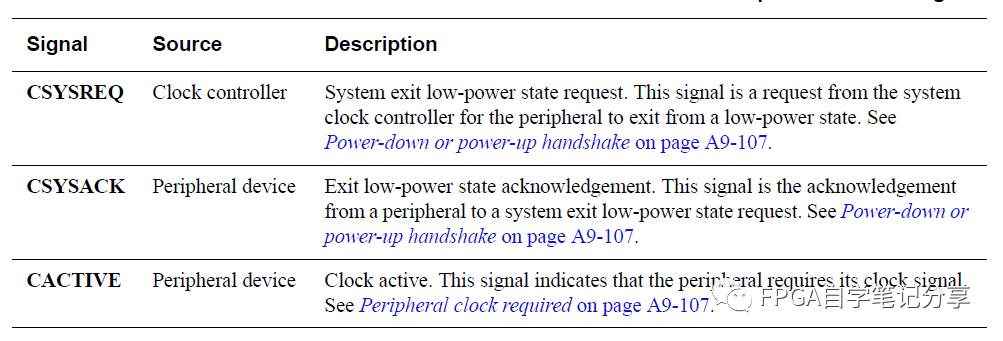

上文FPGA IP之AXI4協(xié)議1_協(xié)議構(gòu)架對(duì)協(xié)議框架進(jìn)行了說(shuō)明,本文對(duì)AXI4接口的信號(hào)進(jìn)行說(shuō)明。

2023-05-24 15:05:46 2767

2767

上文FPGA IP之AXI4協(xié)議1_信號(hào)說(shuō)明把AXI協(xié)議5個(gè)通道的接口信息做了說(shuō)明,本文對(duì)上文說(shuō)的信號(hào)進(jìn)行詳細(xì)說(shuō)明。

2023-05-24 15:06:41 2083

2083

AXI4協(xié)議是ARM的AMBA總線協(xié)議重要部分,ARM介紹AXI4總線協(xié)議是一種性能高,帶寬高,延遲低的總線協(xié)議。

2023-06-19 11:17:42 5678

5678

從 FPGA 應(yīng)用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 3091

3091

AXI4協(xié)議是一個(gè)點(diǎn)對(duì)點(diǎn)的主從接口協(xié)議,數(shù)據(jù)可以同時(shí)在主機(jī)(Master)和從機(jī)(Slave)之間**雙向** **傳輸** ,且數(shù)據(jù)傳輸大小可以不同。

2023-06-21 15:26:43 4254

4254

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實(shí)現(xiàn)一個(gè)簡(jiǎn)單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯(lián)結(jié)構(gòu)上,通過(guò) ZYNQ 主機(jī)控制,后面對(duì) Xilinx 提供的整個(gè) AXI4-Lite 源碼進(jìn)行分析。

2023-06-25 16:31:25 4882

4882

外部存儲(chǔ)器接口( EMIF )通信常用于FPGA和DSP之間的數(shù)據(jù)傳輸,即將FPGA作為DSP的外部SRAM、或者協(xié)同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 11849

11849

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關(guān)IP核中,經(jīng)常見(jiàn)到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因?yàn)檫@個(gè)協(xié)議在SoC、IC設(shè)計(jì)中應(yīng)用比較廣泛。

2024-01-17 12:21:22 4273

4273

Transaction Layer的所有功能特性,不僅內(nèi)置DMA控制器,而且具備AXI4用戶接口,提供一個(gè)高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時(shí)適用于ASIC和FPGA。

2024-02-21 15:15:03 2110

2110

Transaction layer的所有功能特性,不僅內(nèi)置DMA控制器,而且具備AXI4用戶接口,提供一個(gè)高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時(shí)適用于ASIC和FPGA。

2024-02-22 09:15:46 3

3 AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協(xié)處理器接口(AXI4-Lite)、AXI主外設(shè)接口(AXI4)、AXI外設(shè)到主處理器接口(AXI4-Lite)等。

2024-04-18 11:41:39 2500

2500 AXI4和AXI3是高級(jí)擴(kuò)展接口(Advanced eXtensible Interface)的兩個(gè)不同版本,它們都是用于SoC(System on Chip)設(shè)計(jì)中的總線協(xié)議,用于處理器和其它外設(shè)之間的高速數(shù)據(jù)傳輸。

2024-05-10 11:29:50 13098

13098

NVMe AXI4 Host Controller IP可以連接高速存儲(chǔ)PCIe SSD,無(wú)需CPU,自動(dòng)加速處理所有的NVMe協(xié)議命令,具備獨(dú)立的數(shù)據(jù)寫(xiě)入和讀取AXI4接口,不但適用高性能、順序

2024-07-18 09:17:19 1441

1441

AMBA AXI4(高級(jí)可擴(kuò)展接口 4)是 ARM 推出的第四代 AMBA 接口規(guī)范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導(dǎo)體產(chǎn)業(yè)首個(gè)符合 AXI4 標(biāo)準(zhǔn)的即插即用型 IP 進(jìn)一步擴(kuò)展了 AMD 平臺(tái)設(shè)計(jì)方法。

2024-10-28 10:46:42 1383

1383

接口轉(zhuǎn)換模塊負(fù)責(zé)完成AXI4接口與控制器內(nèi)部的自定義接口之間的轉(zhuǎn)換工作。由于AXI4接口協(xié)議的實(shí)現(xiàn)會(huì)占用大量的邏輯資源,為了節(jié)約資源,控制器內(nèi)部的接口信號(hào)均采用邏輯簡(jiǎn)單的自定義接口,對(duì)外通過(guò)此模塊轉(zhuǎn)換為通用的AXI4接口,從而實(shí)現(xiàn)與其他模塊之間的高效互聯(lián)。

2025-05-10 14:36:42 594

594

AXI4 總線是第四代 AXI 總線,其定義了三種總線接口,分別為:AXI4、AXI4-Lite 和 AXI4-Stream接口。其中 AXI4 也稱為 AXI4-Full 是一種基于地址的高性能

2025-06-24 23:22:33 523

523

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務(wù),而 PCIe 接口信號(hào)可被

2025-08-04 16:52:09 677

677

NVMe over PCIe采用 AXI4-Lite 接口、AXI4 接口和 PCIe3.0X4 接口,其中AXI4-Lite 和 AXI4 總線接口均可抽象為總線事務(wù),而 PCIe 接口信號(hào)可被

2025-08-25 18:53:01 2817

2817

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論