引言

在某些情況下,通過嗅探 AXI 接口來分析其中正在發生的傳輸事務是很有用的。在本文中,我將為大家演示如何創建基本 AXI4-Lite Sniffer IP 以對特定地址上正在發生的讀寫傳輸事務進行計數。

首先,編寫 HDL (Verilog) 代碼,然后將其封裝為 IP,最后將此 IP 添加到 IP IntegratorBlock Design (BD) 中。

我們將創建包含 AXI4-Lite 輸入接口的 AXI Sniffer 用于嗅探 AXI4-Lite 鏈接,并包含 2 項輸出以提供在特定地址上發生的讀寫傳輸事務的數量 (地址可通過 GUI 配置)。

創建 AXI Sniffer IP 以在 Vivado IP Integrator 中使用(教程)

1. 下載設計文件

https://forums.xilinx.com/xlnx/attachments/xlnx/support_blog/132/1/AXI_Basics_5.zip

2. 打開 Vivado 2019.2

3. 在 Tcl 控制臺中,使用 cd 命令導航到解壓縮的目錄 (cd AXI_Basics_5)

4.在 Tcl 控制臺中,使用 source 命令生成腳本 tcl (source ./create_proj.tcl)

這將創建一個附帶 BD 的 Vivado 工程,此 BD 包含 AXI VIP (設置為 AXI4-Lite 主接口) 和 AXI GPIO IP。這與我們在AXI 基礎第 3 講一文中完成的最終設計十分相似。

在此工程中,我們將創建 AXI Sniffer IP,然后嘗試將其連接到位于 AXI VIP 和 AXI GPIO IP 之間的 AXI4-Lite 接口

首先,讓我們來編寫適用于 AXI Sniffer IP 的 HDL (Verilog) 代碼

5.雙擊“源 (Sources)”窗口中的 AXI_Sniffer.v 文件以在文本編輯器中將其打開

首先,需要聲明 IP 端口。我們需要 1 個 AXI4-Lite 接口。根據 ARM 網站上提供的 AMBA AXI和 ACE協議規范 (掃碼查看),AXI4-Lite 接口上所需信號如下

我們還需要添加 2 個端口 (read_accesses 和 write_accesses),用于輸出監測地址的讀寫訪問次數。

6. 添加以下代碼以聲明所有必需的信號。

module AXI_Sniffer

(

input aclk,

input aresetn,

input s_axi_arvalid,

input s_axi_arready,

input [31:0] s_axi_araddr,

input [2:0] s_axi_arprot,

input s_axi_rvalid,

input s_axi_rready,

input [31:0] s_axi_rdata,

input [1:0] s_axi_rresp,

input s_axi_awvalid,

input s_axi_awready,

input [31:0] s_axi_awaddr,

input [2:0] s_axi_awprot,

input s_axi_wvalid,

input s_axi_wready,

input [31:0] s_axi_wdata,

input [3:0] s_axi_wstrb,

input s_axi_bready,

input s_axi_bvalid,

input [1:0] s_axi_bresp,

output [31:0] read_accesses,

output [31:0] write_accesses

);

注:在本例中,所有 AXI4-Lite 信號均設置為輸入,因為 IP 不應對 AXI4-Lite 接口執行任何操作,僅限于監測其中的流量

然后,IP 需要 1 個參數用于設置要監測的地址

7.添加以下代碼以添加用于監測地址的參數

module AXI_Sniffer

#(

parameter SLAVE_BASE_ADDR = 32'h40000000

)

(

最后,我們需要添加用于對地址訪問次數進行計數的邏輯。監測地址出現在 axi 總線上時,每次 r/wready 和 r/wvalid處于高位時,此代碼都會將計數增加 1。

8. 請將以下代碼添加到此文件中

reg [31:0] read_accesses_cnt;

reg [31:0] write_accesses_cnt;

assign read_accesses = read_accesses_cnt;

assign write_accesses = write_accesses_cnt;

//Check the Read Address Channel

always @(posedge aclk)

begin

if(aresetn == 0)

begin

read_accesses_cnt = 0;

end

else if (s_axi_arready && s_axi_arvalid && s_axi_araddr == SLAVE_BASE_ADDR)

begin

read_accesses_cnt = read_accesses_cnt + 1;

end

else

read_accesses_cnt = read_accesses_cnt;

end

//Check the Write Address Channel

always @(posedge aclk)

begin

if(aresetn == 0)

begin

write_accesses_cnt = 0;

end

else if (s_axi_awready && s_axi_awvalid && s_axi_awaddr == SLAVE_BASE_ADDR)

begin

write_accesses_cnt = write_accesses_cnt + 1;

end

else

write_accesses_cnt = write_accesses_cnt;

end

endmodule

9.保存 AXI_Sniffer.v 文件

在 IP Integrator 中,提供了一項允許用戶將 HDL 文件導入 BD 的功能。

10.右鍵單擊 BD,然后單擊“添加模塊 (Add Module...)”

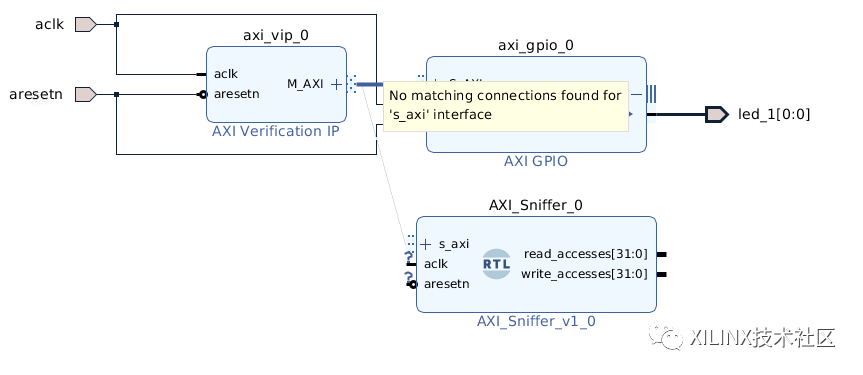

可以看到,該工具將所有 s_axi_* 信號組合為接口 s_axi。但如果我們嘗試將此接口連接到 AXI VIP 與 AXI GPIO 之間的現有連接上,該工具將會禁止此操作。

這是因為導入模塊工具已將 s_axi 接口設置為從接口,而 Vivado 僅允許每個主接口連接到一個從接口。

要創建監測 IP,我們需要將代碼封裝為 IP,這將為我們提供更多接口選項。

11.單擊“工具 (Tools) > 創建并封裝新 IP (Create and Package New IP...) ”

12.在“Create and Package New IP”的第 2 個頁面上,選擇“封裝指定目錄 (Package a specified directory)”,然后單擊“下一步 (Next)”

13.選中 AXI_Basics_5/src/hdl/AXI_Sniffer 目錄,然后單擊“Next > Next(保留默認設置) > 完成 (Finish)

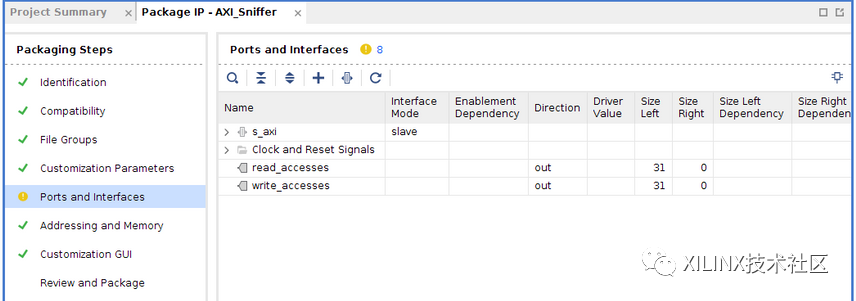

這樣將創建 IP Packager 工程 。在“封裝 IP (Package IP)”選項卡中,單擊“端口和接口 (Ports and Interface)”部分。

可以看到,工具又一次將 s_axi_* 信號分組構成 s_axi 接口。但此接口仍設置為從接口。要連接到現有 AXI 總線,我們需要告知該工具,此接口并非從接口,而是監測接口。

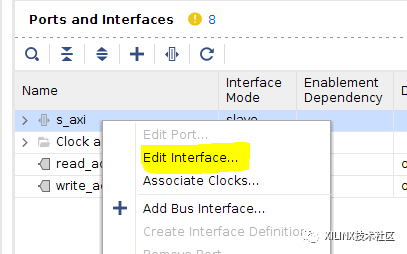

14.右鍵單擊 s_axi 接口,然后單擊“編輯接口 (Edit Interface...)”

15.在“Edit Interface”窗口的“常規 (General)”選項卡中,將“模式 (Mode)”更改為“monitor”

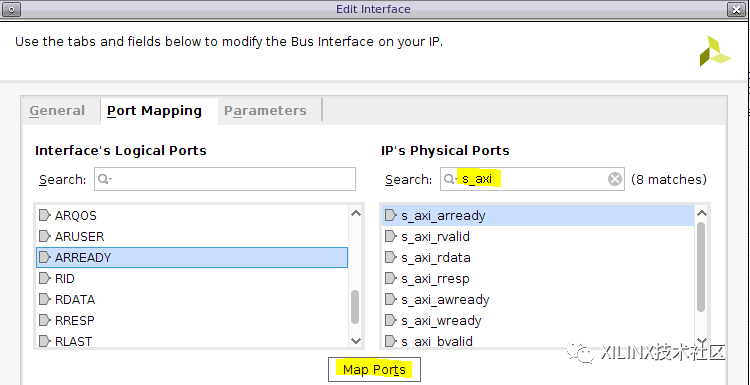

16. 然后單擊“端口映射 (Port Mapping)”選項卡,并啟用“隱藏已映射的端口 (Hide Mapped Port)”

17.對于 IP 的每個名為 s_axi_* 的物理端口,查找接口的匹配“邏輯端口 (Logical Ports)”,然后單擊“映射端口 (Map Ports)”

18.完成所有 s_axi_* 端口映射后,單擊“確定 (OK)”,以關閉“編輯接口 (Edit Interface)”窗口

19. 再次右鍵單擊 s_axi 接口,然后單擊“關聯時鐘 (Associate Clocks...)”

20. 在下一個窗口中,應該會自動選中 aclk。單擊“OK”

21. 單擊“復查并封裝 (Review and Package)”部分,然后單擊“封裝 IP (Package IP)”。

這樣將關閉 IP Packager 工程。

22. 從初始工程的 BD 中移除先前的AXI_Sniffer IP

23. 右鍵單擊初始工程的 BD,然后單擊“添加 IP (Add IP)”。找到 AXI Sniffer IP(應已自動添加到 IP 目錄中),并將其添加到 BD

24. 嘗試將新 AXI Sniffer IP 的 s_axi 接口連接到 AXI VIP 與 AXI GPIO 之間的總線。現在,此操作已可行。

25. 將定制 IP 的 aclk 和 aresetn 輸入端口連接到對應的 BD 端口。

26. 驗證 BD 設計。確保其中不存在任何嚴重警告或錯誤。保存 BD。

最后,我們可在仿真中驗證此 IP 是否有效。

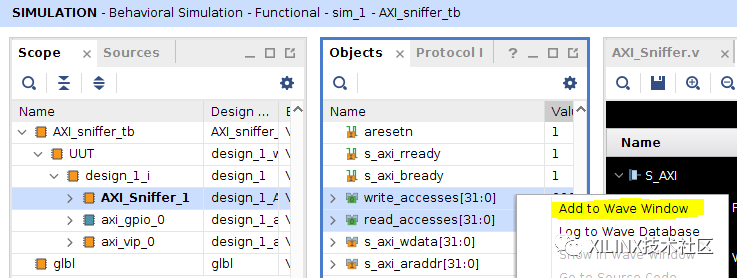

27. 啟動仿真,將 AXI_Sniffer IP 的端口 read_accesses 和 write_accesses 添加到波形窗口中。

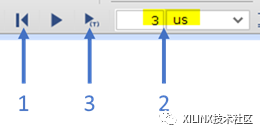

28.重新啟動仿真,保持運行 3us

在仿真波形中可以看到,正在執行 2 項讀取和 2 項寫入傳輸事務。但我們的 IP 計數僅顯示 2 項寫入傳輸事務和 1 項讀取傳輸事務。

我們可以觀察每項傳輸事務的地址,查看輸出是否正確。在 IP 監測的地址 0x4000_0000 上正在發生 2 項寫入傳輸事務。

但只有 1 項讀取傳輸事務目標為地址 0x4000_0000(另一項讀取傳輸事務目標為 0x4000_0008),因此 IP 行為正確。

本文僅展示了 1 個利用 AXI Sniffer(或者稱為 Monitor)IP 可實現的操作的示例。您可編輯 Verilog 代碼以添加自己的功能。

-

接口

+關注

關注

33文章

9519瀏覽量

157015 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133425

原文標題:AXI基礎第5講——創建 AXI4-Lite Sniffer IP 以在賽靈思 Vivado IP Integrator 中使用

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RDMA設計36:驗證環境設計

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

NVMe IP高速傳輸卻不依賴XDMA設計之三:系統架構

NVMe IP高速傳輸卻不依賴便利的XDMA設計之三:系統架構

NVMe IP之AXI4總線分析

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

如何創建基本AXI4-Lite Sniffer IP以對特定地址上正在發生的讀寫傳輸事務進行計數

如何創建基本AXI4-Lite Sniffer IP以對特定地址上正在發生的讀寫傳輸事務進行計數

評論