AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測試源或者AXI外設的初始化配置接口。

ATG(AXI Traffic Generator)IP的GUI如下圖所示。

AXI Traffic Generator是一個完全可綜合的符合AXI4標準的核心,具有以下特點:

- 可根據不同的流量配置選項生成和接受數據。

- 可配置的主AXI4接口地址寬度。

- 支持讀/寫主端口之間的相關/獨立事務,并具有可配置的延遲。

- 可編程的重復計數,對于每個事務可以使用恒定/遞增/隨機地址。

- 在AXI接口上為預定義的協議生成特定IP流量。

該IP的主要特性為:

- AXI4 接口適用于寄存器訪問和數據傳輸;

- 支持多種模式工作(AXI4 Master,AXI4-Lite Master, and AXI4-Stream Master);

- 高度靈活的數據位寬:32/64/128/256/512 axistream:8-1024;

- 高度靈活的地址位寬:32-64;

- 可為處理器資源較少系統中的系統初始化提供 AXI4-Lite 主接口支持;

- 中斷引腳,指示內核已完成流量生成;

- 錯誤中斷引腳,指示內核工作期間出現的錯誤。可通過讀取錯誤寄存器,了解所出現的錯誤;

- 內部 RAM(CMDRAM、PARAMRAM 和 MSTRAM)的初始化支持允許用戶針對所需的流量特性分析初始化所有 RAM 的內容;

它支持6種工作模式:

如下圖所示,在IP生成的時候可以在AXI4選項下選擇Advanced、Basic、Static三種模式;

AXI4-Stream模式如下圖所示:

如下圖所示,在IP生成的時候AXI4-Lite選項可以選擇System Init和Test Mode兩種模式;

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638461 -

寄存器

+關注

關注

31文章

5615瀏覽量

130316 -

接口

+關注

關注

33文章

9576瀏覽量

157530 -

Xilinx

+關注

關注

73文章

2205瀏覽量

131735 -

AXI

+關注

關注

1文章

145瀏覽量

18003

發布評論請先 登錄

相關推薦

熱點推薦

Xilinx zynq AXI總線全面解讀

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使

ARM+FPGA開發:基于AXI總線的GPIO IP創建

FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗

XILINX FPGA IP之Clocking Wizard詳解

鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明

發表于 06-12 17:42

?9348次閱讀

XILINX FPGA IP之MMCM PLL DRP時鐘動態重配詳解

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重

發表于 06-12 18:24

?1.8w次閱讀

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

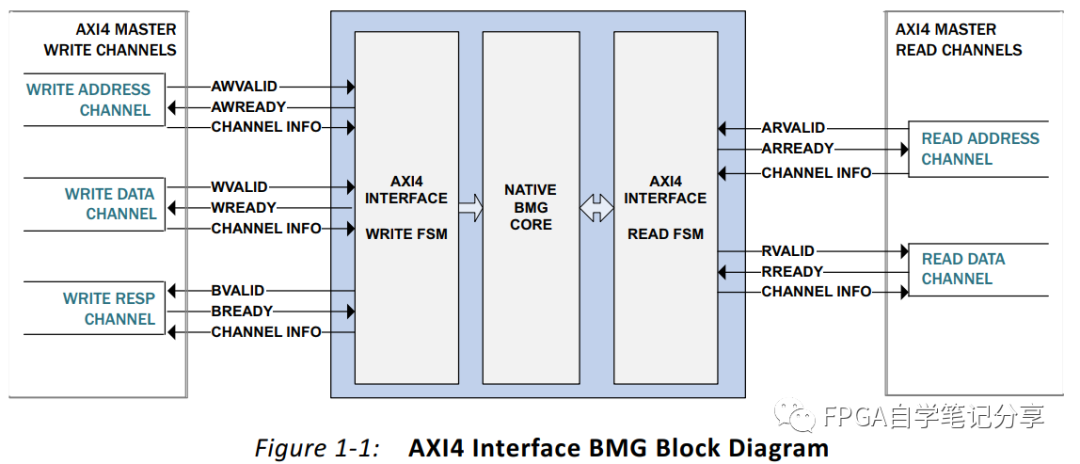

Xilinx FPGA IP之Block Memory Generator AXI接口說明

之前的文章對Block Memory Generator的原生接口做了說明和仿真,本文對AXI接口進行說明。

Xilinx FPGA片內ROM實例之ROM配置

Xilinx FPGA入門連載44:FPGA片內ROM實例之ROM配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

發表于 01-09 16:02

AXI 代碼 不通過 AXI Protocol Checker IP 的檢測

Checker IP 的檢測呢 ? https://www.xilinx.com/support/documentation/ip_documentation/axi_protoco

發表于 02-28 13:44

Xilinx的LogiCORE IP Video In to AXI4

Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個IP的作用。 下面看一下這個IP 的接口

發表于 02-08 08:36

?915次閱讀

FPGA開發之算法開發System Generator

的對應關系: System generator 安裝之后會在Simulin模塊庫中添加一些Xilinx FPGA專用的模塊庫,包括Basic Element,Communication,Control

發表于 11-17 14:29

?9138次閱讀

如何使用Xilinx AXI進行驗證和調試

了解如何使用Xilinx AXI驗證IP有效驗證和調試AXI接口。

該視頻回顧了使用的好處,以及如何使用示例設計進行模擬。

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC

XILINX FPGA IP之AXI Traffic Generator

XILINX FPGA IP之AXI Traffic Generator

評論