All Programmable技術和器件的全球領先企業賽靈思公司(Xilinx, Inc.,(NASDAQ:XLNX))昨日宣布推出符合汽車級要求的Zynq? UltraScale+? MPSoC系列器件,其可支持安全攸關的ADAS和自動駕駛系統的開發。

2018-01-17 09:15:26 9994

9994 Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內的控制寄存器進行通信。AXI-Lite允許構建簡單的元件接口。這個接口規模較小,對設計和驗證方面的要求更少

2020-09-27 11:33:02 9823

9823

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI

2020-12-04 12:22:44 9055

9055

FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗迅速入門

2020-12-25 14:07:02 6725

6725

一、AXI DMA介紹 本篇博文講述AXI DMA的一些使用總結,硬件IP子系統搭建與SDK C代碼封裝參考米聯客ZYNQ教程。若想讓ZYNQ的PS與PL兩部分高速數據傳輸,需要利用PS的HP

2020-12-31 09:52:02 10715

10715

使用zynq最大的疑問就是如何把PS和PL結合起來使用,在其他的SOC芯片中一般都會有GPIO,本實驗使用一個AXI GPIO的IP核,讓PS端通過AXI總線控制PL端的LED燈,實驗雖然簡單,不過可以讓我們了解PL和PS是如何結合的。

2021-02-01 10:06:00 7851

7851

由于ZYNQ架構和常用接口IP核經常出現 AXI協議,賽靈思的協議手冊講解時序比較分散。所以筆者收藏AXI協議的幾種時序,方便編程。

2022-08-02 12:42:17 9566

9566 在Zynq MPSoC的器件里,PS (Processing System )集成了三個看門狗,分別是CSU SWDT,LPD SWDT和FPD SWDT。

2023-06-30 09:47:22 2983

2983

本帖最后由 何立立 于 2018-1-9 15:03 編輯

ZYNQ 、AXI協議、PS與PL內部通信 三種AXI總線分別為:AXI4:(For high-performance

2018-01-08 15:44:39

ZYNQ Ultrascale+ MPSOC FPGA教程

2021-02-02 07:53:25

大部分器件的接口要求,提供互聯架構的靈活性與獨立性。

(1)AXI總線

總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般由數據線、地址線、控制線等構成。在ZYNQ中支持三種AXI總線

2023-11-03 10:51:39

1、Zynq MPSoC支持的DDR介紹自己做自己的嵌入式產品一般要選擇合適的DDR,而這里開發板給的是4GB的UIMM的DDR4,也就是電腦上用的,所以用不了,只能自己掛載Component,這里

2022-04-19 17:56:03

通信設備類功能的分步過程本節介紹CDC抽象控制模型(ACM)Linux小工具驅動程序的詳細信息,如何配置Linux源以支持Zynq?的串行小工具驅動程序UltraScale +?MPSoC USB

2019-01-03 09:59:50

MPSOC系列FPGA視頻教程目錄(總計128集)第一部分 MPSOC裸機開發(共65集)一、MPSoC簡介及開發流程01_MPSoC架構介紹02_MPSoC開發之Vivado工程創建流程03_MPSoC

2022-07-21 10:34:51

` Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平臺。其亮點在于FPGA里包含了完整的ARM處理子系統(PS),包含了四核Cortex-A53處理器或雙核

2021-01-07 17:11:26

管理系統;高密度片上UltraRAM靜態存儲器;單通道速率高達32Gbps的高速收發器;集成100GbE、PCIe Gen4、150Gbps Interlaken等I/O控制器;高性能UltraScale可編程邏輯。和Zynq-7000系列器件相比,加密、安全和電源管理都得到了顯著增強。

2019-10-09 06:07:09

,在詳細介紹具體步驟之前,我們先來了解什么是管理程序,以及它們如何與Zynq UltraScale+ MPSoC 上的處理器協同工作。

2019-10-09 06:21:21

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

`1、在開發zynq工程時遇到多個axi_hp總線讀寫ddr時,總線鎖死。現象就是axi_hp的wready信號一直為低。架構圖: 2、應用write1、wrtie2、read1同時并行讀寫ddr3

2020-04-15 21:57:28

介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹.pdf》。3 AXI GP外設配置在zstar_ex53實例的基礎上,需要對ZYNQ7Processing System(PS)配置頁面做更改

2019-11-12 10:23:42

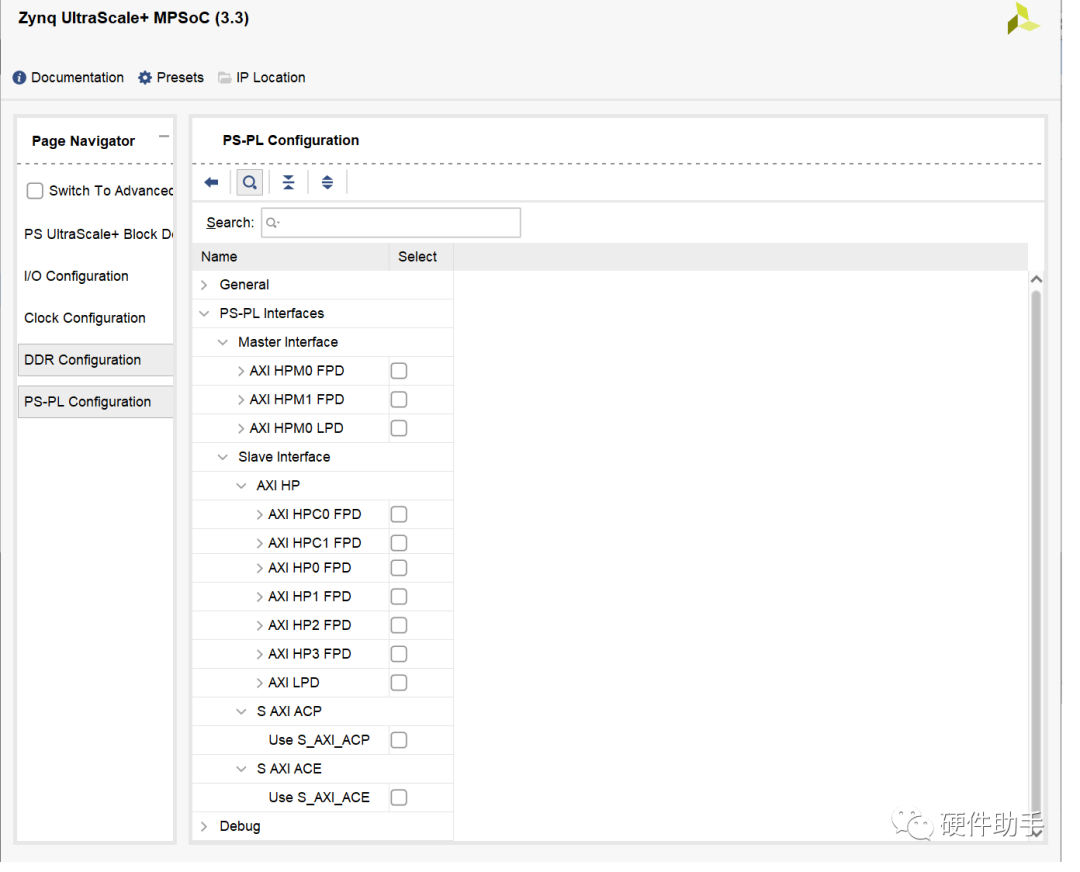

的邏輯設計。2 AXI總線協議介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹.pdf》。3Zynq PS的AXI HP配置在ZYNQ7 ProcessingSystem中,點擊左側Page

2019-11-26 09:47:20

不同通道使用情況下的數據吞吐量。大家可以在此基礎上,更改不同的AXI HP總線時鐘頻率,以評估時鐘頻率對AXI HP總線的影響。2 AXI總線協議介紹參考文檔《玩轉Zynq-基礎篇:AXI總線協議介紹

2019-11-28 10:11:38

`玩轉Zynq連載3——AXI總線協議介紹1 更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s 1 AXI協議簡介AMBA AXI(Advanced

2019-05-06 16:55:32

最近做的東西涉及到將原有的DSP+FPGA架構的程序移植到ZYNQ-7系列FPGA上,請問如何將原DSP程序移植到ZYNQ-7的ARM上,可不可以做一個EMIF總線和AXI總線轉換的模塊呢?

2014-05-12 21:51:09

你好我們正在考慮在我們的新設計中使用Zynq Ultrascale + MPSOC。我們想在我們的電路板設計中加入HDMI接口。 Zynq Ultrascale + MPSOC在PS中有一個

2019-10-14 09:17:03

AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 12

12 作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 在高性能系統中越來越多地使用高速串行互聯意味著你會在Zynq UltraScale+ MPSoC系列中的11款器件中發現很多Gbps

2017-02-08 05:50:41 847

847 Zynq UltraScale+ MPSoC器件提供64位處理器可擴展能力,將實時控制系統與軟件和硬件引擎相結合,完成顯示、視頻、波形生成以及數據包處理等操作。基于通用的實時處理器與可編程邏輯組合

2017-02-08 09:28:11 764

764

學了zynq一段時間,一上來的時候就被zynq的GPIO唬住了,實在沒搞清楚zynq的GPIO怎么回事,一會這樣,一會那樣,最后才慢慢發現zynq至少有3種GPIO可以調用。難怪我覺得每篇介紹

2017-02-08 10:23:12 3720

3720

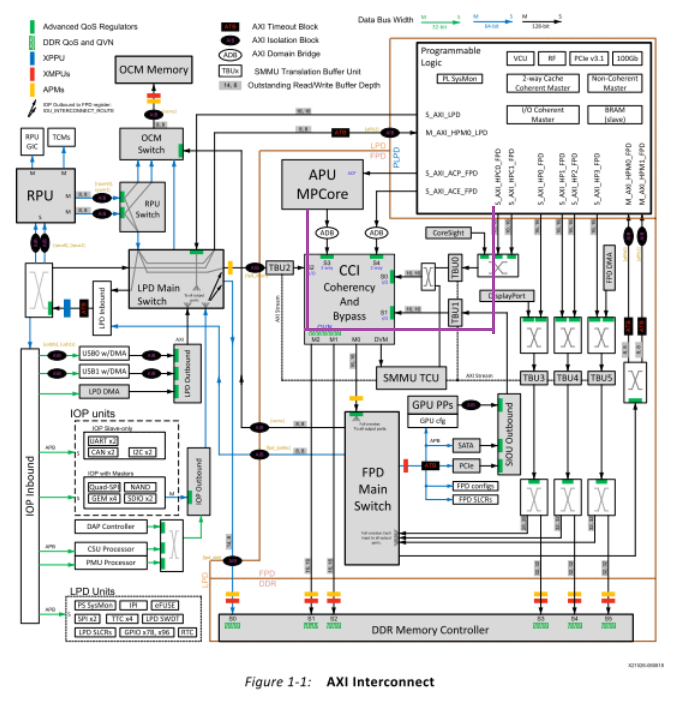

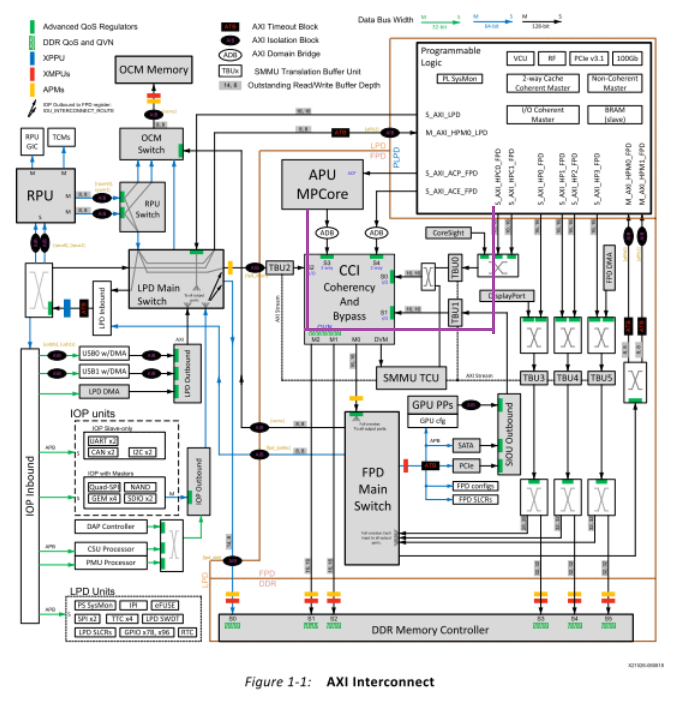

MPSoC器件族中的11個功能單元以“為任務量身打造模塊”的概念引入所需的處理能力。以下塊狀圖展示了 Xilinx Zynq UltraScale+ MPSoC系列中所有可用的元件。 這里可清楚看到

2017-02-09 08:01:11 3207

3207

本節介紹的AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。 書上講的AXI比較具體,本節呢不打算落入俗套,從應用角度解釋AXI。

2018-07-13 07:08:00 12677

12677

詳細介紹AXI總線

2017-02-28 21:03:54 1

1 本篇文章將與大家討論的是Xilinx Zynq UltraScale+ MPSoC的電源解決方案參考設計。

2017-03-14 02:24:12 4142

4142

本文主要介紹zynq linux AXI DMA傳輸步驟教程,具體的跟隨小編一起來了解一下。

2018-07-08 05:46:00 32067

32067

熟悉運行在賽靈思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 賽靈思和 DornerWorks 的系統軟件團隊在賽靈思的 Zynq? Ultrascale+? MPSoC

2017-11-16 20:17:53 3873

3873

QEMU 在 Xen 上運行 Doom 呢,在詳細介紹具體步驟之前,我們先來了解什么是管理程序,以及它們如何與Zynq UltraScale+ MPSoC 上的處理器協同工作。

2017-11-18 18:39:25 3104

3104

1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數據通道( W): write data

2018-01-05 08:13:47 11271

11271

本實驗工程將介紹如何利在賽靈思異構多處理器產品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式評估板上實現多個 UIO,同時借助賽靈思的工具完成硬件工程和 linux BSP 的開發,最后通過測試應用程序完成測試。

2018-03-21 14:55:00 3684

3684

本文試圖搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2929

2929 TIDA-01480 參考設計是一種可擴展的電源設計,旨在為 Xilinx Zynq UltraScale+ (ZU+) 系列 MPSoC 器件供電。此設計接收來自標準直流電源的電力,并通過明確的 Samtec 插座端子板連接方式為 Xilinx 芯片組和 DDR 存儲器的所有電源軌供電。

2018-10-14 08:52:00 2414

2414 該視頻重點介紹了UltraScale +產品系列的第一個成員Zynq?UltraScale+?MPSoC,并展示了使用可編程邏輯中的DDR4 SDRAM IP的存儲器接口系統的穩健性。

2018-11-29 06:36:00 3851

3851 該演示展示了Zynq UltraScale + MPSoC的視頻處理功能。

使用ZCU102開發套件,Zynq UltraScale + MPSoC將全高清1080p視頻輸入轉換為UltraHD 4K視頻輸出

2018-11-29 06:28:00 3667

3667 Zynq?UltraScale+?MPSoC,現已開始發售。視頻向您重點介紹了Xilinx UltraScale +產品組合的第一位成員

2018-11-27 06:47:00 4289

4289 該視頻重點介紹了UltraScale +產品組合的第一個成員,Zynq?UltraScale+?MPSoC,以及其多樣化收發器技術的穩健性。

2018-11-27 06:33:00 3300

3300 全新Zynq UltraScale MPSoC實現了前所未有的異構多處理能力,從而能夠實現“為合適任務提供合適引擎”。這些新器件相對此前解決方案可將系統級性能功耗比提升約5倍。位于處理子系統

中心

2018-11-27 06:09:00 4609

4609 行業抓取式演示視頻重點介紹了Zynq UltraScale + MPSoC裝有專用處理引擎,面向圖像處理,實時處理和功能安全性。

2018-11-23 06:59:00 3599

3599 該視頻顯示了Zynq?UltraScale+?MPSoC處理系統中硬化控制器的性能如何,LPDDR4以2.4Gbps運行48小時以上,在壓力下,具有低抖動和大量余量。

2018-11-22 06:14:00 4753

4753 本視頻向您演示了賽靈思16nm MPSoC產品系列的最新成員Zynq UltraScale + MPSoC EV器件的強大的實時視頻處理功能。該器件專為視頻處理等應用優化,集成H.264 / H.265視頻編解碼

單元,能夠以每秒60幀的速率同時對視頻進行4K編碼和解碼操作。

2018-11-22 05:51:00 4777

4777 (PS)和可編邏輯(PL)架構,主要用在航空航天與國防,汽車電子,數據中心,無線通信基礎設備和無線基礎設施.本文介紹了Xilinx公司的Zynq? UltraScale+?MPSoC系列主要特性,應用方案以及AvnetUltra96開發板主要特性,框圖,電路圖,材料清單和PCB設計圖.

2019-03-05 15:18:14 3941

3941

本文檔的主要內容詳細介紹的是zynq UltraScale MPSoC的產品選擇指南資料免費下載

2019-02-15 11:51:59 15

15 Zynq UltraScale+? MPSOC系列基于Xilinx UltraScale?MPSOC體系結構。該系列產品在單個設備中集成了功能豐富的64位四核或雙核ARM?Cortex?-A53

2019-02-21 16:48:54 22

22 由于ZYNQ架構和常用接口IP核經常出現 AXI協議,賽靈思的協議手冊講解時序比較分散。所以筆者收藏AXI協議的幾種時序,方便編程。

2019-05-12 09:10:33 11737

11737

XA Zynq UltraScale+ MPSoC 系列已通過 Exida 認證,符合 ISO 26262 ASIL-C 級的安全規范。Exida 是全球領先的自動化和汽車系統安全性和保密性專業認證公司之一。

2019-07-29 11:11:49 3228

3228 Zynq UltraScale+ MPSoC是Xilinx推出的第二代多處理SoC系統,在第一代Zynq-7000的基礎上做了全面升級,在單芯片上融合了功能強大的處理器系統(PS)和用戶可編程邏輯(PL)。Zynq UltraScale+ MPSoC系統框圖

2019-11-18 11:03:22 4111

4111

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI-Lite或

2020-09-24 09:50:30 7203

7203

新的賽靈思器件設計中不可或缺的一部分。充分了解其基礎知識對于賽靈思器件的設計和調試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關基礎知識。首先,我們將從一些通俗易懂的知識、理論

2020-09-27 11:06:45 7722

7722

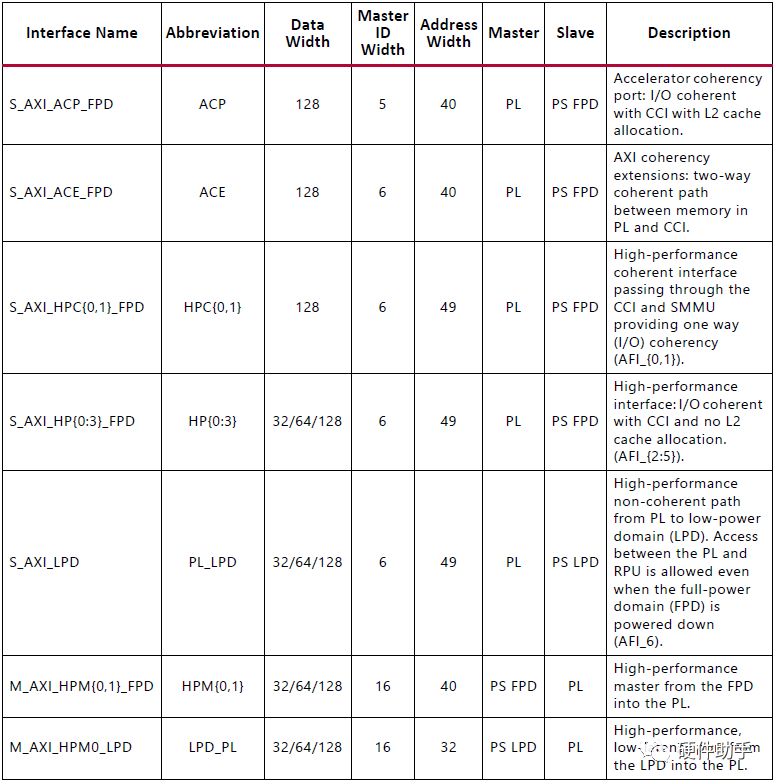

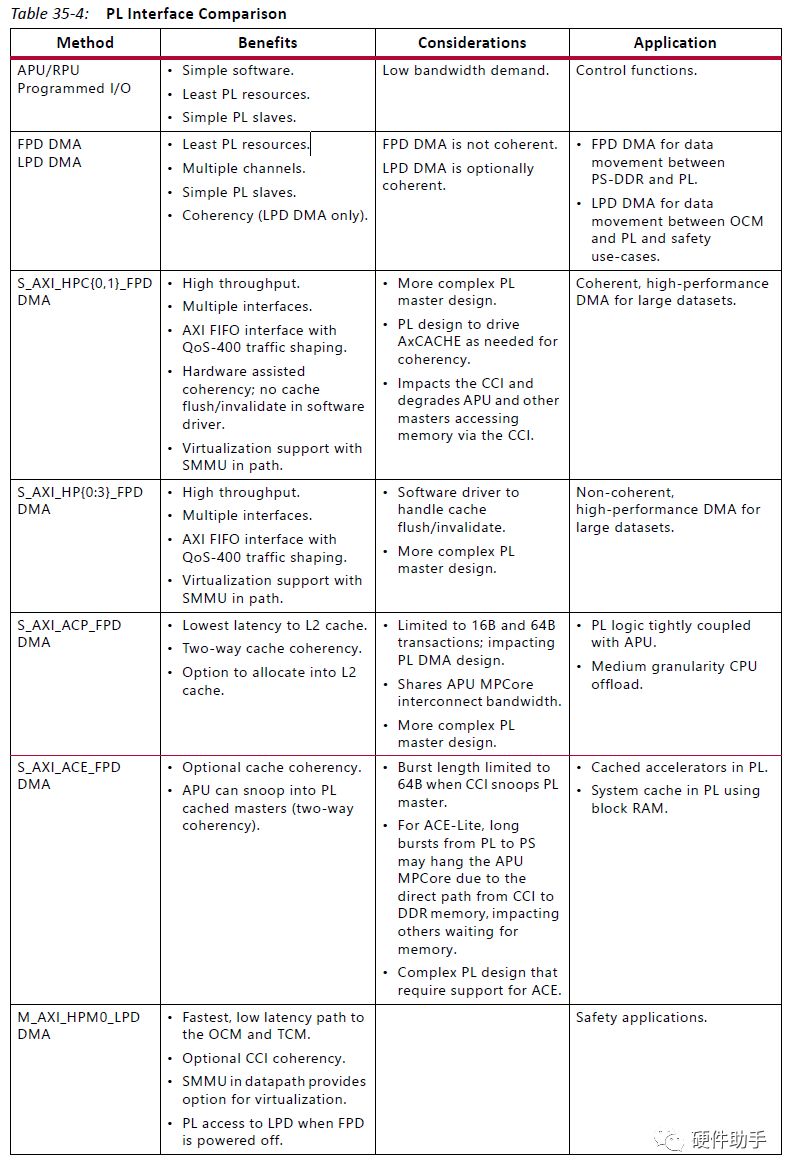

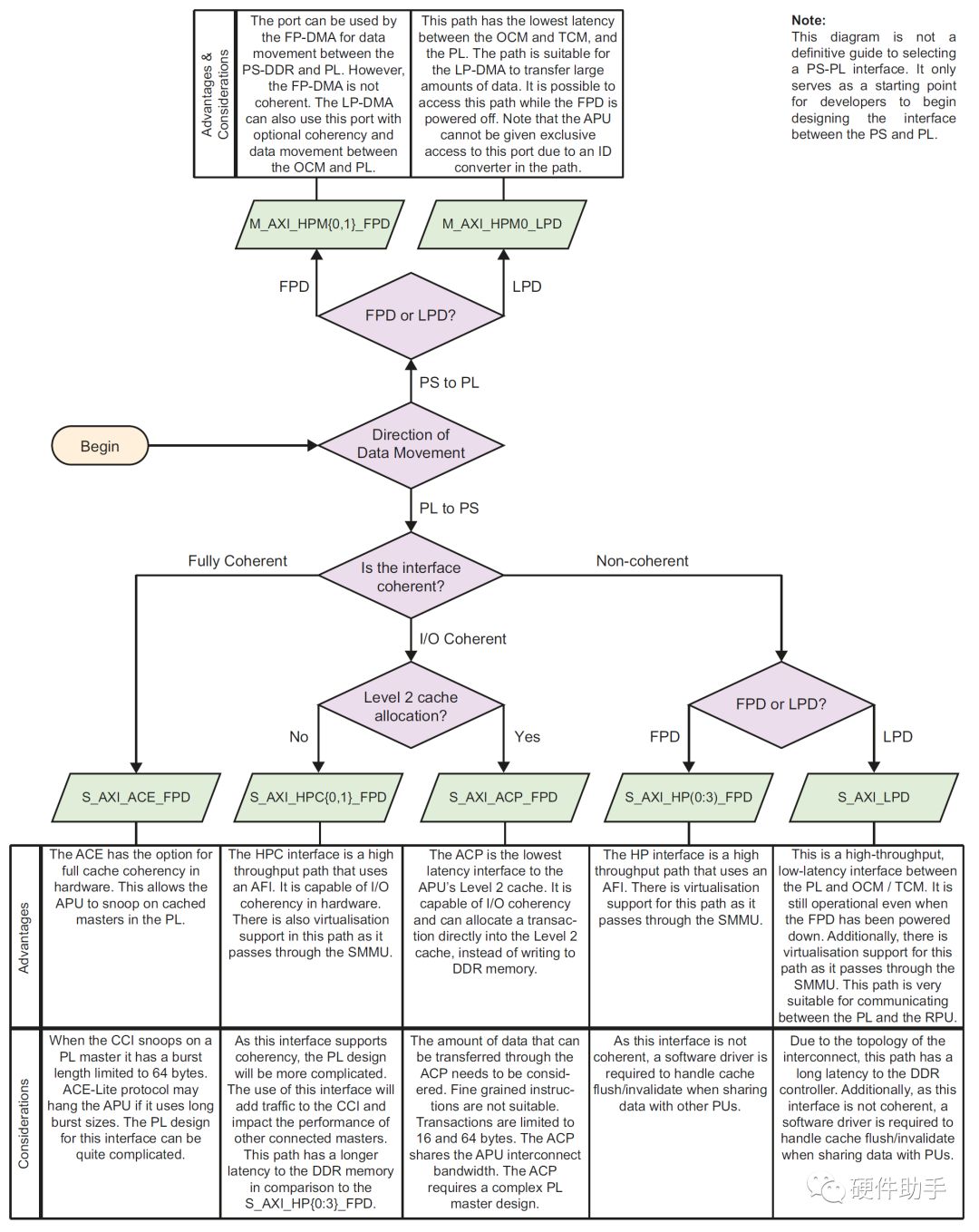

1. 參考文檔 1.1. AR69446 AR# 69446 Zynq UltraScale+ MPSoC Example Design - Use AXI HPC port to perform

2020-11-04 12:19:07 5209

5209

ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯

2020-11-02 11:27:51 5033

5033

在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2022-02-08 11:44:02 18240

18240 ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 3555

3555

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平臺。其亮點在于FPGA里包含了完整的ARM處理子系統(PS),包含了四核Cortex-A53處理器或雙核

2021-01-31 07:43:52 17

17 在介紹AXI之前,先簡單說一下總線、接口以及協議的含義。總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。

2021-02-04 06:00:15 10

10 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上與 Zynq

2021-02-23 06:00:10 15

15 。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點。 2.1 技術時間線 進一步介紹之前,需要指出這三種

2021-04-02 17:20:14 18829

18829

AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 7245

7245

本文介紹了AMBA 3.0 AXI的結構和特點,分析了新的AMBA 3.0 AXI協議相對于AMBA 2. 0的優點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲

2021-04-12 15:47:39 28

28 目錄1. MPSoC的中斷處理介紹 2. 擴展PL中斷 3. 擴展AXI Intc中斷 3.1. AXI Intc PL連接 3.2. AXI Intc Device Tree 3.3. AXI

2021-05-07 15:34:15 4690

4690 學習內容 近期設計需要用到AXI總線的IP,所以就對應常用的IP進行簡要的說明,本文主要對AXI互聯IP進行介紹。 基礎架構IP 基礎的IP是用于幫助組裝系統的構建塊。基礎架構IP往往是一個通用IP

2021-05-11 14:52:55 7870

7870

米爾電子推出的國內首款zynq ultrascale+ mpsoc平臺核心板(及開發板):MYC-CZU3EG吸引了人工智能、工業控制、嵌入式視覺、ADAS、算法加速、云計算、有線/無線通信等

2022-01-07 15:20:29 3

3 [導讀] 前面寫過篇介紹ZYNQ基本情況的文章,今天來肝一篇實戰文章介紹AXI quad SPI 使用方法,如果你正使用ZYNQ的這個IP,希望對你有所...

2022-01-26 17:01:47 7

7 關于AXI總線協議的一些簡單知識,通過閱讀Xilinx的使用指導手冊(UG1037),結合正點原子的ZYNQ視頻進行梳理總結。

2022-07-15 09:16:29 3977

3977 Zynq MPSoC是Zynq-7000 SoC(之后簡稱Zynq)的進化版本。Zynq是賽靈思發布的集成PL(FPGA)和PS設計的最早的一代產品。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點.

2022-08-15 09:16:38 3750

3750 ZU19EG 是一款緊湊型 SoC 原型開發板,采用 Zynq? UltraScale+? MPSoC 器件,可提供 64 位處理器可擴展性,同時將實時控制與軟和硬引擎相結合,用于 SoC 原型

2022-09-26 11:28:39 7

7 AXI (高性能擴展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機總線系列中的一個協議,是計劃用于高性能、高主頻的系統設計的。AXI協議是被優化

2022-10-10 09:22:22 11273

11273 基于 Xilinx 公司ZYNQ Ultrascale+ MPSoC系列 FPGA 芯片設計,應用于工廠自動化、機器視覺、工業質檢等工業領域

2022-11-02 14:35:47 2380

2380 在zynq開發過程中,AXI總線經常遇到,每次看到AXI總線相關的信號時都一頭霧水,仔細研究一下,將信號分分類,發現其實也不難。

2023-05-25 11:22:54 1790

1790

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 3091

3091

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 7276

7276

電子發燒友網站提供《Zynq UltraScale+ MPSoC:軟件開發者指南.pdf》資料免費下載

2023-09-14 10:03:42 15

15 電子發燒友網站提供《Zynq UltraScale+ MPSoC中的隔離方法.pdf》資料免費下載

2023-09-13 17:11:48 1

1 電子發燒友網站提供《Zynq UltraScale+ MPSoC的隔離設計示例.pdf》資料免費下載

2023-09-13 11:28:01 3

3 電子發燒友網站提供《適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計.pdf》資料免費下載

2023-09-13 09:55:25 10

10 電子發燒友網站提供《Zynq UltraScale+MPSoC嵌入式設計教程.pdf》資料免費下載

2023-09-13 09:14:33 6

6 電子發燒友網站提供《Zynq UltraScale+ MPSoC中的隔離方法應用筆記.pdf》資料免費下載

2023-09-15 14:49:14 0

0 電子發燒友網站提供《Zynq UltraScale+ MPSoC生產勘誤表.pdf》資料免費下載

2023-09-15 10:35:56 0

0 電子發燒友網站提供《Zynq UltraScale+ MPSoC數據手冊:DC和AC開關特性.pdf》資料免費下載

2023-09-15 10:27:21 3

3 電子發燒友網站提供《Zynq UltraScale+ MPSoC驗證數據手冊.pdf》資料免費下載

2023-09-15 10:13:41 0

0 電子發燒友網站提供《采用Zynq UltraScale+ MPSoC滿足汽車ESD和SEED要求.pdf》資料免費下載

2023-09-18 09:44:32 1

1 armbian、 hdmi、 zynq、 mpsoc、 rk3399

2023-10-13 18:11:00 3362

3362 ,同樣也是希望熟悉器件及其相關設計方法的技術人員的有效參考資料。前? 言Zynq MPSoC(多處理器片上系統)是Xilinx公司推出的第二代SoC系列產品,集成了復雜

2024-11-16 11:32:45 1190

1190

電子發燒友網站提供《Zynq UltraScale+ MPSoC數據手冊.pdf》資料免費下載

2024-12-30 14:37:55 3

3 通道,從ddr讀出數據通道和向ddr寫入數據通道。其IP結構的兩邊分別對應著用于訪問內存的AXI總線和用于用戶簡

2025-01-06 11:13:54 3774

3774

NVMe需要用AXI總線進行高速傳輸。而AXI總線是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)協議中的重要組成部分,主要面向高性能、高帶寬、低延時的片內互連需求。這里簡要介紹AXI總線區別,以及讀寫架構基本原理

2025-05-21 09:29:51 658

658

電子發燒友App

電子發燒友App

評論