AMBA AXI4(高級可擴展接口 4)是 ARM 推出的第四代 AMBA 接口規范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導體產業首個符合 AXI4 標準的即插即用型 IP 進一步擴展了 AMD 平臺設計方法。 對于依靠 IP 來推動 UltraScale、7 系統、Zynq 7000、Virtex 6 和 Spartan 6 型設計上市進程的客戶而言,AXI4 即插即用型 IP 提供了統一的標準接口,能顯著簡化 IP 集成。AMD 提供了一系列豐富的基于 AXI4 的 IP,為嵌入式、DSP 以及邏輯領域提供了統一的開放式標準接口。

更高的生產率

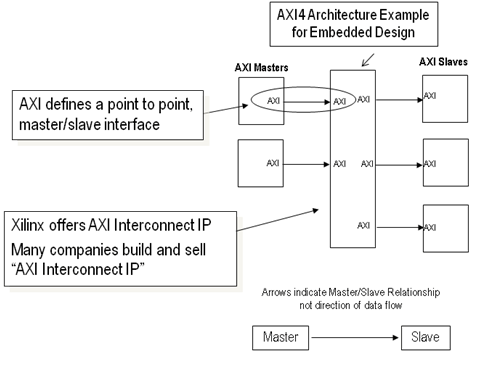

通過將多種不同的接口整合到一個接口(AXI4)中,用戶僅需了解單個系列的接口即可。

簡化了不同領域 IP 的集成,并使自身或第三方合作伙伴 IP 的開發工作更簡單易行。

由于 AXI4 IP 已為實現最高性能、最大吞吐量以及最低時延進行了優化,從而使設計工作進一步獲得簡化。

更大的靈活性

支持嵌入式、DSP 及邏輯版本用戶。

調節互連機制,滿足系統要求:性能、面積及功耗。

幫助您在目標市場中構建最具號召力的產品。

廣泛的 IP 可用性

AMD 同 ARM 密切合作,共同為基于 FPGA 的高性能系統和設計定義了 AXI4 規范。作為我們推廣 AXI4 工作的一部分,AMD 已采用 AXI4 作為 UltraScale、7 系統、Zynq 7000、Spartan 6、Virtex 6 以及未來產品系列發展的新一代 IP 互連標準。

AXI4 目標設計平臺幫助客戶加速嵌入式處理、DSP和連接功能設計開發。

AXI4 參考指南可指導用戶向 AXI4 標準過渡。

行業生態系統(Ecosystem)支持

第三方 IP 和 EDA 廠商普遍采用開放式 AXI4 標準,從而使該接口獲得了更廣泛的應用。

Cadence Design Systems, Inc. 、CAST, Inc.、Denali Software、Mentor Graphics Corp.、Northwest Logic、OMIINO ltd.、Sarance Technologies, Inc.、Synopsys, Inc. 以及 Xylon d.o.o. 紛紛宣布支持可滿足 AXI4 接口標準的 IP 及工具。

這能夠確保構建基于 AXI4 的系統設計能夠獲得強大的行業生態系統支持,從而實現終極生產率,并加速產品上市進程。

AXI4 接口的主要優勢

隨著 IP 通用用戶接口普遍采用 AXI4 標準,AMD 用戶將從中受益。AXI4 具有:

一致性:所有接口子集都使用相同的傳輸協議。

全面規范化:便于客戶采用。

標準化:配套提供標準模型和檢查器以供設計人員使用。

接口去耦化:互連電路與接口之間有去耦機制。

可擴展性:AXI4 是一種可滿足未來需求的開放式標準。

其它優勢:

支持存儲器映射型和串流型接口。

為通信、視頻、嵌入式以及 DSP 功能提供統一化 IP 接口。

簡便易用,并具有自動流水線例程化等特性,可幫助用戶輕松實現既定性能目標。

諸如 fMAX、LUT 使用、時延以及帶寬等關鍵屬性相當于或優于當前的解決方案。

使 AMD 能在所有應用領域高效提供增強型本地存儲器、外部存儲器接口以及存儲器控制器解決方案。

AXI 詳情AXI4

AXI4 協議是 AXI3 的升級,旨在提高多個主系統使用時的互連性能和互連利用率。其包括了如下增強功能:

支持高達 256 個突發長度

服務質量信令

支持多個區域接口

AXI4-Lite

AXI4-Lite 是 AXI4 協議的子集,旨在與組件中較小較簡單的控制寄存器型接口實現通信。AXI4-Lite 接口主要特性為:

所有處理的突發長度為 1

所有數據存取的大小等同于數據總線寬度

不支持獨占訪問

AXI4-Stream

AXI4-Stream 協議旨在實現從主系統向從系統進行單向數據傳輸,從而顯著減少信號傳輸。該協議的主要優勢包括:

使用相同的共享線集支持單數據流和多數據流

在同一互連中支持多數據寬度

FPGA 實現的理想選擇

-

FPGA

+關注

關注

1662文章

22464瀏覽量

637980 -

嵌入式

+關注

關注

5203文章

20555瀏覽量

335833 -

接口協議

+關注

關注

5文章

44瀏覽量

19119 -

AMBA

+關注

關注

0文章

70瀏覽量

16089 -

AXI4

+關注

關注

0文章

21瀏覽量

9186

原文標題:AMBA AXI4 接口協議

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何使用AXI VIP在AXI4(Full)主接口中執行驗證和查找錯誤

看看在SpinalHDL中AXI4總線互聯IP的設計

學習架構-AMBA AXI簡介

SoC Designer AXI4協議包的用戶指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協議斷言用戶指南

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

AMBA AXI4接口協議概述

AMBA AXI4接口協議概述

評論