2025年12月29日 – 隨著車載網絡朝 ADAS、信息娛樂和自動駕駛持續升級,100/1000BASE-T1 的物理層一致性驗證成為整車廠與Tier-1(一級供應商)的共同痛點。泰克科技宣布,在

2025-12-31 17:25:55 1229

1229

SN65MLVD204B:具有IEC ESD保護的多點LVDS線路驅動器和接收器 在硬件設計領域,數據傳輸的高效性和穩定性至關重要。SN65MLVD204B作為一款具有IEC ESD保護的多點

2025-12-19 09:30:05 183

183 100M、1000M以太網一致性測試

2025-12-14 10:42:36 285

285

SMD貼片式車規耐抗振電解電容通過封裝革新、全流程自動化工藝及智能化檢測技術,實現了高一致性生產,完全適配新能源汽車自動化產線需求 ,具體分析如下: 一、封裝革新:適配自動化生產的核心優勢 貼片式

2025-12-04 14:33:31 218

218 SMD貼片式車規鋁電解電容通過封裝革新、全流程自動化工藝及智能化檢測技術,實現了高一致性生產,完全適配新能源汽車自動化產線需求 。具體分析如下: 一、封裝革新:適配自動化生產的核心優勢 貼片式

2025-12-03 14:47:46 272

272 一、技術本質:定義與量化指標 相位一致性描述的是多通道電纜組件在相同頻率與輸入信號下,各通道輸出信號相位差的穩定程度。核心衡量指標包括: 相位偏差 :單通道相位的波動范圍 通道間相位差 :多通道之間

2025-11-27 13:41:52 166

166

ESD測試,即靜電放電測試(Electrostatic Discharge Testing),是一種用于評估電子設備或組件在靜電放電環境下的性能穩定性和可靠性的測試方法。以下是關于ESD測試的詳細

2025-11-26 07:37:49

該ADS61JB23是一款高性能、低功耗、單通道模數轉換器,具有集成JESD204A輸出接口。該ADS61JB23采用 6 mm × 6 mm QFN 封裝,具有單通道和雙通道輸出模式,具有前所未有

2025-11-17 10:28:13 462

462

接口與 JESD204A 標準兼容,并具有附加模式(根據 IEEE 標準 802.3-2002 第 3 部分第 36.2.4.12 條),可與 TI TLK 系列 SERDES 收發器無縫連接。同樣令人印象深刻的是片上模擬輸入緩沖器,可在采樣保持開關之間提供隔離,并提供更高、更一致的輸入阻抗。

2025-11-14 10:05:46 447

447

終端兼容的 DAC37J84/DAC38J84 系列是一款低功耗、16 位、四通道、 1.6/2.5 GSPS 數模轉換器 (DAC),帶JESD204B接口。

數字數據通過 1、2、4 或

2025-11-13 14:31:02 472

472

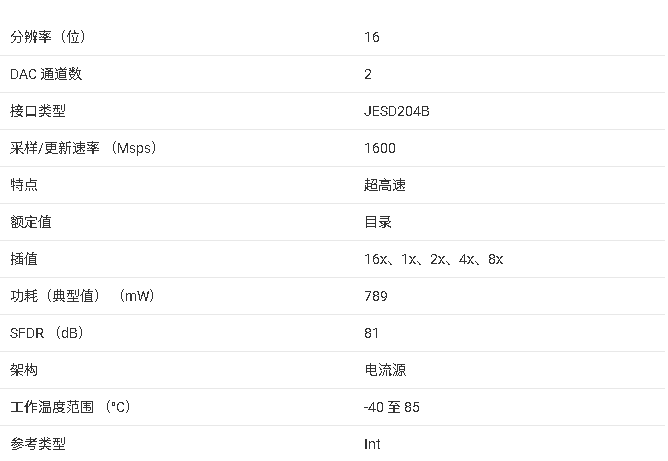

引腳兼容的DAC37J82/DAC38J82系列是一款非常低功耗、16位、雙通道、 1.6/2.5 GSPS 數模轉換器 (DAC),帶JESD204B接口。最大輸入數據速率 是 1.23 GSPS

2025-11-13 13:52:47 434

434

請教大家一下,DP的Vbios中已經固定了預加重和Swing的值,DP的TX信號一致性測試項中Non Pre-Emphasis Level Test(Swing2/Swing0)-PLTPAT,這個測試項意思是Swing2與Swing0偏差嗎?已經固定了Swing中,這一項測試還有意義嗎?請不吝指教

2025-11-12 15:57:58

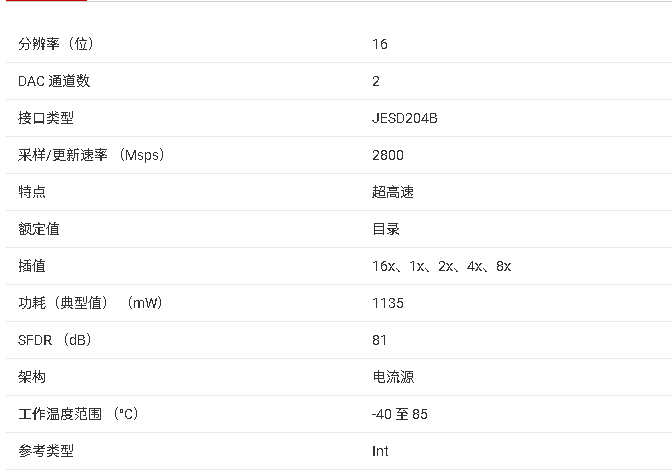

該DAC39J82是一款非常低功耗、16 位、雙通道、2.8 GSPS 數模 具有JESD204B接口的轉換器 (DAC)。最大輸入數據速率為1.4 GSPS。

數字數據通過 1、2、4 或

2025-11-12 11:32:03 547

547

輸入分頻器為系統時鐘架構設計和SYSREF輸入提供了更大的靈活性 實現完整的系統同步。這些設備支持JESD204B接口,以減少 接口線的數量,從而實現高系統集成密度。The JESD204B 接口是一個

2025-11-12 09:23:14 457

457

解決鋰電池一致性難題!景鋰新能源電池均衡儀為儲能/電動車電池續航保駕護航

2025-11-06 11:00:07 460

460 ?直播主題CAN總線一致性測試“一致性測試是保障總線系統穩定、兼容、可靠運行的核心環節。”隨著整車電子電氣架構日益復雜,ECU數量增多、通信負載加大,CAN節點之間若存在電氣特性不匹配、時序偏差

2025-10-30 17:34:23 2099

2099

傳輸速率的提升,以太網物理層面臨更多信號完整性、協議合規性等挑戰,造成網絡問題,這使得以太網設備在研發、生產和應用環節的物理層一致性測試變得尤為關鍵。航天測控公司

2025-10-30 09:02:12 281

281

作為半導體器件的潛在致命隱患,Latch Up(閂鎖效應)一直是電子行業可靠性測試的重點。今天,SGS帶你深入揭秘這個“隱形殺手”,并詳解國際權威標準JEDEC JESD78F.02如何通過科學的測試方法,為芯片安全筑起堅固防線。

2025-10-22 16:58:52 1528

1528

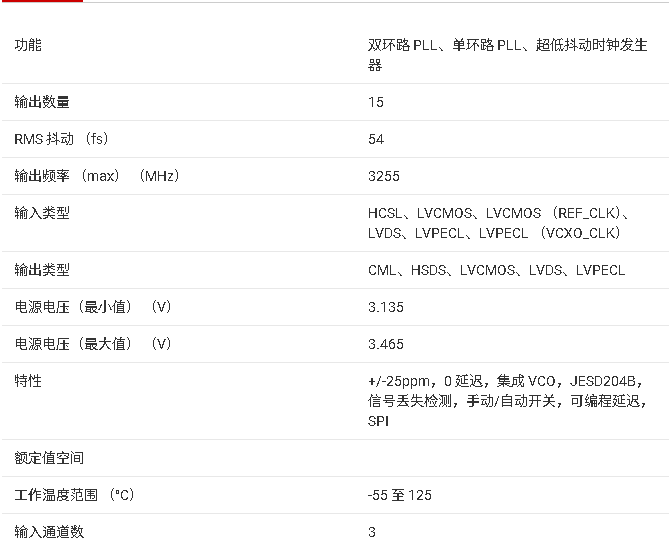

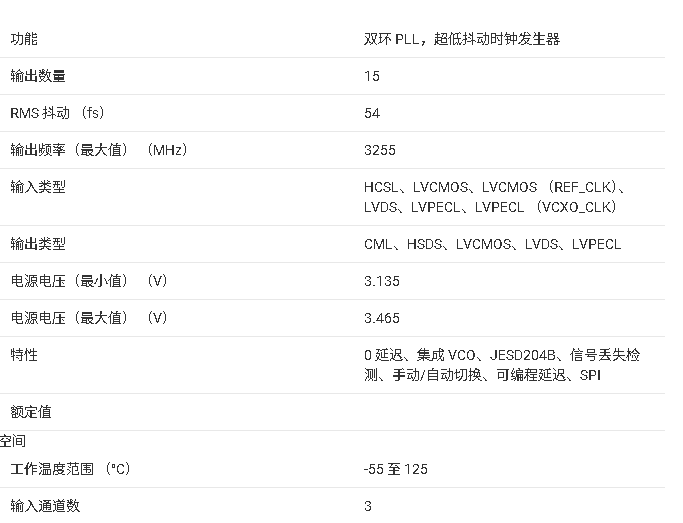

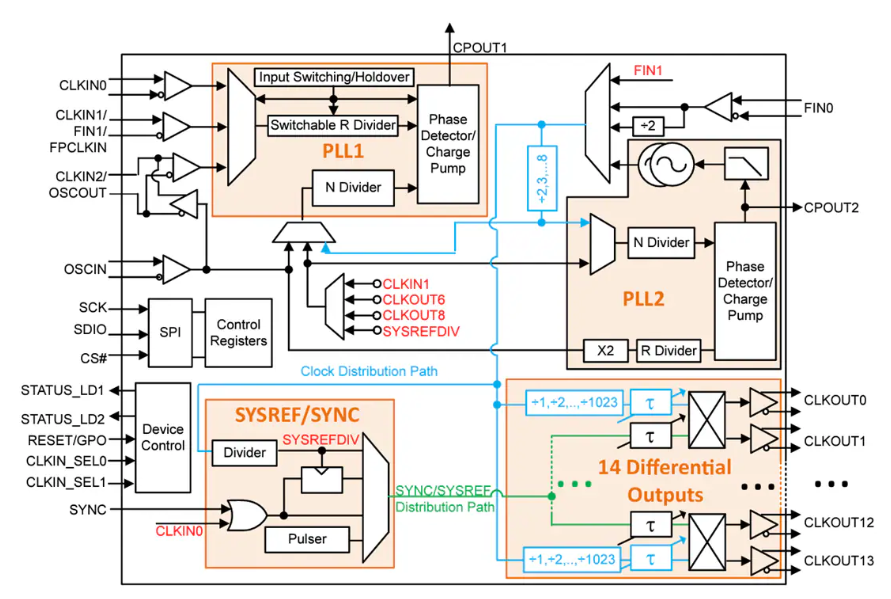

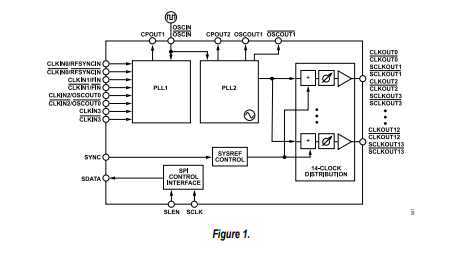

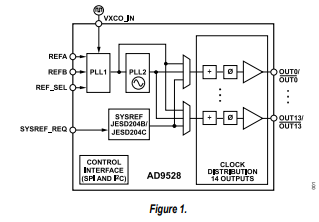

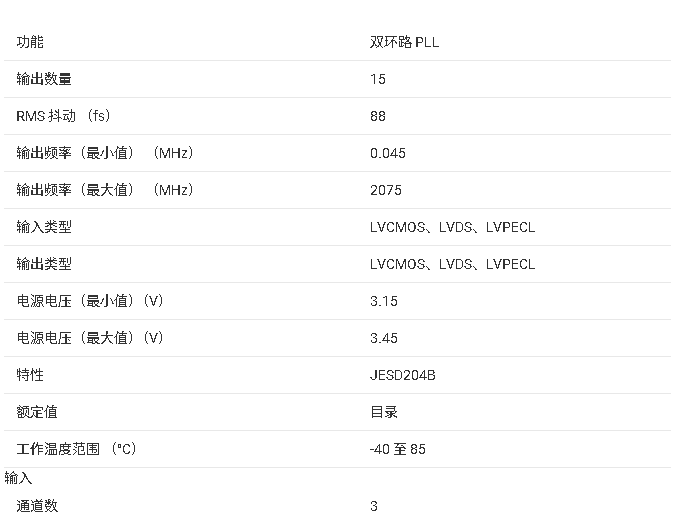

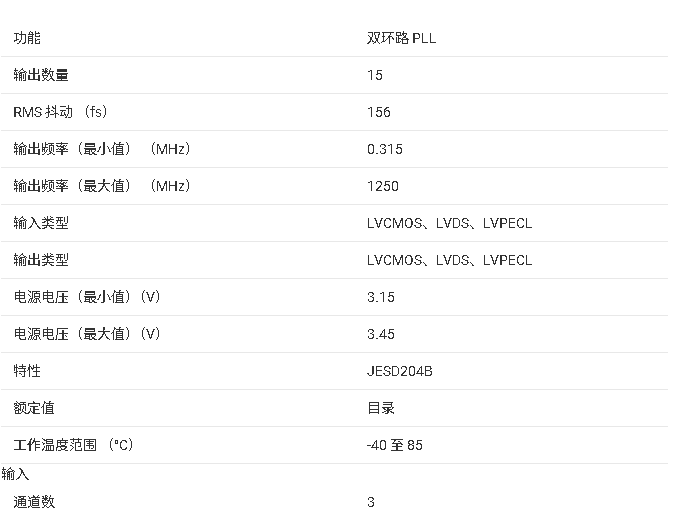

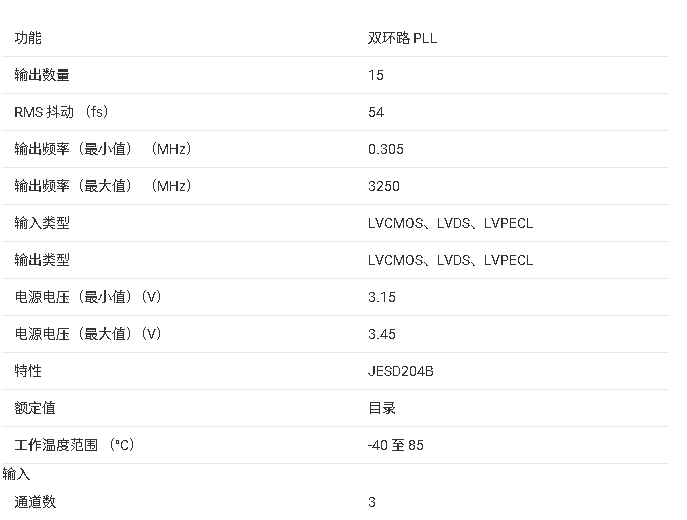

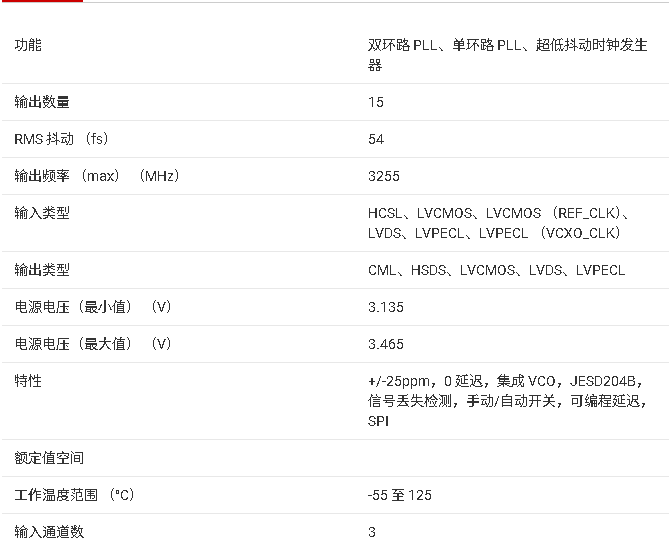

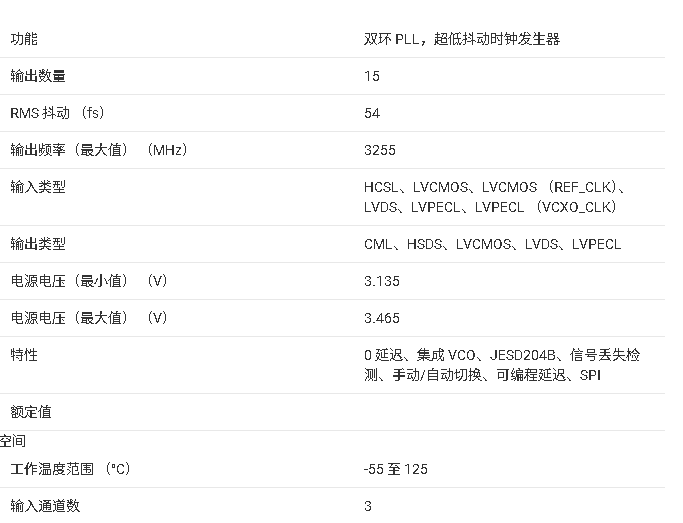

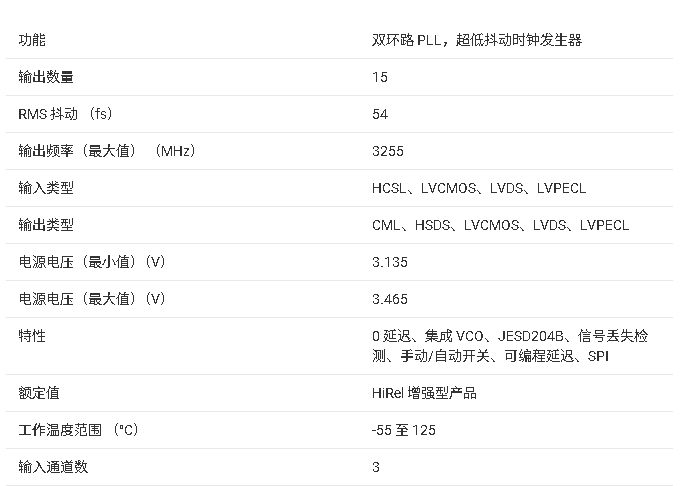

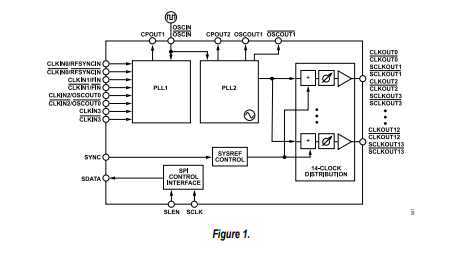

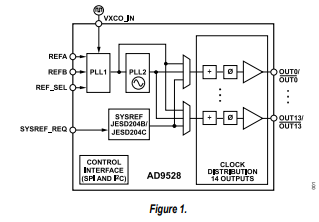

AD9528是一款雙級PLL,集成JESD204B SYSREF發生器,可用于多器件同步。

2025-10-15 10:24:53 1197

1197

,可能會造成感知不一致。所謂感知不一致,就是車上不同“眼睛”對同一件事看法不一致。打個比方,攝像頭說前面有個人,激光雷達回來的點云卻很稀疏,毫米波雷達也測到一個移動目標但不在同一個位置。這種感覺像是三個人各

2025-09-17 12:45:13 549

549

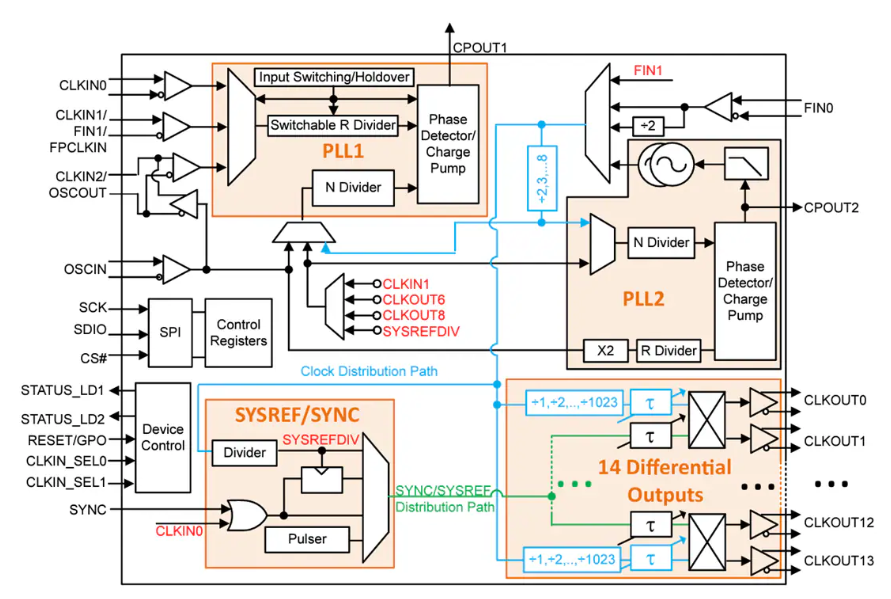

B 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

2025-09-15 10:10:11 848

848

B 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

2025-09-15 10:03:34 665

665

B 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

2025-09-14 11:07:35 901

901

LMK0461x 器件系列是業界性能最高、功耗最低的抖動清除器,支持 JESD204B。

2025-09-13 09:35:35 1028

1028

LMK0461x 器件系列是業界性能最高、功耗最低的抖動清除器,支持 JESD204B。16 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 8 個 JESD204B 轉換器或其他邏輯器件。第 17 個輸出可配置為提供來自 PLL2 的信號或來自外部 VCXO 的副本。

2025-09-12 16:50:34 907

907

。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

2025-09-12 16:13:11 831

831

。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

2025-09-12 15:02:13 611

611

該LMK04832是一款超高性能時鐘調節器,支持 JEDEC JESD204B,還與 LMK0482x 系列器件引腳兼容。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅動7個

2025-09-12 14:11:12 929

929

LMK04832-SP 是一款高性能時鐘調節器,支持 JEDEC JESD204B,適用于太空應用。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅動7個JESD204B轉換器或

2025-09-11 18:19:56 875

875

LMK04832-SEP 是一款高性能時鐘調節器,支持 JEDEC JESD204B/C,適用于太空應用。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅動7個JESD204

2025-09-11 10:43:33 649

649

LMK04368-EP 是一款高性能時鐘調節器,支持 JEDEC JESD204B/C,適用于太空應用。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個

2025-09-11 10:23:20 652

652

LMK04714-Q1 是一款高性能時鐘調節器,支持 JEDEC JESD204B/C,適用于太空應用。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個

2025-09-11 10:07:11 560

560

在機器視覺系統的視界,鏡頭一致性猶如維系整個生態的隱形生命線,貫穿于光學成像、圖像處理到智能決策的全鏈路,其細微波動足以顛覆整個檢測系統的可靠性。當工業界熱衷于討論算法精度與算力突破時,鏡頭這一基礎光學元件的一致性也是視覺工程師需要關注的重要環節。

2025-09-11 09:45:52 948

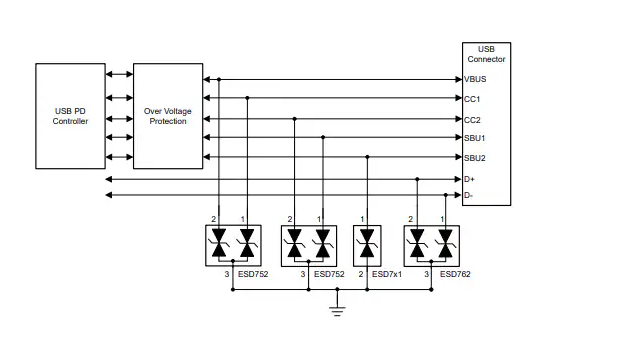

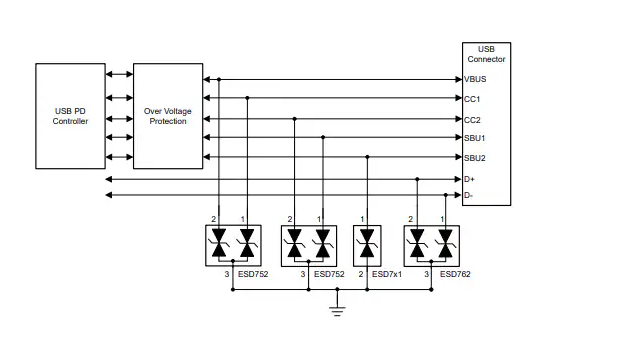

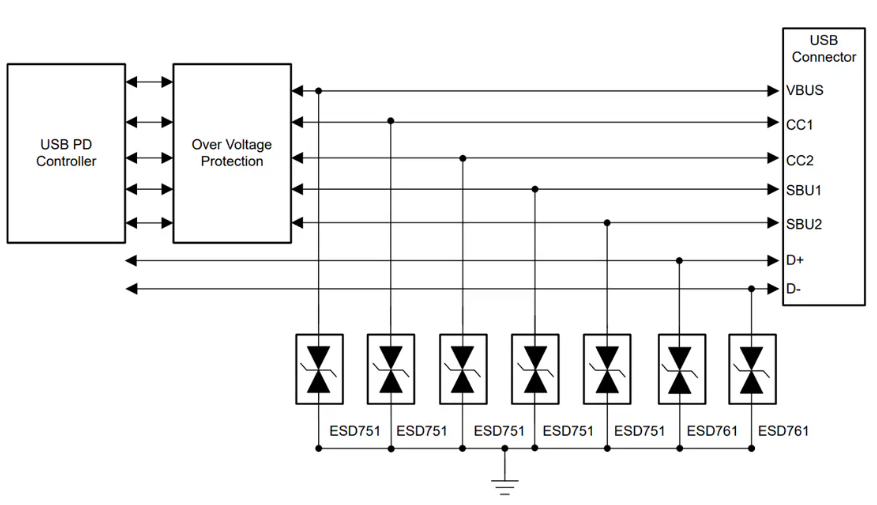

948 Texas Instruments ESD752和ESD762雙通道ESD保護二極管設計用于USB供電 (USB-PD) 和工業接口。ESD752和ESD762的額定接觸ESD達到或超過IEC

2025-09-07 17:41:31 938

938

硬限),優化多通道間的時序一致性(如子類1/2/3的同步協議)。

分布式轉換器功能

僅支持單轉換器器件(ADC/DAC功能集成于單一芯片)。

支持多轉換器器件分布式(如多片ADC協同采樣),需通過同步

2025-09-05 21:18:18

要驗證電能質量在線監測裝置備用電源續航測試方案的準確性,需從 方案設計合理性、測試過程可控性、結果一致性、標準符合性 等維度出發,通過多方法交叉驗證,確保測試結果能真實反映裝置在斷電場景下的實際續航

2025-09-03 17:42:49 648

648

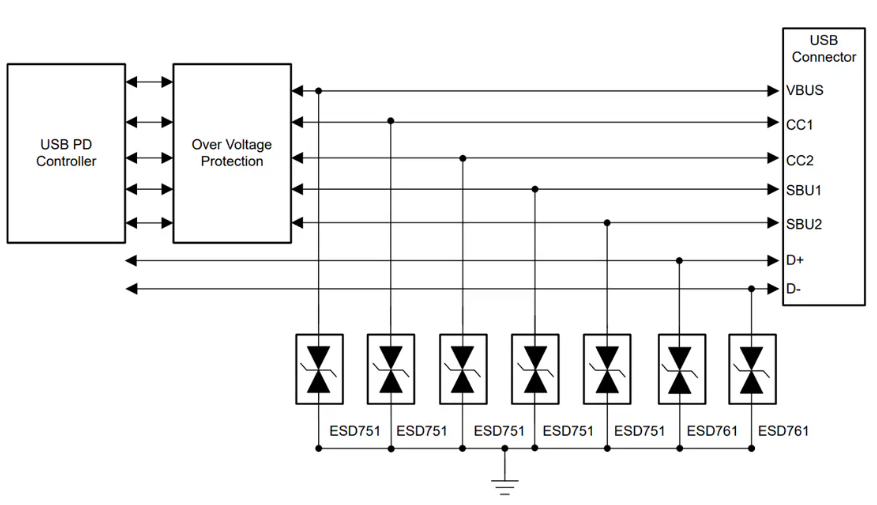

Texas Instruments ESD751/ESD751-Q1和ESD761/ESD761-Q1 ESD保護二極管是適用于USB電力輸送 (USB-PD) 的單通道低電容雙向ESD保護器

2025-09-02 09:30:26 838

838

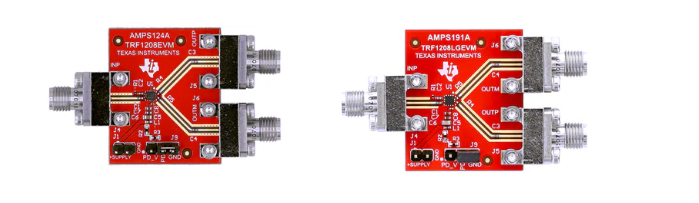

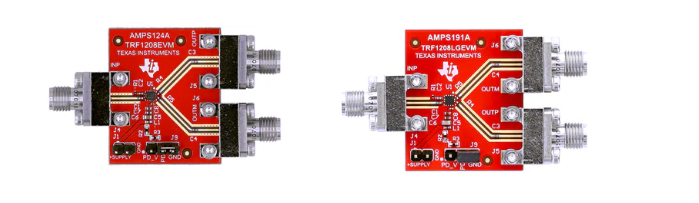

寬帶直接射頻采樣評估。 TRF1208評估模塊支持JESD204B/C,可實現同步和兼容性。這些評估模塊可在5.5V單輸入電壓下工作,包含完整的電源管理電路。TRF1208模塊具有JESD204B/C

2025-08-27 11:42:55 649

649

電池是現代生活中非常重要的能源供應設備。無論是手機、電腦,還是電動汽車和儲能電站,都離不開電池。電池的性能直接影響著設備的使用效果和安全性。在生產大量電池時,每一個電池的電壓、內阻等性能參數不可能

2025-08-25 17:26:12 457

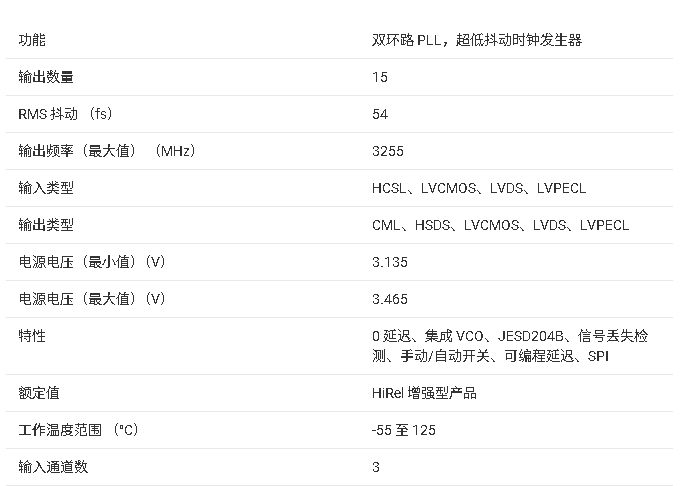

457 Texas Instrument LMK04714-Q1雙環時鐘抖動清除器是一款高性能時鐘調節器,支持JEDEC JESD204B/C,適用于航天應用。PLL2的每個14時鐘輸出均可配置為驅動七個

2025-08-08 15:05:57 843

843

的一致性片上網絡(NoC)IP——昉·星路-700(StarNoC-700)已成功適配賽昉科技昉·天樞(Dubhe)系列RISC-V處理器核心(Dubhe-70/83)

2025-07-24 09:02:50 1101

1101

德思特提供的Skydel仿真平臺提供靈活的GNSS信號功率配置方案,支持真實場景模擬和功率一致性測試兩種模式,通過GUI界面或API接口快速設置,滿足不同測試場景需求,助力衛星導航設備精準驗證。

2025-07-18 10:24:04 437

437

新興技術,以便幫助應對其當前PNT策略的脆弱性。自動駕駛汽車(AV)的制導與導航控制(GNC)系統就屬于這類技術,它必須能夠識別與PNT服務丟失或受損相關的一系列復雜威脅。

2025-07-11 15:49:30 1592

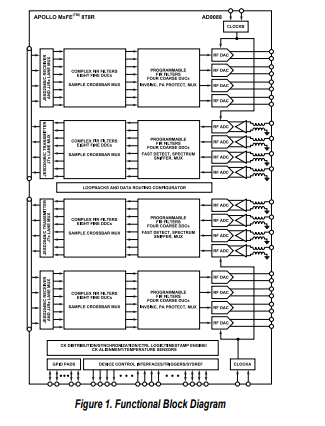

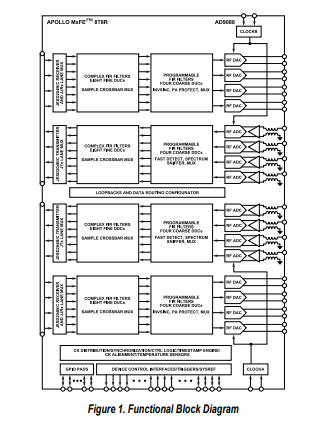

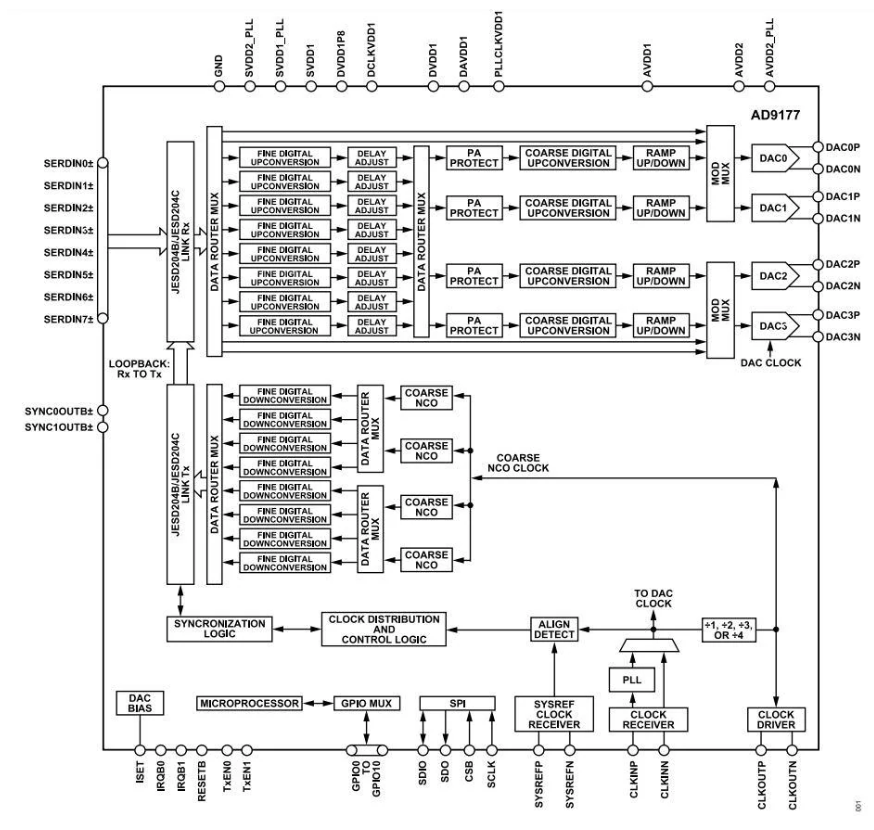

1592 和射頻數模轉換器 (DAC) 內核,支持多達八個基帶通道。該器件集成有8通道、24.75Gbps JESD204C或15.5Gbps JESD204B數據接收器 (JRx) 端口、片上時鐘倍頻器和數

2025-06-27 14:50:33 798

798

不斷地侵蝕著我們,面對這些劣質產品,可能一個細小的失誤就可能給企業造成巨大的財產損失或斷送了前程。材料一致性比對的應用領域來料檢驗:由供應商未通知客戶擅自改換原材料

2025-06-19 14:14:46 491

491

本文介紹FPGA與高速ADC接口方式和標準以及JESD204與FPGA高速串行接口。

2025-06-12 14:18:21 2880

2880

、遵循行業標準

CiA推薦采樣點為87.5%,并提供詳細的位定時指南(如CiA 601-3文檔)。工程師應參考這些標準,確保所有節點配置一致。

為確保網絡可靠性,工程師必須為所有節點配置一致的位定時

2025-06-07 08:55:26

時鐘和脈沖對準。與IC處理基準和SYSREF信號配合使用時,它支持JESD204B和JESD204C子類1解決方案。

2025-06-06 14:32:57 780

780

實用JESD204B來自全球數據轉換器市場份額領導 者的技術信息、提示和建議

2025-05-30 16:31:21 0

0 請教下大家怎樣配置CY7C68013A進入test packet mode 以可以進行眼圖一致性測試?怎樣配置相關寄存器?

2025-05-29 06:21:55

物理層的位置,一種是物理層在JESD204 IP里;另外一種是物理層在JESD204 IP外部,需要再配置JESD204 phy IP核進行使用。

2025-05-24 15:05:00 1827

1827

在CAN、CANFD信號波形不穩定或非理想環境下,采樣點不一致成為總線通信中的關鍵隱患,本文分析了采樣點偏移對總線的影響,并提出優化同步策略以提高通信可靠性,為總線設計提供重要參考。為什么采樣點如此

2025-05-19 11:44:07 953

953

字節,與預期值不一致。

eCamViewer 上的顯示問題:

使用Wireshark檢查數據傳輸,數據包已成功傳輸到主機。

但是,視頻沒有在eCamViewer上顯示,我懷疑幀和數據包大小差異(在第 1 點和第 2 點中提到)是導致顯示問題的原因。

2025-05-19 08:09:49

車用鋰離子電池機理建模與并聯模組不一致性研究

2025-05-16 21:02:17

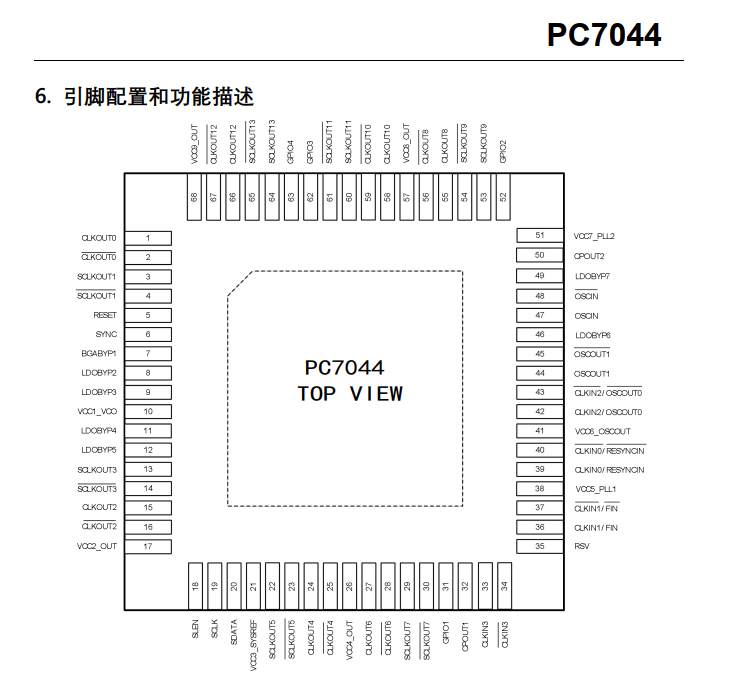

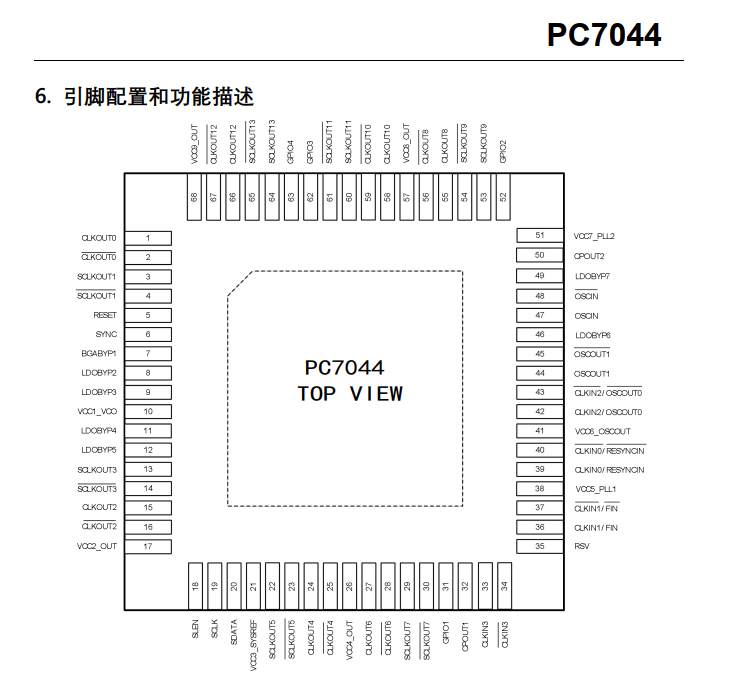

1.?概述 PC7044 是一款高性能雙環路的整數時鐘抖動消除器,可以為具有并行或串(JESD204B 型)接口的高速數據轉換器執行參考時鐘選擇和超低噪聲頻率的生成。?PC7044 具有兩個整數

2025-05-08 16:01:36 655

655

數字延遲,可在 14 個時鐘輸出通道中的每一個上獨立編程SPI 可編程相位噪聲與功耗SYSREF 有效中斷以簡化 JESD204B 同步窄帶雙核VCO最多 2 個緩沖壓控振蕩器(VCXO)輸出LVDS

2025-05-08 15:57:20

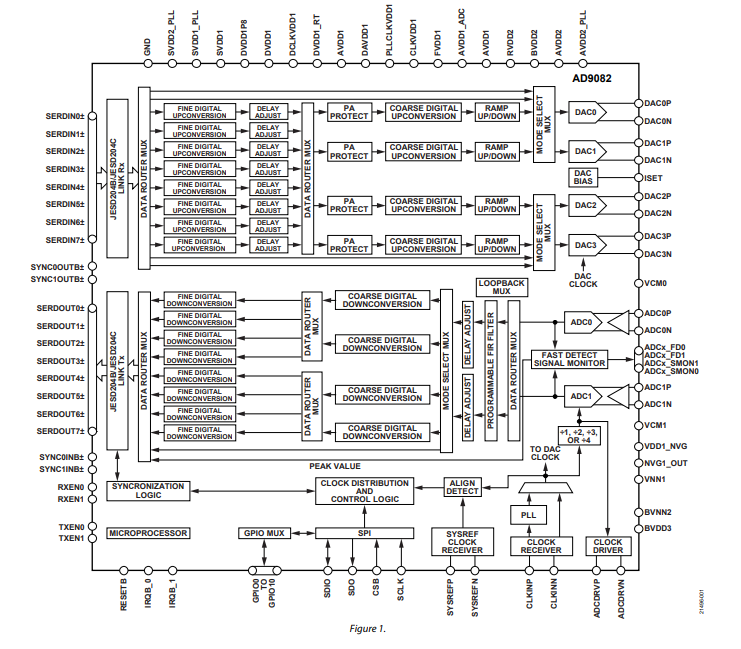

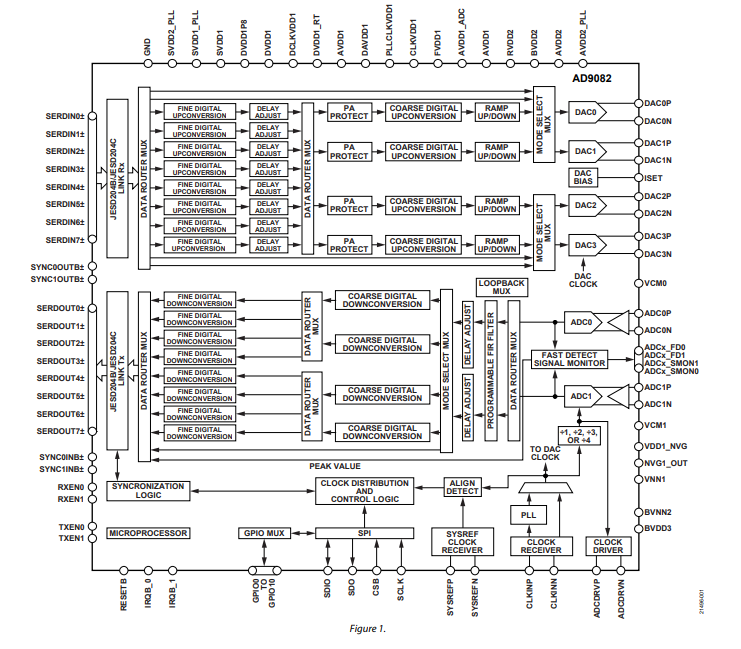

支持4個發射器通道和2個接收器通道。AD9082非常適合需要使用寬帶ADC和DAC來處理具有寬瞬時帶寬的信號的應用。該器件具有16通道、16.22 Gbps JESD204C或15.5 Gbps

2025-04-28 09:51:06 1123

1123

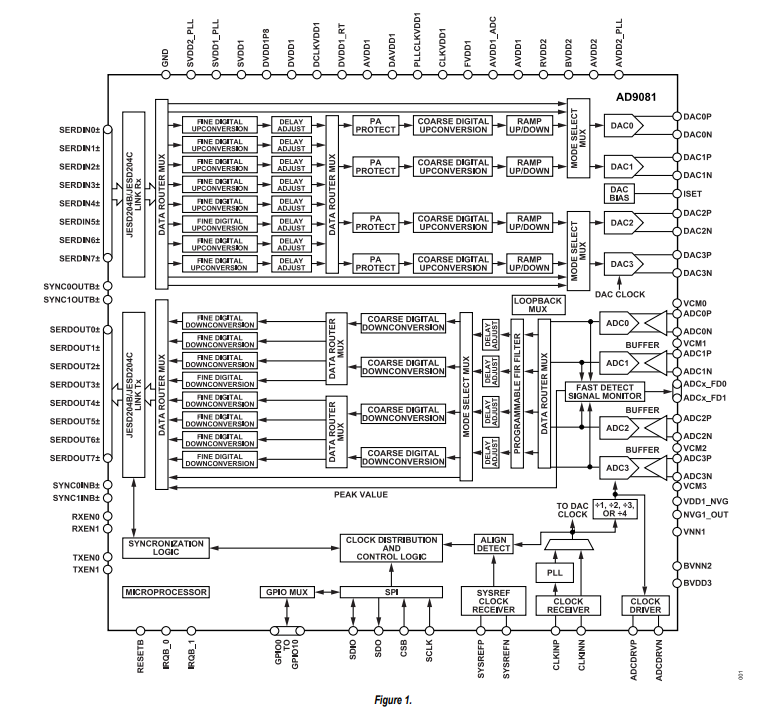

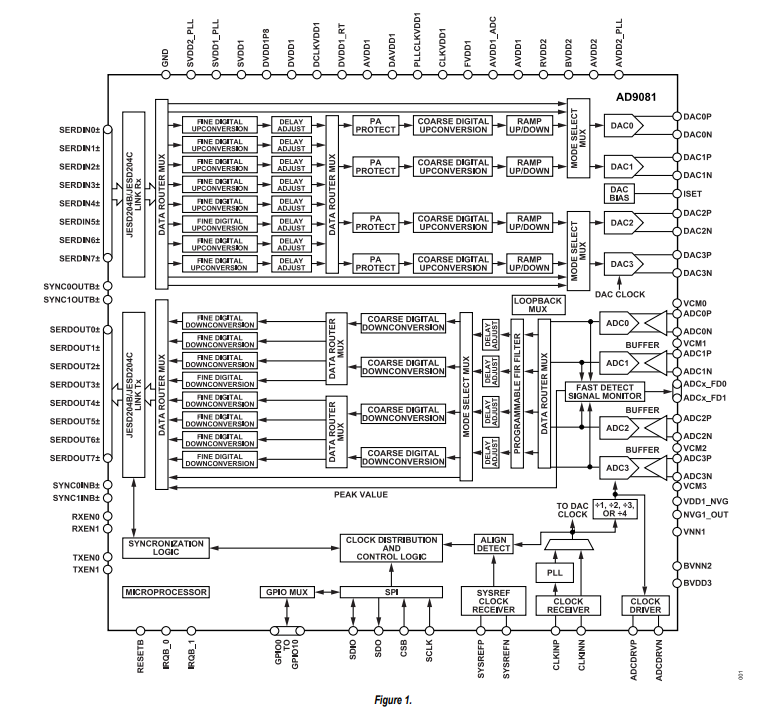

模數轉換器(ADC)內核。AD9081 非常適合需要寬帶 ADC 和 DAC 來處理具有寬瞬時帶寬信號的應用。該套件具有八個發送和八個接收通道,支持 24.75 Gbps/通道 JESD204C 或 15.5

2025-04-28 09:44:03 1128

1128

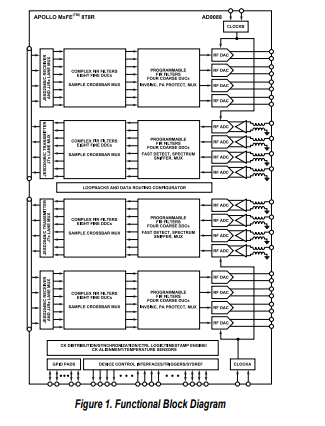

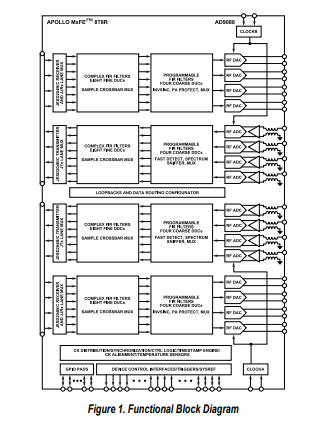

JESD204C 或 20 Gbps JESD204B 數據收發器端口、一個片上時鐘乘法器以及針對寬帶或多頻段、直接到 RF 應用的數字信號處理 (DSP) 功能。AD9088 還具有旁路模式,允許 ADC

2025-04-28 09:35:17 893

893

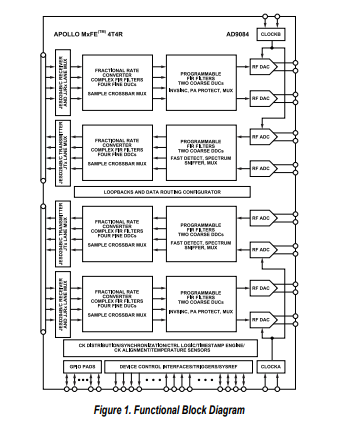

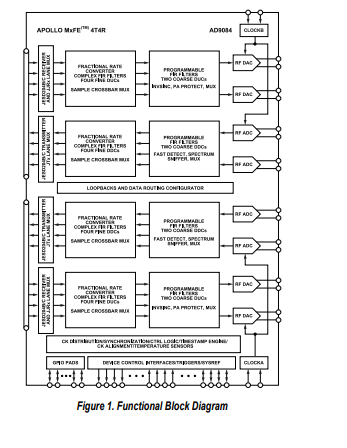

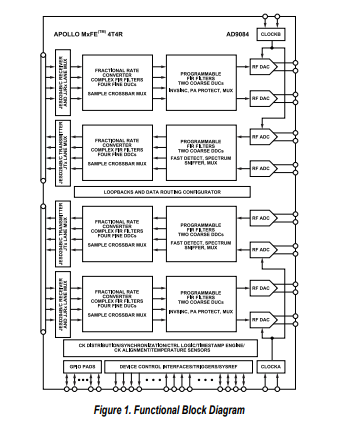

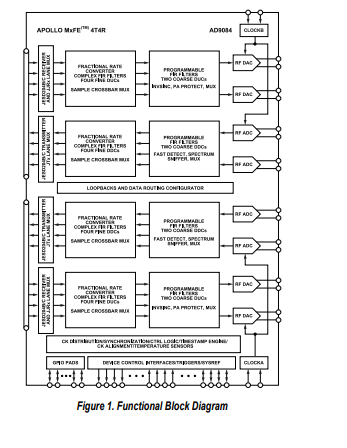

Gbps JESD204C 或 20 Gbps JESD204B數據收發器端口、片上時鐘乘法器以及針對寬帶或多頻段、直接到 RF 應用的數字信號處理 (DSP) 功能。AD9084 還具有旁路模式,允許

2025-04-28 09:32:20 1365

1365

及稀釋程度等關鍵參數對焊層質量有直接影響,實時監控熔池輪廓和溫度分布可及時預警缺陷并指導參數優化,以保證焊層一致性與工藝穩定性。今天一起了解堆焊熔池輪廓實時監控,實現工藝穩定性與焊縫一致性。 堆焊簡介 堆焊,又

2025-04-24 17:15:59 559

559

JESD204B是邏輯器件和高速ADC/DAC通信的一個串行接口協議,在此之前,ADC/DAC與邏輯器件交互的接口大致分為如下幾種。

2025-04-24 15:18:36 4481

4481

的應用。該套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 數據接收器 (JRx) 端口、片內時鐘乘法器和數字信號處理 (DSP) 數據通路,能夠處理

2025-04-18 17:22:55 1026

1026

JESD204C 或 20 Gbps JESD204B 數據收發器端口、一個片上時鐘乘法器以及針對寬帶或多頻段、直接到 RF 應用的數字信號處理 (DSP) 功能。AD9088 還具有旁路模式,允許 ADC

2025-04-18 15:58:18 1055

1055

JESD204C 或 20 Gbps JESD204B數據收發器端口、片上時鐘乘法器以及針對寬帶或多頻段、直接到 RF 應用的數字信號處理 (DSP) 功能。AD9084 還具有旁路模式,允許 ADC

2025-04-18 15:47:45 1770

1770

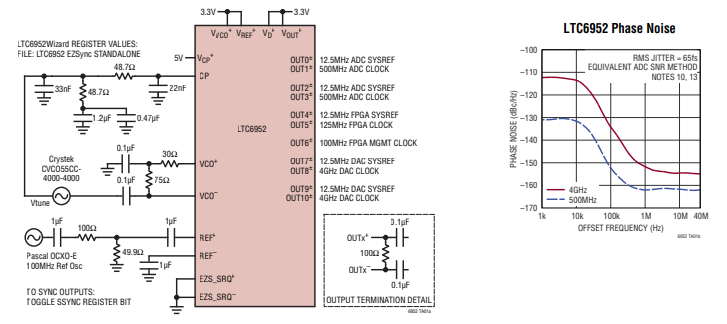

LTC6953 是一款高性能、超低抖動的 JESD204B/JESD204C 時鐘分配 IC。LTC6953 的 11 個輸出可配置為最多 5 個 JESD204B/JESD204C

2025-04-16 14:28:18 1023

1023

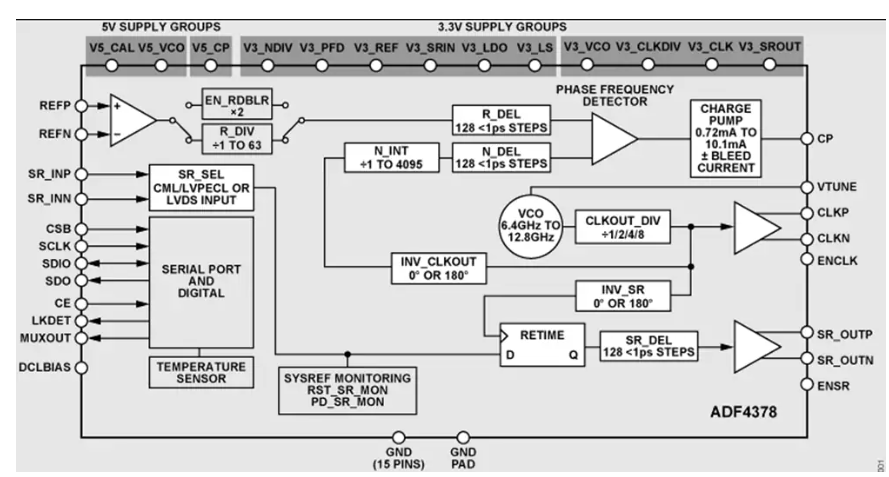

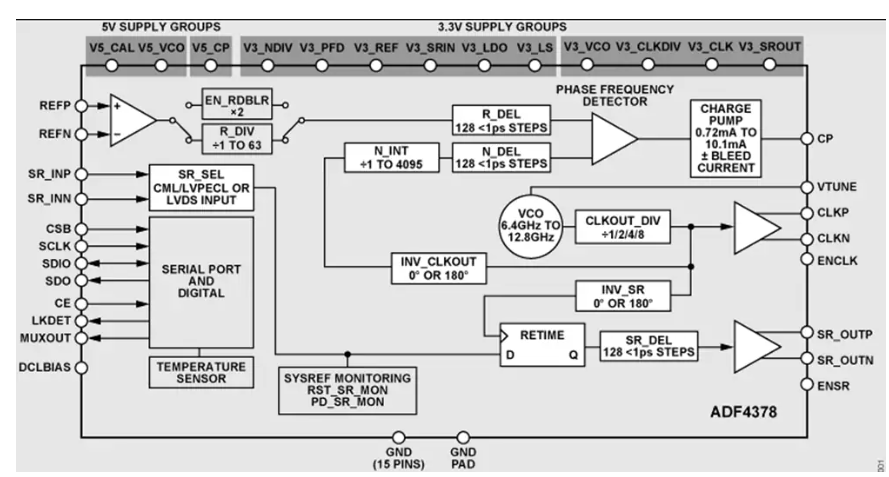

HMC7044B 是 [HMC7044]的修訂版本,是一款高性能、雙環路、整數 N 抖動衰減器,能夠為具有并行或串行(JESD204B 和 JESD204C 類型)接口的高速數據轉換器執行參考選

2025-04-16 11:27:05 1623

1623

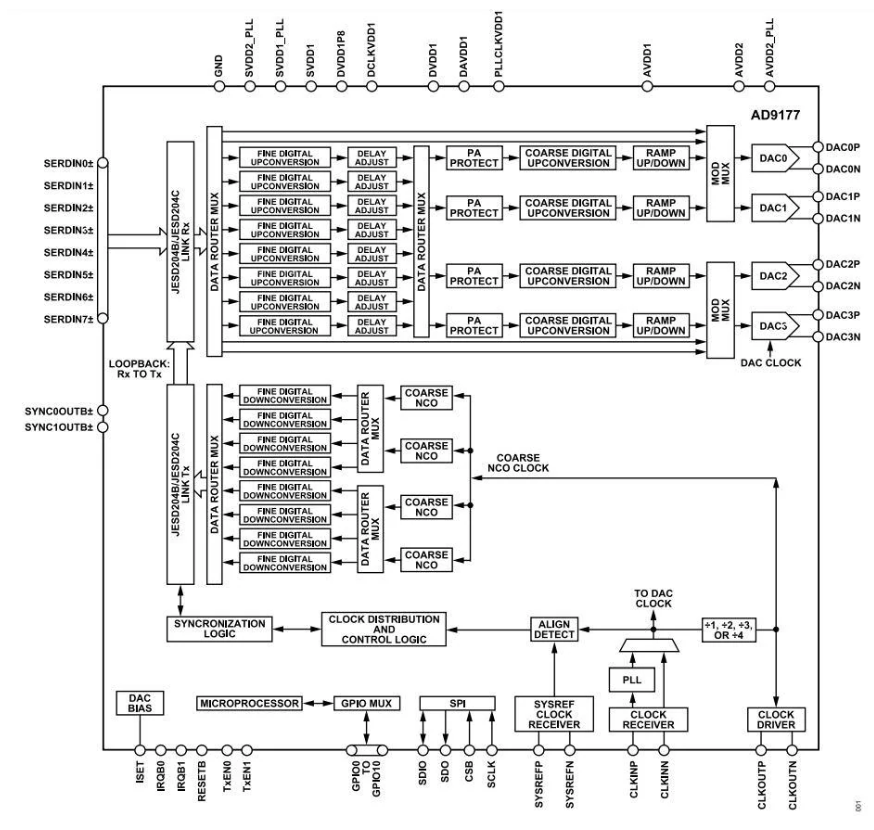

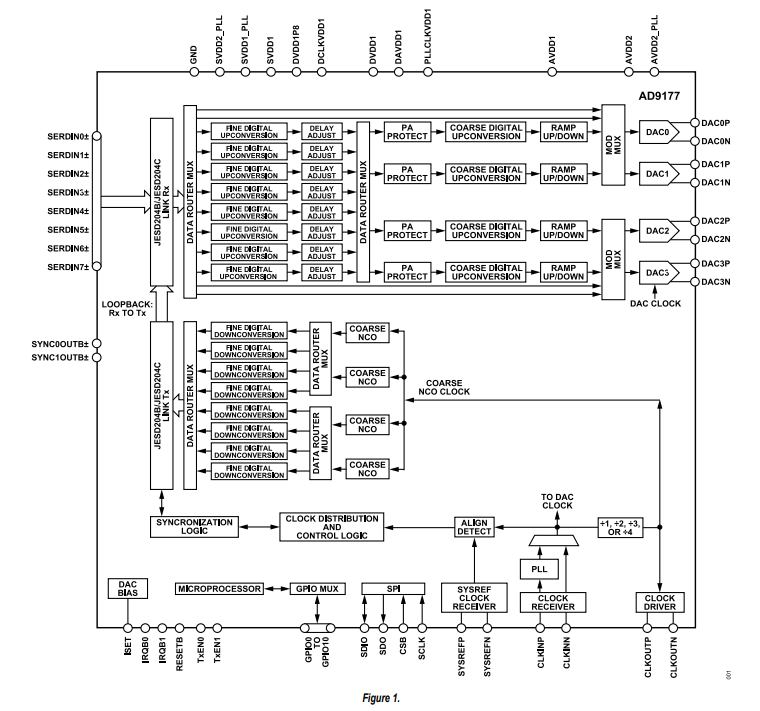

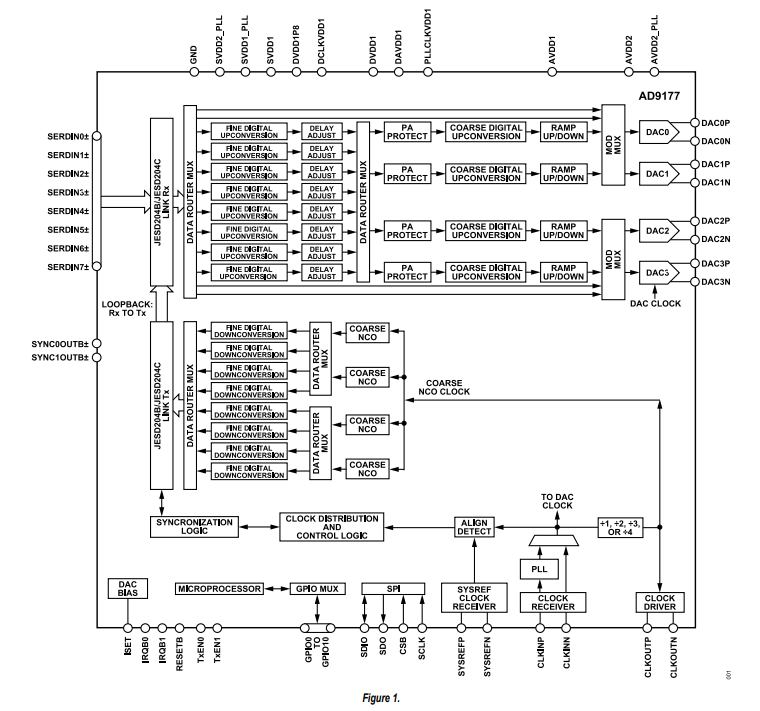

通過MICROBALZE配置AD9177,數據率9.6GSPS

輸入300MHz參考時鐘,內部倍頻至9.6GHz作為采樣時鐘,顯示PLL已鎖定

JESD204C 8個lane無法正常校驗成功,此時線速率是19.8Gbps;將其配置為9.9Gbps后lane正常

2025-04-15 07:09:14

AD采集芯片為AD9680-1000,時鐘芯片為AD9528。當 AD 采樣時鐘為 500MHz 時,jesd204B (串行線速 = 5 Gbps) 穩定。但是,當 AD 采樣時鐘為 800MHz

2025-04-15 06:43:11

電子發燒友網站提供《差一致性校正與邊緣融合拼接.pdf》資料免費下載

2025-04-10 18:02:03 0

0 AD9528是一款雙級PLL,集成JESD204B/JESD204C SYSREF發生器,可用于多器件同步。第一級鎖相環(PLL) (PLL1)通過減少系統時鐘的抖動,從而實現輸入基準電壓調理

2025-04-10 10:19:13 1141

1141

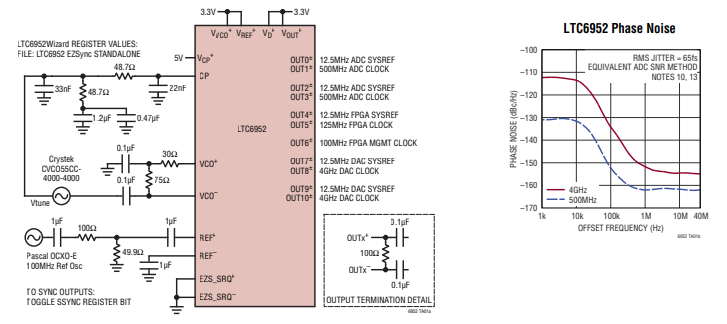

LTC6952 是一款高性能、超低抖動 JESD204B/C 時鐘生成和分配 IC。該器件包括一個鎖相環 (PLL) 內核,由基準分頻器、具有鎖相指示器的相位頻率檢波器 (PFD)、超低噪聲充電

2025-04-09 17:26:48 830

830

這是我的工程結構,其中jesd204部分在一開始運行綜合的時候就出錯了,報錯如下

* Synthesis

* synth_1

* [Synth 8-6104] Input port

2025-03-12 22:21:51

YOLOv5類中rgb888p_size這個參數要與模型推理和訓練的尺寸一致嗎,一致會達到更好的效果

2025-03-11 08:12:30

羅德與施瓦茨(以下簡稱“R&S”)的R&S TS8980FTA-M1 5G一致性測試系統率先通過了測試平臺認證標準(TPAC),隨即全球認證論壇(GCF)最新的無線資源管理(RRM

2025-02-28 17:22:45 1315

1315

目前發現的問題是當我們雙通道采樣的時候,雙通道增益不一致的時候,

有一路采樣溢出,一路沒有溢出的情況下,沒有溢出的那一路采樣會出現

大范圍的跳動,且沒有規律。

雙通道,兩路差分輸入,然后對應

2025-02-13 06:45:44

配置寄存器寫進去與讀出來的數據是一致的,但是數據只是通道0的數據

2025-02-12 06:08:58

近期,炬光科技股份有限公司作為全球領先的高功率半導體激光器及原材料、激光光學、光子應用模塊與系統解決方案的提供商,宣布了一項重要戰略舉措。為了進一步深化品牌一致性戰略,炬光科技的全資子公司

2025-02-10 11:08:54 922

922 其實使用到ADI的東西,基本也就沒有太去關注協議這些東西,只是簡簡單單的有個了解就行,在實際調試的時候,用的也是Xilinx的評估版的JESD的IP,基本不需要自己做什么工作就能夠把整個系統運行起來了。

2025-02-08 13:45:55 3990

3990

請問各位大俠:JESD204B專用于ADC/DAC和FPGA或ASIC的接口嗎,該接口同Rapid/PCIe的物理層Serdes接口有何區別,謝謝!

2025-02-08 09:10:29

CARLEN 磁致伸縮位移傳感器在鋼廠熱軋設備中的應用:在鋼廠熱軋環節,CARLEN 磁致伸縮位移傳感器可用于監測軋機軋輥的位置,精確控制軋輥間距,確保鋼材軋制厚度的一致性;也能應用于熱軋生產線中各種液壓缸活塞位置的反饋,保證設備動作的準確性和穩定性 ,從而提升熱軋生產的效率和產品質量。

2025-02-06 13:46:33 909

909

各位專家好!這邊想選擇一款能夠實現多個通道數據采集的ADC,由于對通道間的幅度和相位一致性要求較高,最好可以嚴格控制各通道之間的同步,要求單個通道的吞吐量為1MSPS以上,SNR最好在90dB以上

2025-01-24 08:28:24

100。考慮到兩個通道的幅度一致性,在保證參考電路中兩個25歐姆電阻的和不變的同時,調整其電阻比例。但是通道2的idle noise基本不變。有沒有什么辦法能夠調整通道2的空采偏置呢?

2025-01-24 06:41:18

老師,我用ADS1298在進行內部信號測試(1HZ)時為什么各個通道的零點都不一致呢,并且明顯都漂到y=0軸以上了,以至于每次我在測心電信號時都需要重新調整坐標Y軸的值

2025-01-23 07:49:35

采用2片ADS8345采集多路傳感器信號得到的各個通道數據精度不一致,有的噪聲大的驚人有0.03V,有的噪聲在0.0008V左右,SPI通訊速率2.25M

2025-01-17 06:26:18

我們使用的是文獻[21, 18, 20]中報道的 SOA 模型,該模型與文獻[3]中的 pumpprobe 實驗結果具有良好的一致性。

2025-01-16 15:08:40 914

914

個模擬通道)。我們還需要測試夾具:是德的N7015A和N7018A控制器,和一個DP的控制器:UNIGRAF的DPR-100。整體連接:夾具N7015A的Tx1的

2025-01-15 17:33:51 1871

1871

請問一下ADS1298的8個通道的基線應該一致嗎?

2025-01-15 07:08:57

讀取手冊,發現要保證多片AD1278的通道之間相位一致性需要兩點:1、CLK一致;2、SYNC_N同時拉高。

我的情況:

1、各個AD1278的CLK來著不同的時鐘源,即分別采用10ppm

2025-01-14 06:02:23

大家好,近來接觸JESD204B接口協議,采用SUBCLASS1方案,在系統設計上遇到諸多問題。首先SYSREF和DEVICE CLK 一般有不同的電氣特性,一個可能是TTL的,另一個是CML

2025-01-10 07:25:47

最近在使用JESD204B協議,遇到一下問題。我使用的是FPGA與DAC38J84。

1:有關SYSREF時鐘問題,DAC的時鐘為1.2GHz, FPGA中JESD204B IP核配置為發射

2025-01-06 08:08:15

電子發燒友App

電子發燒友App

評論