1.概述

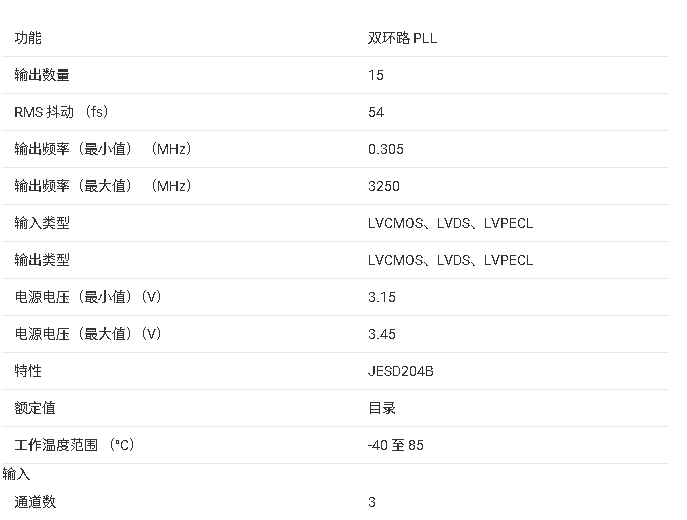

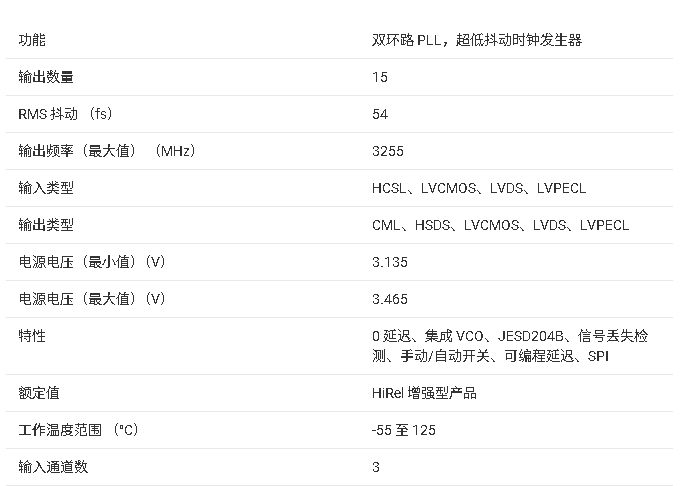

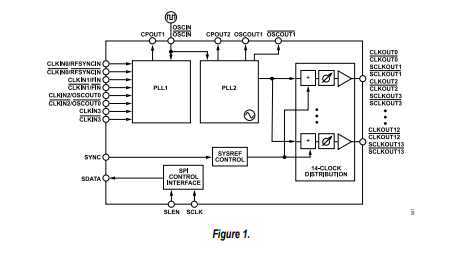

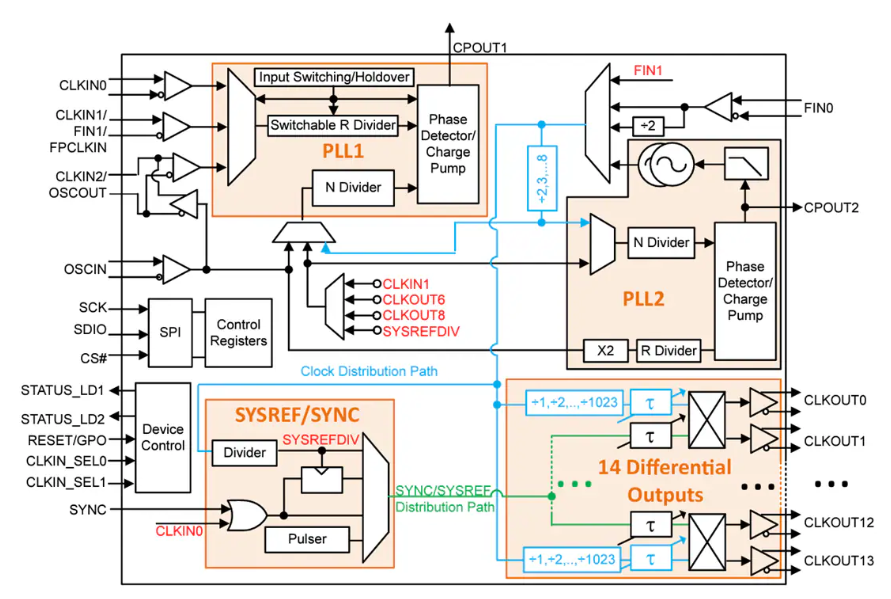

PC7044 是一款高性能雙環路的整數時鐘抖動消除器,可以為具有并行或串(JESD204B 型)接口的高速數據轉換器執行參考時鐘選擇和超低噪聲頻率的生成。PC7044 具有兩個整數模式的PLL 和重疊的片上VCO,具有較寬的調諧范圍,SPI 可選。該設備旨在滿足GSM 和LTE 基站設計的要求,并提供寬范圍的時鐘管理和分配功能,用來簡化基帶和無線網卡時鐘樹設計。PC7044 采用QFN68 封裝,提供14 個低噪聲和可配置的輸出,用來提供與許多不同組件接口的靈活性,包括數據轉換器、現場可編程門陣列(FPGA)和混頻器本地振蕩器(LO)。

2.特性

超低 RMS抖動: 80fs RMS Jitter (12kHz到 20MHz) @245.76 MHz

底噪: -161dBc/Hz@245.76 MHz

PLL2可提供多達 14路 LVDS、 LVPECL或 CML類型的設備時鐘(DCLK)

最大 CLKOUT/CLKOUTx和 SCLKOUT/SCLKOUTx頻率高達 3200MHz

JESD204B兼容系統參考時鐘(SYSREF)脈沖

25ps模擬和?VCO周期數字延遲,可在 14個時鐘輸出通道中的每一個上獨立編程

SPI可編程相位噪聲與功耗

SYSREF有效中斷以簡化 JESD204B同步窄帶雙核VCO

最多 2個緩沖壓控振蕩器(VCXO)輸出

LVDS、 LVPECL、 CMOS和 CML模式下最多 4個時鐘輸入

保持輸出頻率的頻率保持模式

信號丟失(LOS)檢測和無瞬斷參考時鐘切換

4個 GPIO報警/狀態指示器,用于確定系統的健康狀態

外部 VCO輸入,支持高達 3200MHz

車載調節器可實現出色的電源抑制比

3.應用

? JESD204B時鐘生成

?蜂窩基礎設施(多載波 GSM、 LTE、 W-CDMA)

?數據轉換器時鐘

?微波基帶卡

?相控陣參考時鐘分布

審核編輯 黃宇

-

轉換器

+關注

關注

27文章

9418瀏覽量

156332 -

SPI

+關注

關注

17文章

1885瀏覽量

101214 -

消除器

+關注

關注

0文章

59瀏覽量

9115

發布評論請先 登錄

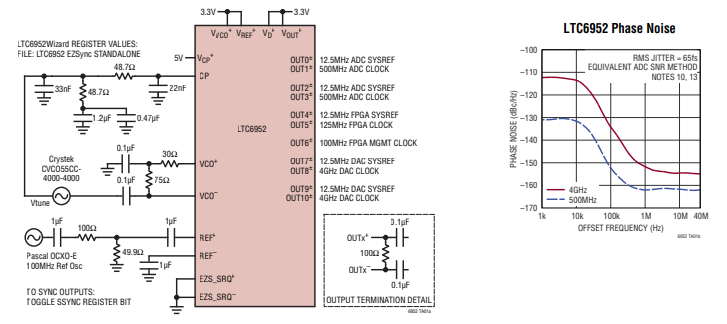

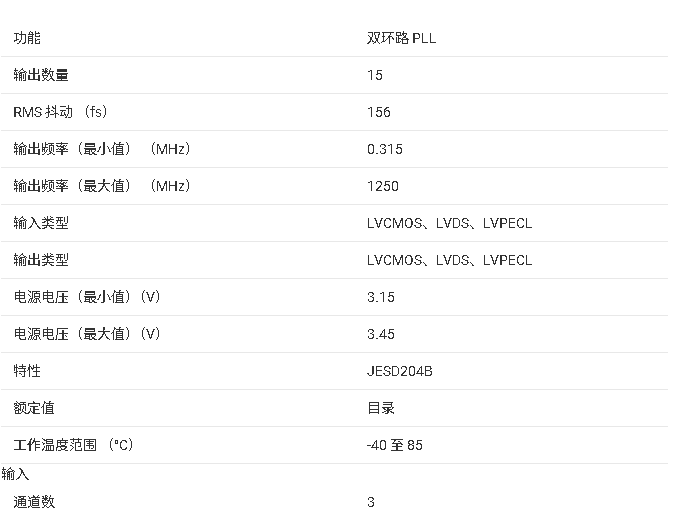

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

?LMK04368-EP 超低噪聲JESD204B/C雙環路時鐘抖動清除器總結

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

PC7044高性能時鐘抖動消除器支持JESD204B 時鐘生成

PC7044高性能時鐘抖動消除器支持JESD204B 時鐘生成

評論