概述

LTC6953 是一款高性能、超低抖動的 JESD204B/JESD204C 時鐘分配 IC。LTC6953 的 11 個輸出可配置為最多 5 個 JESD204B/JESD204C subclass 1 器件時鐘 / SYSREF 對以及一個通用輸出,或者就是 11 個面向非 JESD204B/JESD204C 應用的通用時鐘輸出。每個輸出都有自己的可個別編程分頻器和輸出驅動器。所有輸出也可以采用個別的粗略半周期數字延遲和精細模擬時間延遲實現同步,并設定為精確的相位對齊。

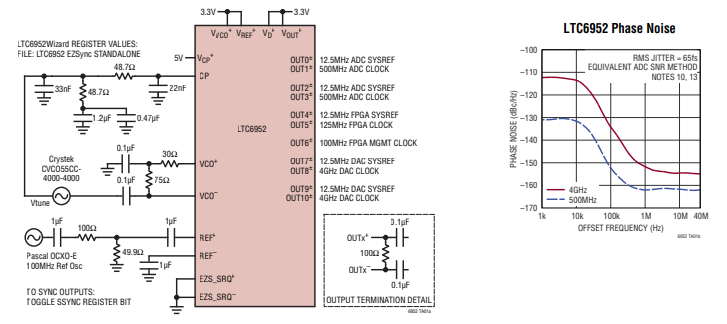

對于需要 11 個以上總輸出的應用,可以使用 EZSync 或 ParallelSync 同步協議將多個 LTC6953 與 LTC6952 和 LTC6955 連接在一起。

數據表:*附件:LTC6953具有11個輸出并支持JESD204B JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊.pdf

應用

- 高性能數據轉換器時鐘

- 無線基礎設施

- 測試和測量

特性

- JESD204B/JESD204C,子類 1 SYSREF 信號生成

- 附加輸出抖動 < 6fs

RMS(集成帶寬 = 12kHz 至 20MHz,f = 4.5GHz) - 附加輸出抖動 65fs

RMS(ADC SNR 方法) - EZSync ^?^ 、ParallelSync^?^ 多芯片同步

- 11 個獨立低噪聲輸出,具有可編程粗數字延遲和精細模擬延遲

- 靈活的輸出可以用作套件時鐘或 SYSREF 信號

- LTC6952Wizard 軟件設計工具支持

- 工作溫度范圍為 –40°C 至 125°C

應用電路

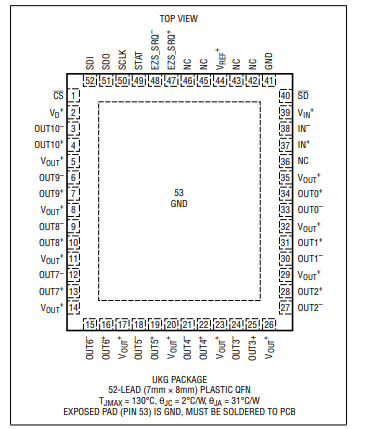

引腳配置描述

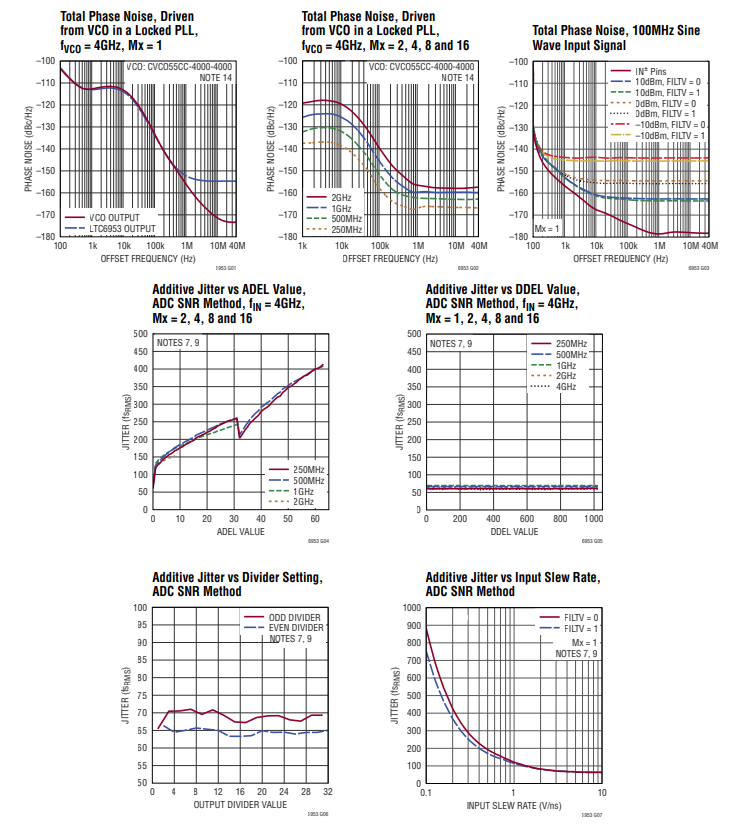

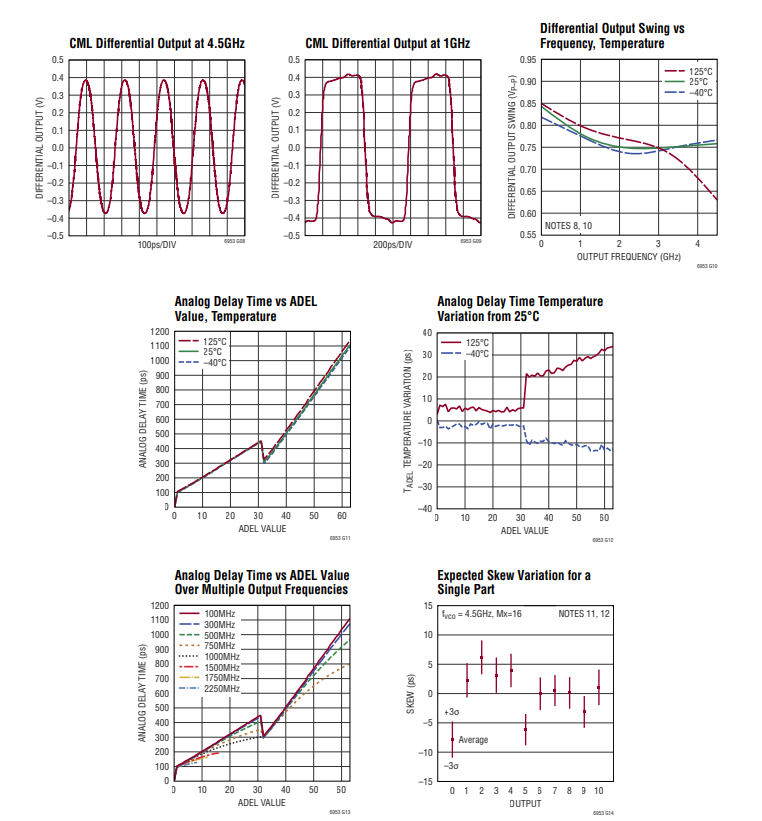

典型性能特征

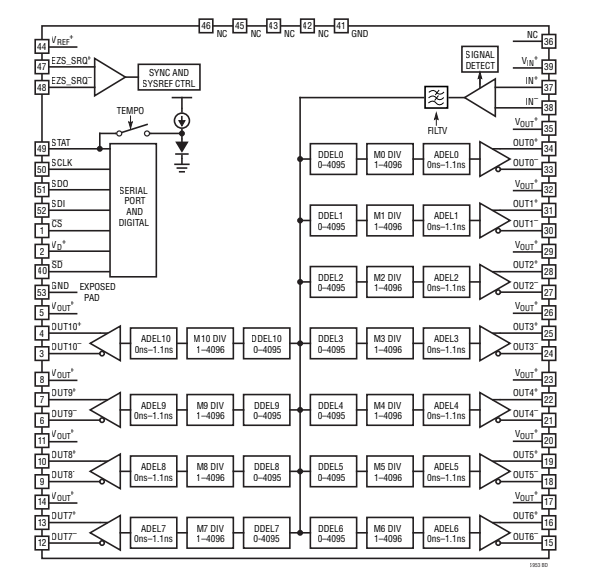

框圖

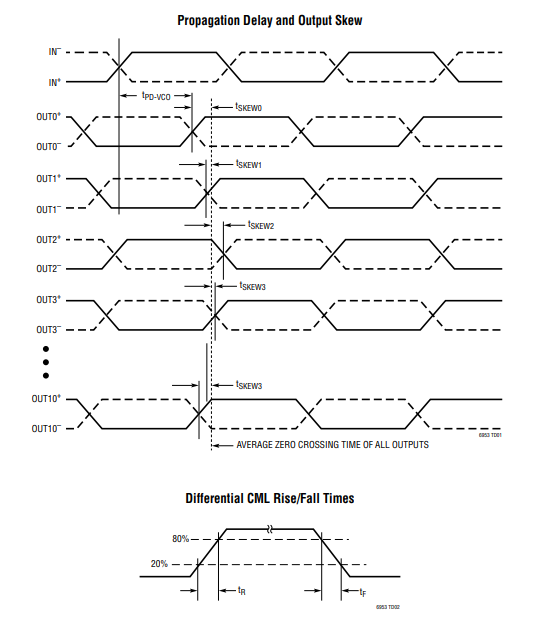

時序圖

操作

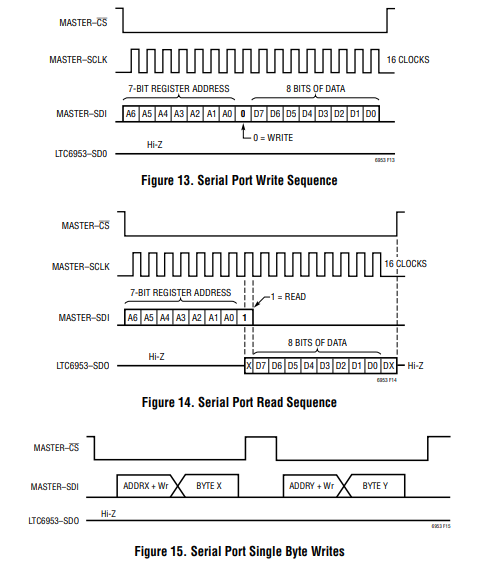

第一個字節的高7位是寄存器地址,最低有效位(LSB)為“1”表示從器件讀取數據 ,LSB為“0”表示向器件寫入數據。隨后的一個或多個字節是來自或寫入指定寄存器的地址數據。圖13為詳細寫序列示例,圖14為讀序列示例。

圖15展示了兩次寫通信突發的示例。第一次突發的第一個字節包含來自串行總線主機的目標寄存器地址(ADDRX),LSB為“0”表示寫操作。下一個字節是要寫入ADDRX寄存器的數據。隨后將片選信號(CS)拉高,以終止傳輸。第二次突發的第一個字節包含目標寄存器地址(ADDRY),LSB指示寫操作。串行數據輸入(SDI)上的下一個字節是要寫入ADDRY寄存器的數據。然后將CS拉高,以終止傳輸。

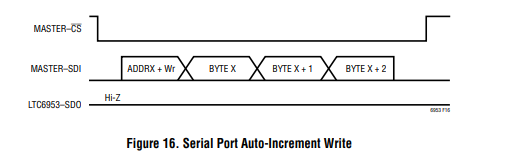

多字節傳輸

如圖16所示,利用LTC6953的寄存器地址自動遞增功能,可實現更高效的多字節數據傳輸。串行端口主機先發送目標寄存器地址,第一個字節按常規方式寫入數據 ,第二個字節及后續字節也按此方式操作。

并繼續發送后續寄存器的數據字節。第一個字節的地址為ADDRX + 1,第二個字節的地址為ADDRX + 2,依此類推。如果寄存器地址指針試圖遞增超過56(十六進制h38 ),它會自動重置為0。

圖17展示了從器件自動遞增讀取的示例。第一次突發的第一個字節包含來自串行總線主機的目標寄存器地址(ADDRX),最低有效位(LSB)為“1”表示讀操作。LTC6953檢測到讀突發后,將數據從其高阻抗(Hi-Z)狀態輸出到串行數據輸出(SDO),并順序發送多個字節,從ADDRX寄存器的數據開始。在突發結束前,器件會忽略串行數據輸入(SDI)上的所有其他數據。

多點配置

多個LTC6953器件可以共享串行總線。在這種多點配置中,所有器件的串行時鐘(SCLK)、串行數據輸入(SDI)和串行數據輸出(SDO)都是共用的。串行總線主機必須為每個器件使用單獨的片選信號(CS),并確保在任何時候只有一個器件的CS被置為有效。建議連接一個高阻值電阻到SDO,以確保在高阻抗狀態下線路能回到已知電平。

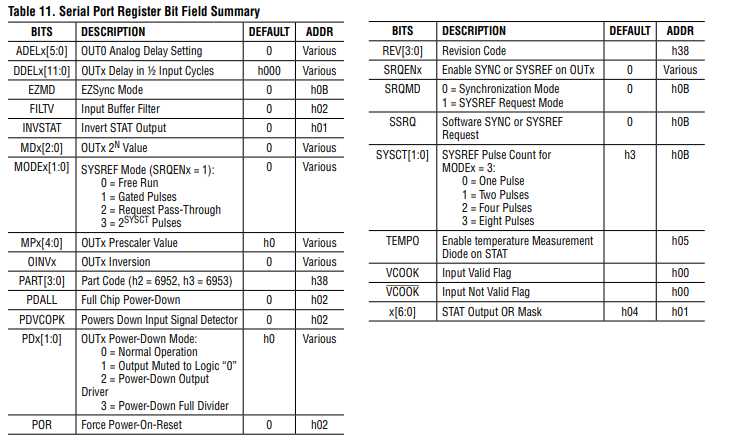

串行端口寄存器

LTC6953的內存映射見表10,詳細的位描述見表11。寄存器地址列以十六進制格式顯示,在“ADDR”下。每個寄存器標記為只讀(R)或讀寫(RW)。寄存器的默認值在器件上電或復位后顯示。

地址為h00的只讀寄存器用于確定不同的狀態標志。這些標志可通過配置狀態寄存器h01立即輸出到STAT引腳。有關更多信息,請參見“輸出”部分。

地址為h38的寄存器是一個用于器件識別的只讀字節。

-

時鐘

+關注

關注

11文章

1993瀏覽量

135117 -

分配器

+關注

關注

0文章

213瀏覽量

27397 -

JESD204B

+關注

關注

6文章

83瀏覽量

19918

發布評論請先 登錄

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

JESD204B串行接口時鐘的優勢

JESD204C的標準和新變化

如何采用系統參考模式設計JESD204B時鐘

JESD204B協議介紹

LTC6953 具有 11 個輸出并支持 JESD204B/JESD204C 協議的超低抖動、4.5GHz 時鐘分配器

LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持數據表

LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個輸出和JESD204B/JESD204C支持數據表

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

從JESD204B升級到JESD204C時的系統設計注意事項

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

評論