LMK0482x 系列是業界性能最高的時鐘調節器,支持 JEDEC JESD204B。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個 JESD204B 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

LMK0482x 系列具有高性能,加上在功率或性能之間權衡的能力、雙 VCO、動態數字延遲、保持和無毛刺模擬延遲等功能,是提供靈活的高性能時鐘樹的理想選擇。

*附件:lmk04826.pdf

特性

- JEDEC JESD204B支持

- 超低 RMS 抖動

- 88 fs RMS 抖動(12 kHz 至 20 MHz)

- 91 fs RMS 抖動(100 Hz 至 20 MHz)

- 245.76 MHz時–162.5 dBc/Hz本底噪聲

- PLL2 提供多達 14 個差分器件時鐘

- PLL1 多達 1 個緩沖 VCXO/晶體輸出

- LVPECL、LVDS、2xLVCMOS 可編程

- 雙環路PLLatinum? PLL架構

- PLL1

- 多達 3 個冗余輸入時鐘

- 自動和手動切換模式

- 無中斷開關和LOS

- 集成低噪聲晶體振蕩器電路

- 輸入時鐘丟失時的保持模式

- 多達 3 個冗余輸入時鐘

- PLL2

- 歸一化 [1 Hz] PLL 本底噪聲為

–227 dBc/Hz - 相位檢測器速率高達 155 MHz

- OSCin 倍頻器

- 兩個集成低噪聲VCO

- 歸一化 [1 Hz] PLL 本底噪聲為

- 50% 占空比輸出分頻,1 至 32

(偶數和奇數) - 精密數字延遲,動態可調

- 25 ps 步進模擬延遲

- 多模:雙 PLL、單 PLL 和時鐘分配

- 工業溫度范圍:–40 至 85°C

- 支持 105°C PCB 溫度(在導熱墊處測量)

- 3.15V 至 3.45V 工作電壓

- 封裝:64引腳QFN(9.0 mm × 9.0 mm × 0.8 mm)

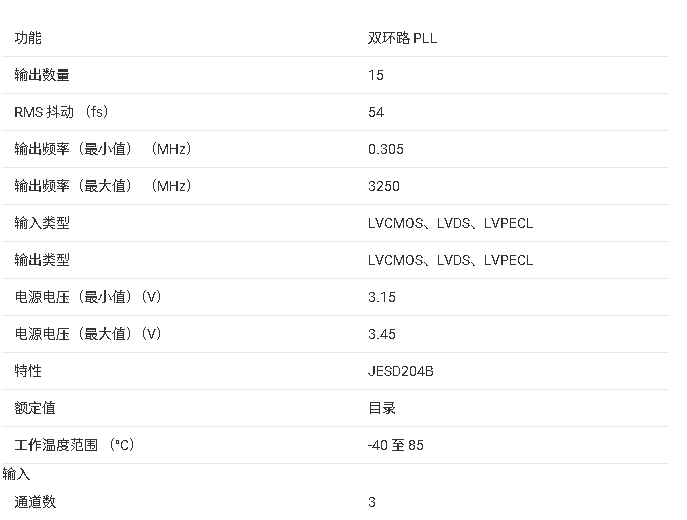

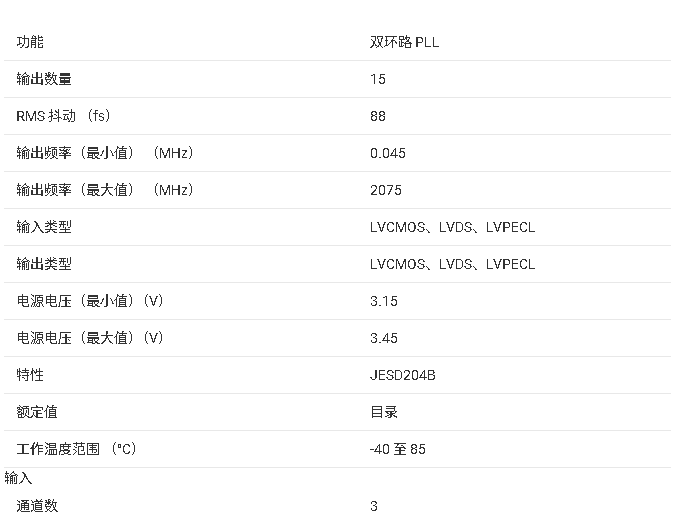

參數

?1. 產品概述?

LMK0482x系列(包括LMK04821、LMK04826、LMK04828)是高性能雙鎖相環(PLL)時鐘抖動清除器,專為無線基礎設施、數據轉換器時鐘、網絡通信(如SONET/SDH)、醫療/軍事/航空航天等應用設計。其核心特性包括:

- ?超低RMS抖動?:12 kHz至20 MHz帶寬下低至88 fs,100 Hz至20 MHz下91 fs。

- ?JESD204B支持?:提供14路可配置差分時鐘輸出(7路設備時鐘+7路SYSREF時鐘),支持多通道同步。

- ?雙PLL架構?:

- ?PLL1?:支持外部VCXO/晶體輸入,實現頻率清潔和冗余輸入切換。

- ?PLL2?:集成雙VCO(頻率范圍覆蓋1.84–3.08 GHz),提供靈活的時鐘分配和低噪聲輸出。

?2. 關鍵特性?

- ?輸出配置?:

- 14路差分輸出可編程為LVDS、LVPECL、HSDS或LCPECL格式,支持最高3.1 GHz頻率。

- 每路輸出支持獨立分頻(1–32)、數字延遲(4–32 VCO周期)和模擬延遲(0–575 ps)。

- ?冗余與同步?:

- 支持3路參考輸入(CLKin0/1/2),支持自動/手動切換和零延遲反饋模式。

- 集成SYSREF生成器,滿足JESD204B確定性延遲需求。

- ?低噪聲性能?:

- 噪聲底低至-162.5 dBc/Hz(245.76 MHz時)。

- 相位噪聲優化設計,適用于高精度時鐘樹應用。

?3. 功能模式?

- ?雙環模式?:PLL1清潔外部VCXO噪聲,PLL2生成高頻低抖動時鐘。

- ?單環模式?:禁用PLL1,直接使用PLL2內部VCO或外部VCO。

- ?時鐘分配模式?:繞過PLL,直接分配輸入時鐘至輸出。

- ?零延遲模式?:通過反饋路徑(內部或外部)確保輸入與輸出時鐘相位對齊。

?4. 應用場景?

?5. 封裝與電氣特性?

- ?封裝?:64引腳QFN(9.0 mm × 9.0 mm),工業級溫度范圍(-40°C至85°C)。

- ?電源?:3.15–3.45 V,典型功耗565–665 mA(全功能運行)。

- ?ESD保護?:HBM ±2000 V,CDM ±250 V。

?6. 設計支持?

- 提供詳細的寄存器配置指南(如SYNC/SYSREF時序控制、動態延遲調整)。

- 支持SPI接口編程,寄存器映射覆蓋時鐘輸出、PLL參數、狀態監控等。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘

+關注

關注

11文章

1994瀏覽量

135139 -

邏輯器件

+關注

關注

0文章

108瀏覽量

20754 -

調節器

+關注

關注

5文章

913瀏覽量

49580 -

清除器

+關注

關注

0文章

56瀏覽量

6107 -

交流耦合

+關注

關注

0文章

44瀏覽量

12632

發布評論請先 登錄

相關推薦

熱點推薦

如何采用系統參考模式設計JESD204B時鐘

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1

發表于 11-18 06:36

LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動

發表于 08-20 10:37

?0次下載

LMK04832-SEP符合JESD204B/C標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04832-SEP符合JESD204B/C標準的航天級、超低噪聲、雙環路時鐘抖動

發表于 08-20 10:39

?0次下載

LMK04368-EP符合JESD204B/C標準的超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04368-EP符合JESD204B/C標準的超低噪聲、雙環路時鐘抖動清除器

發表于 08-20 09:52

?0次下載

LMK04832-SP符合JESD204B標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04832-SP符合JESD204B標準的航天級、超低噪聲、雙環路時鐘抖動清除

發表于 08-20 09:32

?0次下載

帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表

電子發燒友網站提供《帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器

發表于 08-21 09:20

?0次下載

具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表

電子發燒友網站提供《具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器

發表于 08-21 09:12

?0次下載

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

該LMK04832是一款超高性能時鐘調節器,支持 JEDEC JESD204B,還與 LMK0482x

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

LMK04828-EP 器件是業界性能最高的時鐘調理器,支持 JESD204B。

PLL2的14個時鐘輸出可配置為使用器件和SYSRE

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

評論