LMK0482x 系列是業界性能最高的時鐘調節器,支持 JEDEC JESD204B。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個 JESD204B 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

LMK0482x 系列具有高性能,加上在功率或性能之間權衡的能力、雙 VCO、動態數字延遲、保持和無毛刺模擬延遲等功能,是提供靈活的高性能時鐘樹的理想選擇。

*附件:lmk04821.pdf

特性

- JEDEC JESD204B支持

- 超低 RMS 抖動

- 88 fs RMS 抖動(12 kHz 至 20 MHz)

- 91 fs RMS 抖動(100 Hz 至 20 MHz)

- 245.76 MHz時–162.5 dBc/Hz本底噪聲

- PLL2 提供多達 14 個差分器件時鐘

- PLL1 多達 1 個緩沖 VCXO/晶體輸出

- LVPECL、LVDS、2xLVCMOS 可編程

- 雙環路PLLatinum? PLL架構

- PLL1

- 多達 3 個冗余輸入時鐘

- 自動和手動切換模式

- 無中斷開關和LOS

- 集成低噪聲晶體振蕩器電路

- 輸入時鐘丟失時的保持模式

- 多達 3 個冗余輸入時鐘

- PLL2

- 歸一化 [1 Hz] PLL 本底噪聲為

–227 dBc/Hz - 相位檢測器速率高達 155 MHz

- OSCin 倍頻器

- 兩個集成低噪聲VCO

- 歸一化 [1 Hz] PLL 本底噪聲為

- 50% 占空比輸出分頻,1 至 32

(偶數和奇數) - 精密數字延遲,動態可調

- 25 ps 步進模擬延遲

- 多模:雙 PLL、單 PLL 和時鐘分配

- 工業溫度范圍:–40 至 85°C

- 支持 105°C PCB 溫度(在導熱墊處測量)

- 3.15V 至 3.45V 工作電壓

- 封裝:64引腳QFN(9.0 mm × 9.0 mm × 0.8 mm)

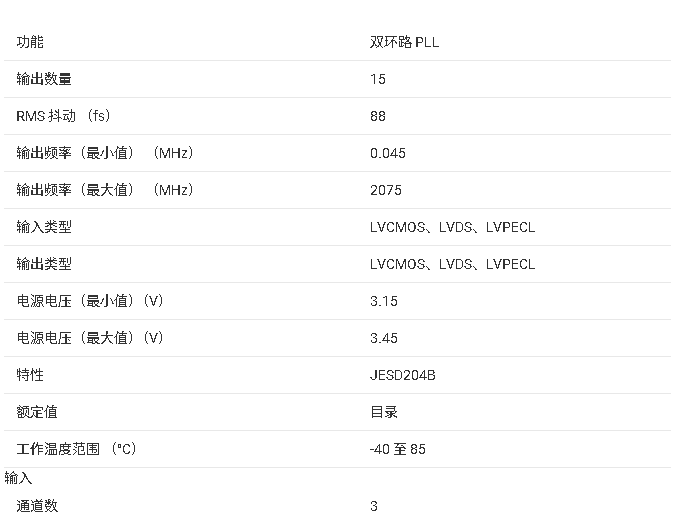

參數

?1. 產品概述?

LMK04821/LMK04826/LMK04828是德州儀器(TI)推出的高性能雙鎖相環(PLL)時鐘調節器,專為無線基礎設施、數據轉換器時鐘、醫療/軍事/航空航天等應用設計。核心特性包括:

- ?超低抖動性能?:RMS抖動低至88 fs(12 kHz–20 MHz帶寬)。

- ?JESD204B支持?:提供14路可配置差分時鐘輸出(7組設備時鐘+7組SYSREF時鐘),支持多通道同步。

- ?雙PLL架構?:

- ?PLL1?:支持3路冗余參考輸入,集成VCXO/晶體振蕩器電路,具備自動/手動切換和保持模式(Holdover)。

- ?PLL2?:集成雙VCO(頻率范圍1.84–3.08 GHz),支持動態數字延遲和模擬延遲調整。

- ?靈活輸出配置?:支持LVDS、LVPECL、HSDS、LCPECL等多種格式,最高輸出頻率3.1 GHz。

?2. 關鍵特性?

- ?低噪聲設計?:噪聲底低至-162.5 dBc/Hz(245.76 MHz)。

- ?高集成度?:內置可編程環路濾波器、數字延遲模塊(25 ps步進)及頻率保持功能。

- ?工作條件?:3.15–3.45 V供電,工業級溫度范圍(-40°C至85°C)。

?3. 應用場景?

?4. 文檔結構?

?5. 設計支持?

?注?:具體型號差異(如LMK04821的VCO1分頻器)需參考設備選型表。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

轉換器

+關注

關注

27文章

9435瀏覽量

156677 -

pll

+關注

關注

6文章

985瀏覽量

138299 -

邏輯器件

+關注

關注

0文章

108瀏覽量

20759 -

晶體振蕩器

+關注

關注

9文章

750瀏覽量

33367 -

交流耦合

+關注

關注

0文章

44瀏覽量

12634

發布評論請先 登錄

相關推薦

熱點推薦

能有效降低高速網絡誤碼率的超低抖動時鐘合成器

為了應對日益緊縮的時鐘抖動預算,麥瑞半導體(Micrel, Inc)已推出兩個全新系列的ClockWorks超低抖動時鐘合成器,能夠滿足這些精確計時要求。SM84xxxx標準時鐘

LMK04832-SP時鐘抖動清除器

SYSREF分頻器SYSREF時鐘的25ps步進模擬延遲設備時鐘和SYSREF的數字延遲和動態數字延遲PLL1的保持模式PLL1或PLL2的0延遲環境溫度范圍:–55°C至125°CLMK5C33216LMK04816LMK04808LMK04832-SPLMK04906LMK

發表于 03-24 16:13

超低抖動時鐘合成器的設計挑戰

該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動

發表于 04-21 23:14

?1062次閱讀

超低抖動時鐘合成器的設計挑戰

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動

發表于 04-22 09:35

?443次閱讀

超低抖動時鐘合成器的設計挑戰

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動

發表于 04-25 09:54

?669次閱讀

超低抖動時鐘合成器的設計挑戰

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動

發表于 05-08 10:19

?596次閱讀

LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表.pdf》資料免費下載

發表于 08-20 10:37

?0次下載

LMK5C33414A:高性能網絡同步器與抖動清除器的深度剖析

LMK5C33414A:高性能網絡同步器與抖動清除器的深度剖析 在無線通信和基礎設施應用領域,時鐘同步和抖動控制至關重要。TI推出的

低噪聲時鐘抖動清除器LMK04610:技術拆解與應用設計

低噪聲時鐘抖動清除器LMK04610:技術拆解與應用設計 在電子設備的世界里,時鐘信號就如同心臟的跳動,穩定而精準的時鐘對于各類系統的正常運行至關重要。今天,我們要深入探討的就是一款在

LMK0482x系列時鐘抖動清除器:高性能時鐘解決方案解析

LMK0482x系列時鐘抖動清除器:高性能時鐘解決方案解析 在電子設計領域,時鐘信號的穩定性和低抖動對于系統性能至關重要。LMK0482x系

探索LMK04100系列時鐘抖動清除器:特性、應用與設計要點

探索LMK04100系列時鐘抖動清除器:特性、應用與設計要點 引言 在電子設計領域,時鐘信號的穩定性和低抖動特性對于眾多應用至關重要。德州儀器(TI)的

LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南

LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南 在電子設計領域,時鐘抖動的控制至關重要,它直接影響著系統的性能和穩定性。TI 的

LMK04821 超低抖動合成器和抖動清除器技術手冊

LMK04821 超低抖動合成器和抖動清除器技術手冊

評論