LMK04832-SP 是一款高性能時(shí)鐘調(diào)節(jié)器,支持 JEDEC JESD204B,適用于太空應(yīng)用。

PLL2的14個(gè)時(shí)鐘輸出可配置為使用器件和SYSREF時(shí)鐘驅(qū)動(dòng)7個(gè)JESD204B轉(zhuǎn)換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應(yīng)用,14 個(gè)輸出中的每一個(gè)都可以單獨(dú)配置為傳統(tǒng)時(shí)鐘系統(tǒng)的高性能輸出。

LMK04832-SP 可配置為在雙 PLL、單 PLL 或時(shí)鐘分配模式下運(yùn)行,無論是否具有 SYSREF 生成或重新時(shí)鐘。PLL2 可以與內(nèi)部或外部 VCO 一起工作。

*附件:lmk04832-sp.pdf

高性能與在功耗和性能之間權(quán)衡的能力、雙 VCO、動(dòng)態(tài)數(shù)字延遲和保持等功能相結(jié)合,使 LMK04832-SP 能夠提供靈活的高性能時(shí)鐘樹。

LMK04832-SP 采用 10.9 mm × 10.9 mm 64 引腳 CFP 封裝。

特性

- 貼片 #5962R1723701VXC

- 總電離劑量 100 krad(不含 ELDRS)

- SEL 免疫 >120 MeV × cm ^2^ /毫克

- SEFI 免疫 >120 MeV × cm ^2^ /毫克

- 最大時(shí)鐘輸出頻率:3255 MHz

- 多模:雙 PLL、單 PLL 和時(shí)鐘分配

- 6 GHz 外部 VCO 或分配輸入

- 超低噪聲,2500 MHz:

- 54 fs RMS 抖動(dòng)(12 kHz 至 20 MHz)

- 64 fs RMS 抖動(dòng)(100 Hz 至 20 MHz)

- –157.6 dBc/Hz 本底噪聲

- 超低噪聲,3200 MHz:

- 61 fs RMS 抖動(dòng)(12 kHz 至 20 MHz)

- 67 fs RMS 抖動(dòng)(100 Hz 至 100 MHz)

- –156.5 dBc/Hz 本底噪聲

- PLL2

- PLL FOM 為 –230 dBc/Hz

- PLL 1/f 為 –128 dBc/Hz

- 相位檢測器速率高達(dá) 320 MHz

- 兩個(gè)集成VCO:2440至2600 MHz和2945至3255 MHz

- 多達(dá) 14 個(gè)差分器件時(shí)鐘

- 多達(dá) 1 個(gè)緩沖 VCXO/XO 輸出

- LVPECL、LVDS、2xLVCMOS 可編程

- 1-1023 CLKout分頻器

- 1-8191 SYSREF 分頻器

- SYSREF時(shí)鐘的25 ps步進(jìn)模擬延遲

- 器件時(shí)鐘和SYSREF的數(shù)字延遲和動(dòng)態(tài)數(shù)字延遲

- PLL1 的保持模式

- PLL1 或 PLL2 的 0 延遲

- 環(huán)境溫度范圍:–55 °C 至 125 °C

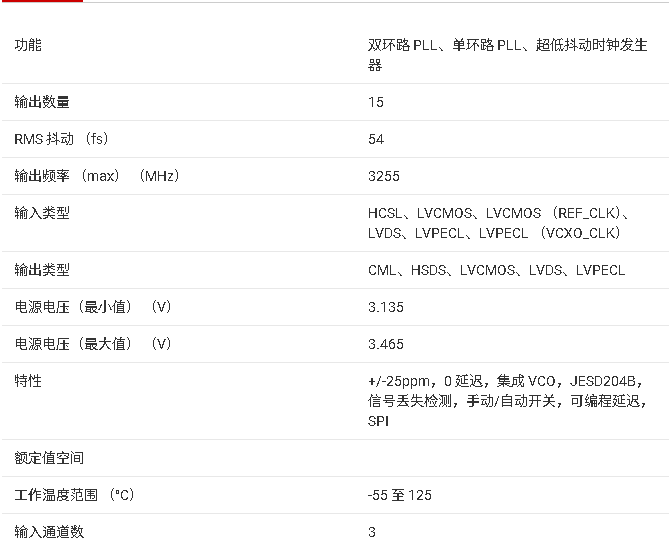

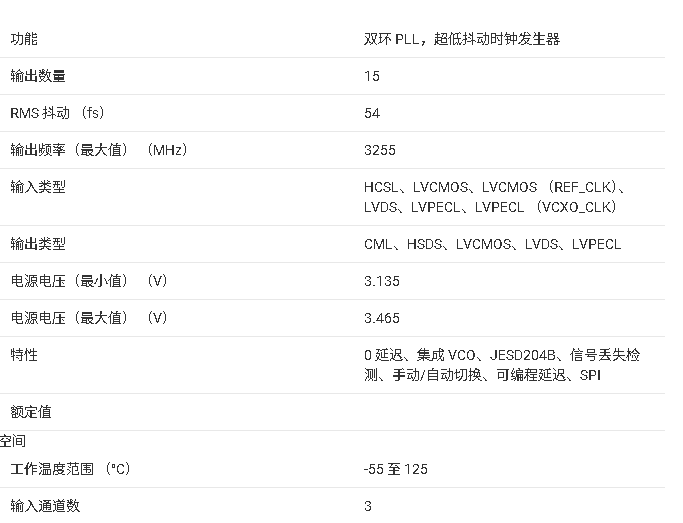

參數(shù)

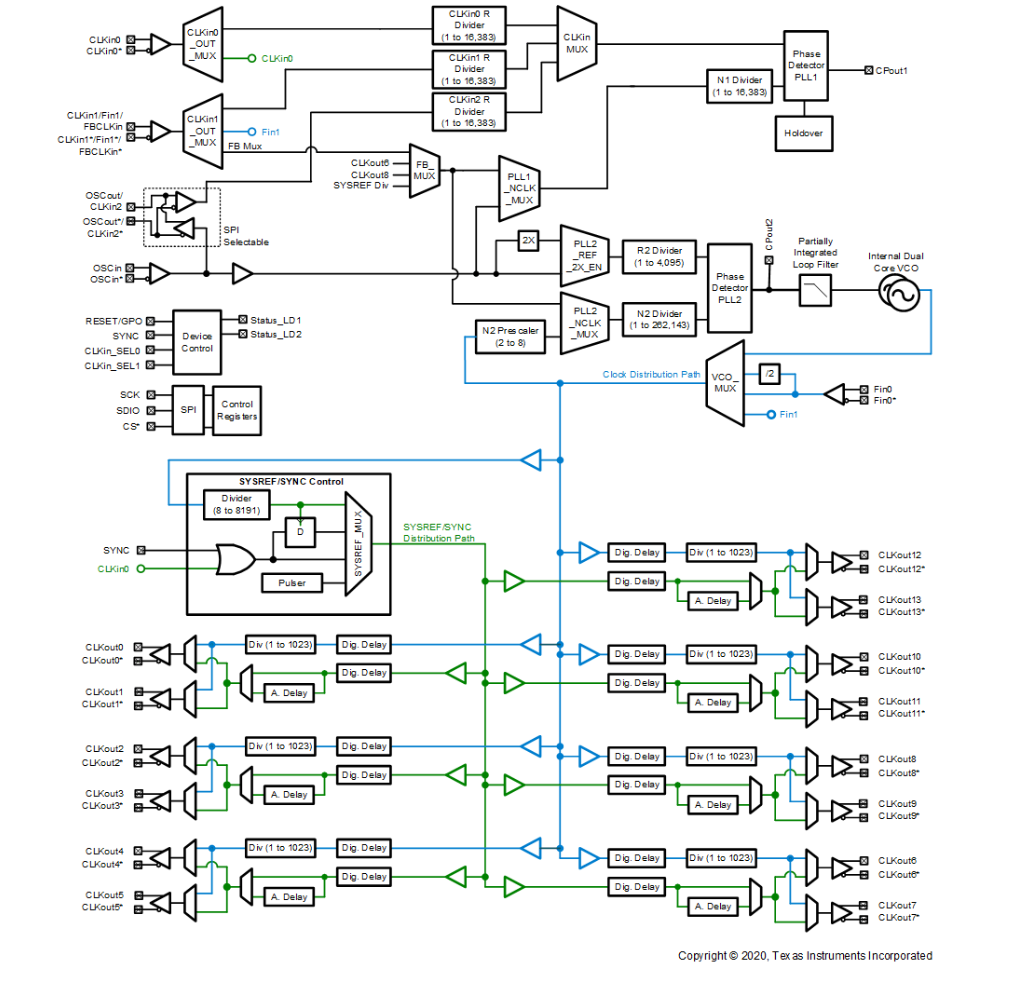

方框圖

?1. 產(chǎn)品概述?

LMK04832-SP 是一款航天級超低噪聲 JESD204B 雙環(huán)路時(shí)鐘抖動(dòng)消除器,適用于高可靠性空間應(yīng)用(如通信載荷、雷達(dá)成像等)。關(guān)鍵特性包括:

- ?輻射硬化?:總電離劑量 100 krad(ELDRS-free),抗 SEL/SEFI(>120 MeV·cm2/mg)。

- ?高性能時(shí)鐘?:最大輸出頻率 3255 MHz,支持雙 PLL、單 PLL 或時(shí)鐘分配模式。

- ?超低抖動(dòng)?:2500 MHz 下 RMS 抖動(dòng)低至 54 fs(12 kHz–20 MHz)。

- ?多格式輸出?:14 路差分時(shí)鐘輸出,支持 CML/LVPECL/LVDS/HSDS/LVCMOS 等可編程格式。

?2. 核心功能?

- ?雙 PLL 架構(gòu)?:

- ?PLL1?:外部 VCXO 參考,窄帶寬(10–200 Hz)用于低頻噪聲清理。

- ?PLL2?:內(nèi)部雙 VCO(2440–2600 MHz 和 2945–3255 MHz),寬帶寬(50–200 kHz)優(yōu)化高頻性能。

- ?JESD204B 支持?:可配置 7 對設(shè)備時(shí)鐘/SYSREF 輸出,支持確定性延遲和同步。

- ?0 延遲模式?:嵌套或級聯(lián)架構(gòu)確保輸入/輸出時(shí)鐘相位對齊。

- ?冗余輸入與保持模式?:支持 3 路參考時(shí)鐘輸入切換,在參考丟失時(shí)保持頻率穩(wěn)定(±0.71 ppm 典型精度)。

?3. 關(guān)鍵參數(shù)?

- ?電氣特性?:

- 工作電壓:3.3 V ±5%(-55°C 至 125°C)。

- 功耗:典型 780 mA(全功能模式)。

- 相位噪聲:-230 dBc/Hz PLL FOM(PLL2)。

- ?封裝?:64 引腳陶瓷扁平封裝(10.9 mm × 10.9 mm),帶金屬蓋密封。

?4. 應(yīng)用設(shè)計(jì)?

- ?時(shí)鐘分配?:支持外部 VCO(6 GHz 輸入)或內(nèi)部 VCO 模式。

- ?同步控制?:SYNC/SYSREF 路徑支持脈沖、連續(xù)或請求模式,滿足 JESD204B 初始化需求。

- ?動(dòng)態(tài)延遲調(diào)整?:數(shù)字延遲(8–1023 周期步進(jìn))和模擬延遲(21 ps 步進(jìn))優(yōu)化時(shí)序?qū)R。

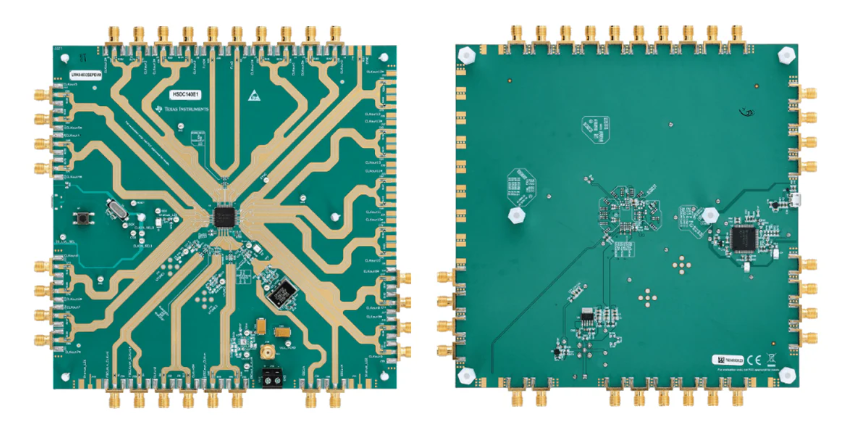

?5. 開發(fā)支持?

- ?工具鏈?:TI 提供 Clock Architect(頻率規(guī)劃)、PLLatinum Sim(環(huán)路濾波設(shè)計(jì))、TICS Pro(寄存器配置)。

- ?輻射認(rèn)證?:通過 MIL-STD-883 總劑量測試和 JEDEC57 SEE 驗(yàn)證。

?6. 典型應(yīng)用場景?

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9418瀏覽量

156335 -

邏輯器件

+關(guān)注

關(guān)注

0文章

107瀏覽量

20719 -

調(diào)節(jié)器

+關(guān)注

關(guān)注

5文章

912瀏覽量

49437 -

交流耦合

+關(guān)注

關(guān)注

0文章

44瀏覽量

12613 -

時(shí)鐘系統(tǒng)

+關(guān)注

關(guān)注

1文章

127瀏覽量

12930

發(fā)布評論請先 登錄

LMK04832配置時(shí)鐘輸出時(shí),IDL和ODL怎么配置?有沒有統(tǒng)一的做法?

LMK04832的時(shí)鐘輸出例如CLKOUT2_3兩對時(shí)鐘全部作為DEVICE CLOCK輸出時(shí)頻率只能是一致的嗎?

LMK04832EVM開發(fā)板在設(shè)置0和1通道的時(shí)鐘是只能輸出一樣的頻率嗎?

LMK04832 CMOS輸出衰減怎么解決?

LMK04832 oscin懸空的時(shí)候,clkout可以輸出時(shí)鐘嗎?

LMK04832-SP時(shí)鐘抖動(dòng)清除器

LMK04832-SP符合JESD204B標(biāo)準(zhǔn)的航天級、超低噪聲、雙環(huán)路時(shí)鐘抖動(dòng)清除器數(shù)據(jù)表

帶雙環(huán)路PLL且符合JESD204B標(biāo)準(zhǔn)的LMK04832超低噪聲時(shí)鐘抖動(dòng)清除器數(shù)據(jù)表

LMK04832EVM-CVAL用戶指南

LMK04832SEPEVM評估模塊技術(shù)解析與應(yīng)用指南

?LMK04832-SEP 芯片技術(shù)文檔摘要

?LMK04832-SP 文檔總結(jié)

?LMK04832-SP 文檔總結(jié)

評論