LMK04368-EP 是一款高性能時鐘調節器,支持 JEDEC JESD204B/C,適用于太空應用。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個 JESD204B/C 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于 JESD204B/C 應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

*附件:lmk04368-ep.pdf

該器件可配置為在雙PLL、單PLL或時鐘分配模式下工作,無論是否生成SYSREF或重新時鐘。PLL2可與內部或外部VCO一起工作。

高性能與在功耗和性能之間權衡的能力、雙 VCO、動態數字延遲和保持等功能相結合,可以提供靈活的高性能時鐘樹。

特性

- 視頻#:V62/23612

- 環境溫度范圍:–55°C 至 125°C

- 最大時鐘輸出頻率:3255 MHz

- 多模:雙 PLL、單 PLL 和時鐘分配

- 6 GHz 外部 VCO 或分配輸入

- 超低噪聲,2500 MHz:

- 54 fs RMS 抖動(12 kHz 至 20 MHz)

- 64 fs RMS 抖動(100 Hz 至 20 MHz)

- –157.6 dBc/Hz 本底噪聲

- 超低噪聲,3200 MHz:

- 61 fs RMS 抖動(12 kHz 至 20 MHz)

- 67 fs RMS 抖動(100 Hz 至 100 MHz)

- –156.5 dBc/Hz 本底噪聲

- PLL2

- PLL FOM 為 –230 dBc/Hz

- PLL 1/f 為 –128 dBc/Hz

- 相位檢測器速率高達 320 MHz

- 兩個集成VCO:2440至2600 MHz和2945至3255 MHz

- 多達 14 個差分器件時鐘

- 多達 1 個緩沖 VCXO/XO 輸出

- LVPECL、LVDS、2xLVCMOS 可編程

- 1-1023 CLKOUT分頻器

- 1-8191 SYSREF 分頻器

- SYSREF時鐘的25 ps步進模擬延遲

- 器件時鐘和 SYSREF 的數字延遲和動態數字延遲

- PLL1 的保持模式

- PLL1 或 PLL2 的 0 延遲

- 高可靠性

- 受控基線

- 一個裝配/測試站點

- 一個制造現場

- 延長產品生命周期

- 擴展產品變更通知

- 產品可追溯性

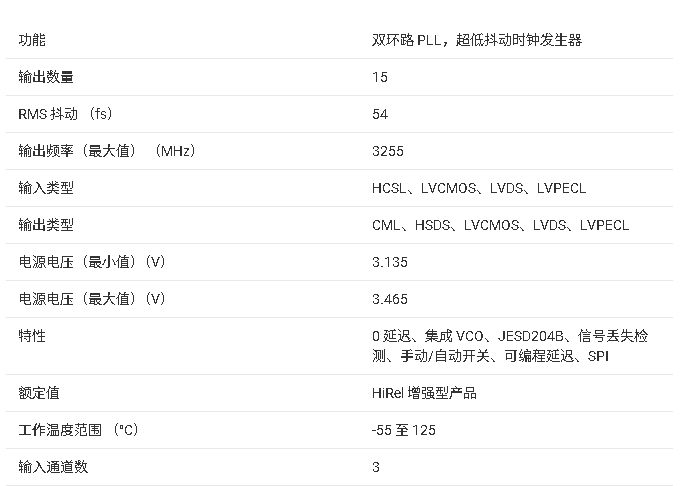

參數

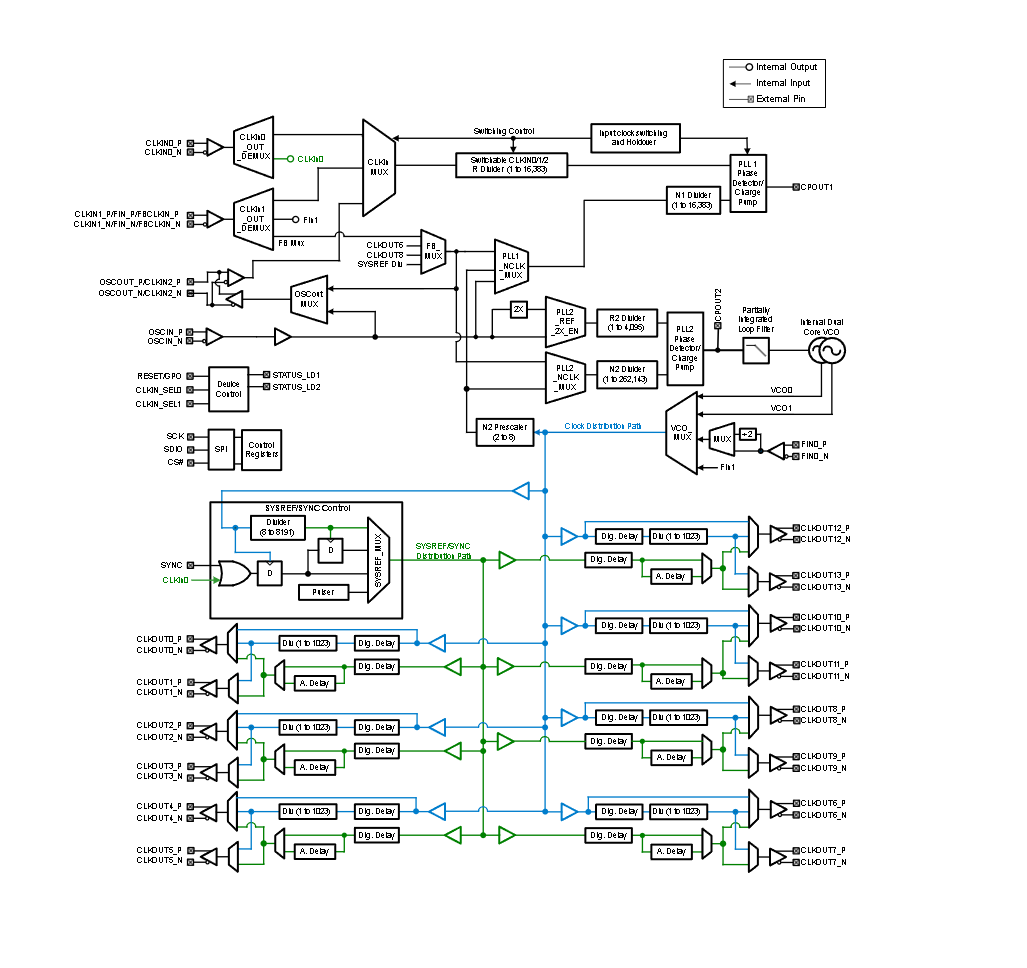

方框圖

- ?產品概述?

- LMK04368-EP是一款高性能時鐘調節器,專為空間應用設計,支持JESD204B/C標準。

- 提供雙PLL、單PLL和時鐘分配模式,支持6 GHz外部VCO或分配輸入。

- 關鍵特性包括超低噪聲(54-fs RMS抖動@2500 MHz)、多模式操作和14個可配置差分時鐘輸出。

- ?主要特性?

- ?頻率范圍?:最大輸出頻率3255 MHz,支持寬溫度范圍(-55°C至125°C)。

- ?噪聲性能?:

- 2500 MHz下:54-fs RMS抖動(12 kHz至20 MHz),噪聲底-157.6 dBc/Hz。

- 3200 MHz下:61-fs RMS抖動(12 kHz至20 MHz),噪聲底-156.5 dBc/Hz。

- ?PLL性能?:PLL2支持高達320 MHz的相位檢測速率,集成雙VCO(2440-2600 MHz和2945-3255 MHz)。

- ?應用場景?

- 軍事雷達、電子戰、數據轉換器時鐘、無線基礎設施等。

- 支持JESD204B/C系統,可驅動7個轉換器或邏輯設備。

- ?功能模塊?

- ?PLL1?:用于低偏移抖動清除,支持冗余輸入和頻率保持。

- ?PLL2?:提供頻率乘法功能,支持內部或外部VCO。

- ?時鐘分配?:14個可編程輸出,支持CML、LVPECL、LVDS等多種格式。

- ?封裝與可靠性?

- 封裝類型:HTQFP(64引腳),尺寸10 mm × 10 mm。

- 高可靠性設計:包括擴展產品生命周期和嚴格的變更通知流程。

- ?設計支持?

- ?文檔與資源?

- 包含詳細的數據表、應用筆記(如AN-912)和在線工具支持(如Clock Tree Architect)。

?總結?:LMK04368-EP是一款高性能、多功能的時鐘調節器,適用于嚴苛環境和高精度時鐘需求的應用,提供靈活的配置和卓越的噪聲性能。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

轉換器

+關注

關注

27文章

9438瀏覽量

156748 -

pll

+關注

關注

6文章

985瀏覽量

138313 -

調節器

+關注

關注

5文章

913瀏覽量

49596 -

清除器

+關注

關注

0文章

56瀏覽量

6109

發布評論請先 登錄

相關推薦

熱點推薦

LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路

發表于 08-20 10:37

?0次下載

LMK04832-SEP符合JESD204B/C標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04832-SEP符合JESD204B/C標準的航天級、超低噪聲、雙環路

發表于 08-20 10:39

?0次下載

LMK04368-EP符合JESD204B/C標準的超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04368-EP符合JESD204B/C標準的超低噪聲、雙環路

發表于 08-20 09:52

?0次下載

LMK04832-SP符合JESD204B標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04832-SP符合JESD204B標準的航天級、超低噪聲、雙環路時鐘

發表于 08-20 09:32

?0次下載

LMK0482x超低噪聲JESD204B兼容時鐘抖動消除器數據表

電子發燒友網站提供《LMK0482x超低噪聲JESD204B兼容時鐘抖動消除器數據表.pdf》資

發表于 08-21 09:19

?1次下載

帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表

電子發燒友網站提供《帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘

發表于 08-21 09:20

?0次下載

具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表

電子發燒友網站提供《具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘

發表于 08-21 09:12

?0次下載

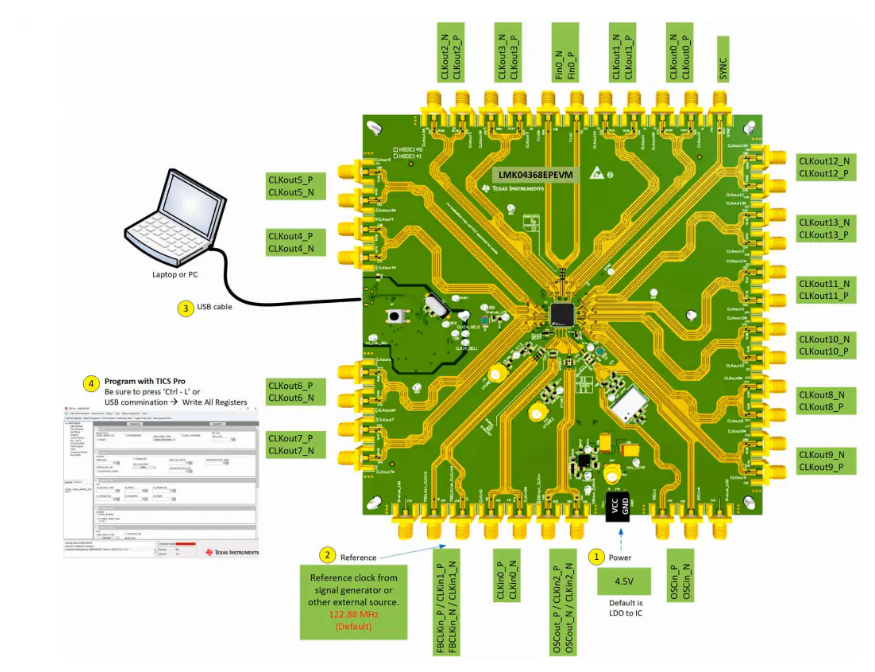

LMK04368EPEVM評估模塊技術解析與應用指南

Texas Instruments LMK04368EPEVM評估模塊用于演示LMK04368-EP的性能和特性。LMK04368-EP是一款高性能超低噪聲

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

LMK04828-EP 器件是業界性能最高的時鐘調理器,支持 JESD204B。

PLL2的14個時鐘輸出可配置為使用器件和SYSRE

LMK04616 超低噪聲低功耗JESD204B兼容時鐘抖動清除器總結

LMK0461x 器件系列是業界性能最高、功耗最低的抖動清除器,支持 JESD204B。16 個時鐘輸出可配置為使用器件和 SYSREF

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

LMK0482x 系列是業界性能最高的時鐘調節器,支持 JEDEC JESD204B。

PLL2 的 14 個時鐘輸出可配置為使用器件

Texas Instruments LMK04368-EP:超低噪聲時鐘抖動清理器的深度解析

Instruments的LMK04368-EP,這是一款專為太空應用設計的高性能時鐘調節器,支持JEDEC JESD204B/C標準。 文

低噪聲時鐘抖動清除器LMK04610:技術拆解與應用設計

表現卓越的器件——LMK04610。 文件下載: lmk04610.pdf 一、LMK04610簡介 LMK04610是一款超低噪聲、低功耗

?LMK04368-EP 超低噪聲JESD204B/C雙環路時鐘抖動清除器總結

?LMK04368-EP 超低噪聲JESD204B/C雙環路時鐘抖動清除器總結

評論