作為半導體器件的潛在致命隱患,Latch Up(閂鎖效應)一直是電子行業可靠性測試的重點。今天,SGS帶你深入揭秘這個“隱形殺手”,并詳解國際權威標準JEDEC JESD78F.02如何通過科學的測試方法,為芯片安全筑起堅固防線。

閂鎖效應(Latch Up):芯片內部的“雪崩”

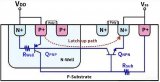

Latch Up是指集成電路在異常電壓或電流觸發下,內部寄生結構(如晶閘管PNPN、雙極晶體管BJT或ESD保護元件)被激活,形成持續低阻抗路徑,導致異常大電流(可達數百毫安)從電源流向地。即使觸發條件移除,電流仍持續,直至器件過熱或物理損壞。

典型觸發場景:

●信號引腳注入過流/過壓(如靜電放電、電源浪涌);

●電源引腳電壓瞬變超過器件耐受極限;

●高溫環境下寄生結構閾值降低(如結溫接近最大工作溫度Tjmax)。

危害有多嚴重?

●物理損壞:硅片熔融、金屬互連熔斷、封裝材料熱損傷(EIPD,電誘導物理損壞);

●系統級故障:引發設備死機、數據丟失,甚至引發汽車電子、醫療設備等關鍵領域的安全事故;

●可靠性風險:導致 “無故障發現(NTF)” 問題,增加售后維修成本和品牌聲譽損失。

破解之道——

JEDEC JESD78F.02標準的兩大核心測試

為了有效評估芯片抗Latch Up的能力,JEDEC制定了全球通用的測試標準JESD78F.02。該標準定義了兩種核心測試方法,覆蓋芯片所有引腳類型,模擬真實應用中的極端應力場景。

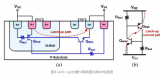

目標:驗證信號引腳(輸入/輸出/雙向引腳)對過流 / 過壓的免疫能力。

●I-Test(電流注入法):

強制注入正/負電流脈沖 (如±100mA),同時限制電壓在1.5×VmaxOP和MSV(最大應力電壓)中的較小值以下,避免非閂鎖損傷。

●E-Test(電壓注入法):

施加正/負電壓脈沖 (如1.5×VmaxOP),限制電流在預設閾值(如100mA),適用于高阻抗輸入或低電壓器件。

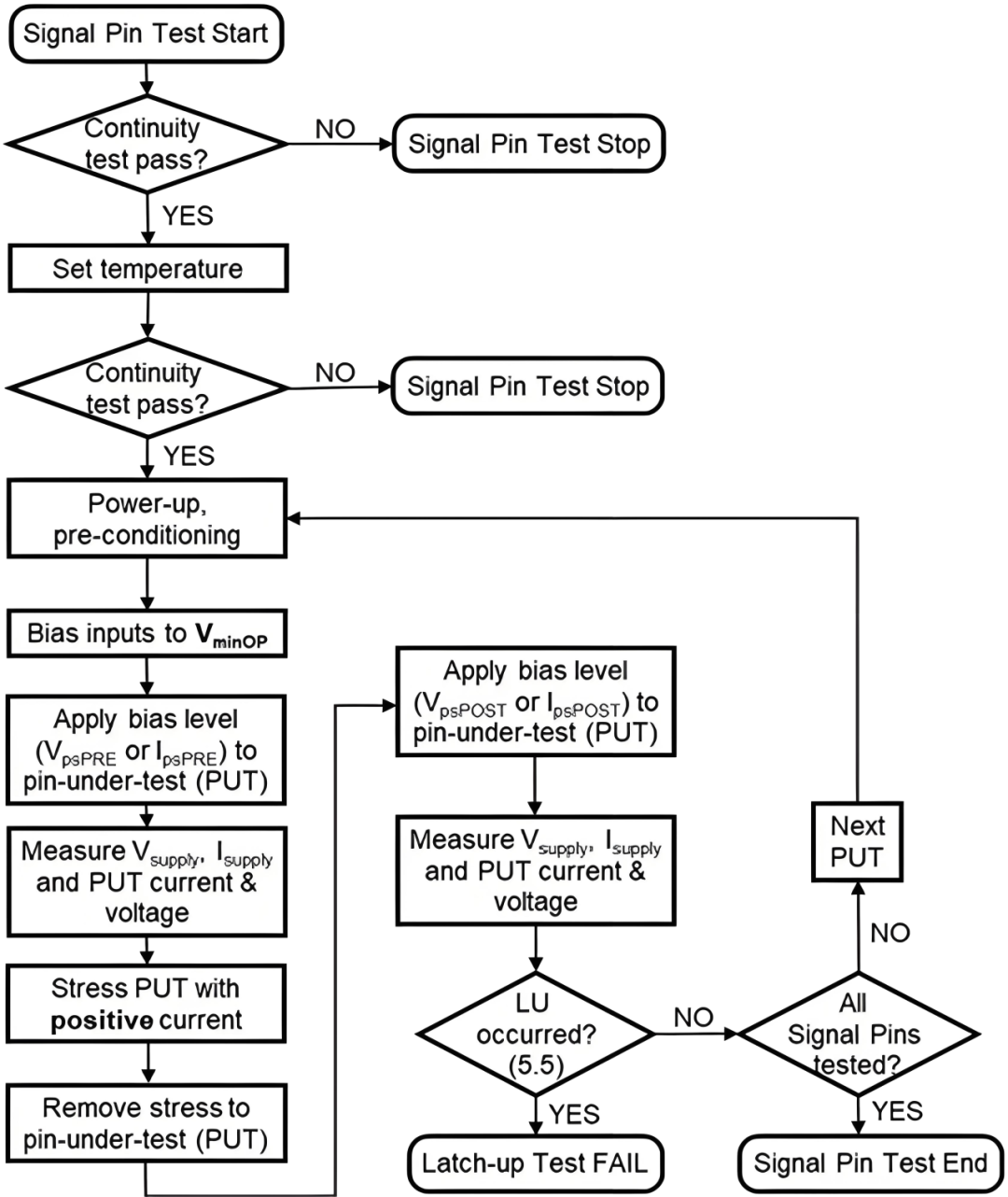

測試流程:

1.引腳分組(輸入/輸出),預處理至邏輯高/低狀態(VmaxOP/VminOP);

2.施加脈沖;

3.監測電源電流,達到以下條件則判定閂鎖觸發:

a.測試后電流值超出測試前電流值10mA;

b.測試后電流值超過測試前電流值的1.4倍。

信號引腳測試流程圖

02電源引腳測試(Supply Test)

目標:評估電源引腳對過電壓的耐受能力。

●方法:

對電源引腳施加1.5×VmaxSUP或MSV的電壓脈沖(哪個更低),同時限流設置為Ilimit=100mA+Inom(Inom為標稱電流)或1.5倍Inom(哪個更高)。

●關鍵參數:

避免電源因過流崩潰,需設置合理電流限制,確保測試有效性。

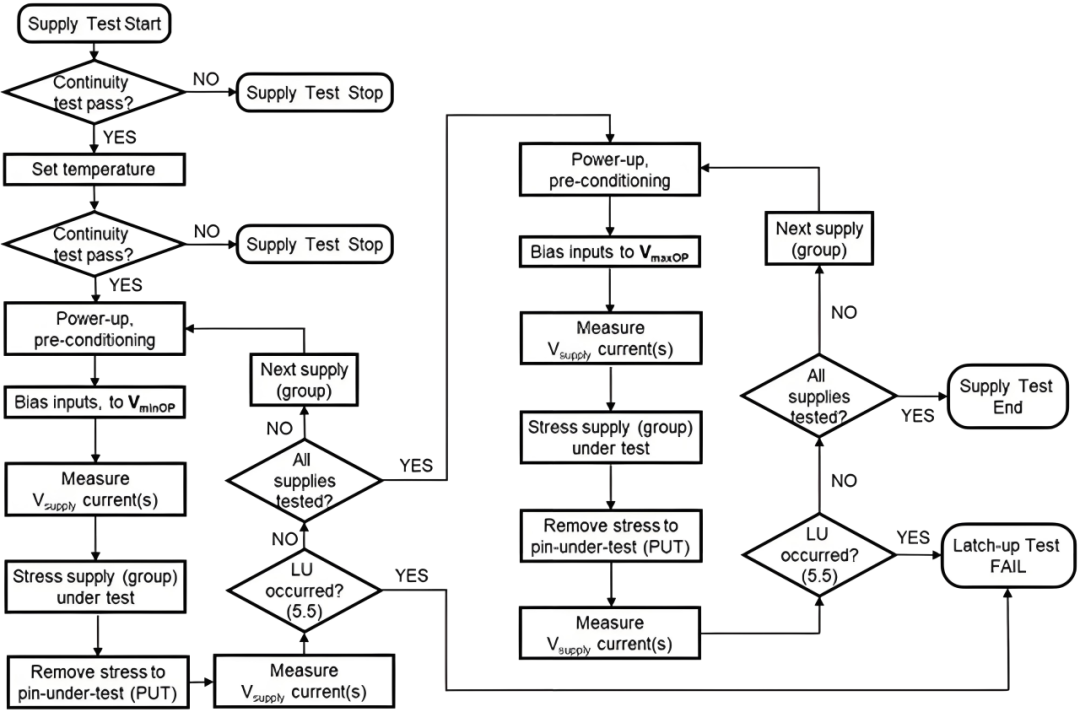

測試流程:

1.上電:按照指定的上電順序給設備上電;

2.測量標稱供電電流:在最大供電電壓VmaxSUP下測量每個供電引腳(或供電引腳組)的Isupply;

3.施加觸發電壓,并在此期間量測應力電源(Stress Supply)的電流、電壓,以及相關電源引腳的電壓(Vsupply(s));

4.監測電源電流,達到以下條件則判定閂鎖觸發:

a.測試后電流值超出測試前電流值10mA;

b.測試后電流值超過測試前電流值的1.4倍。

電源引腳測試流程圖

為什么Latch Up測試是非做不可的 “防線”?

進行符合JEDEC JESD78F.02標準的Latch Up測試,絕非可有可無,而是貫穿芯片研發、量產到市場準入的核心環節。

01可靠性認證的 “準入門檻”

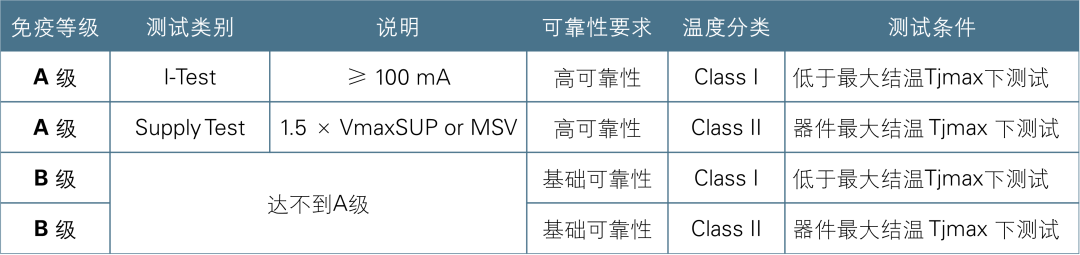

●等級劃分:

根據測試結果,器件可劃分為免疫等級A(高可靠性)或B(基礎等級),并標注溫度分類(Class I/II,Class II需在Tjmax下測試)。

●行業合規:

滿足汽車電子(如AEC-Q100)、工業控制等領域對器件抗干擾能力的強制要求。

Latch Up免疫等級劃分

點擊查看大圖

注:如有特殊需求,可以采取更嚴苛條件執行測試。

02研發與量產的 “質量防線”

●設計優化:

在芯片研發階段定位寄生結構缺陷,指導版圖優化(如增加保護環、調整阱結構);

●量產管控:

通過抽樣測試(最小3件樣品)篩查工藝波動導致的閂鎖風險,避免批量缺陷;

●失效分析:

結合脈沖源驗證和熱成像技術,精準定位失效引腳或結構。

03成本與風險的 “平衡點”

●早期測試成本僅為現場失效維修成本的1/100,尤其對復雜SoC、功率器件等高價值產品至關重要;

●符合JEDEC標準的測試報告可直接用于客戶審核,縮短產品上市周期。

SGS專業服務:從標準到落地的全流程支持

作為國際公認的測試、檢驗和認證機構,SGS依據JEDEC JESD78F.02標準,可為你提供:

●定制化測試方案

針對特殊引腳設計專屬測試流程,規避誤判風險;

●高精度測試設備

配備帶溫度控制的閂鎖測試儀,支持寬溫域測試,滿足Class II嚴苛要求;

●權威合規報告

出具含免疫等級、溫度分類及失效分析的中英文報告,助力產品全球市場準入。

-

芯片

+關注

關注

463文章

54186瀏覽量

467874 -

集成電路

+關注

關注

5459文章

12622瀏覽量

375246 -

半導體

+關注

關注

339文章

31018瀏覽量

265536

原文標題:干貨分享 | 半導體良率提升關鍵:基于JEDEC標準的Latch Up測試

文章出處:【微信號:SGS半導體服務,微信公眾號:SGS半導體服務】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高低溫試驗是什么?測試標準有哪些?

HDMI接口的ESD器件選擇(二):閂鎖效應的防范及解除

時識科技牽頭制定動態視覺傳感器性能測試方法國家標準

基于JEDEC JEP183A標準的SiC MOSFET閾值電壓精確測量方法

開關電源有哪些測試流程和方法?

CMOS集成電路中閂鎖效應的產生與防護

PCBA應力測試:從標準方法到產業實踐的可靠性守護

汽車充電樁出廠要做哪些標準的測試

醫療設備泄漏電流測試全:IEC 60601標準解讀與德國GMC測試方案

靜電的起因與靜電效應:技術分析與應用摘要

基于JEDEC標準的閂鎖效應測試方法

基于JEDEC標準的閂鎖效應測試方法

評論