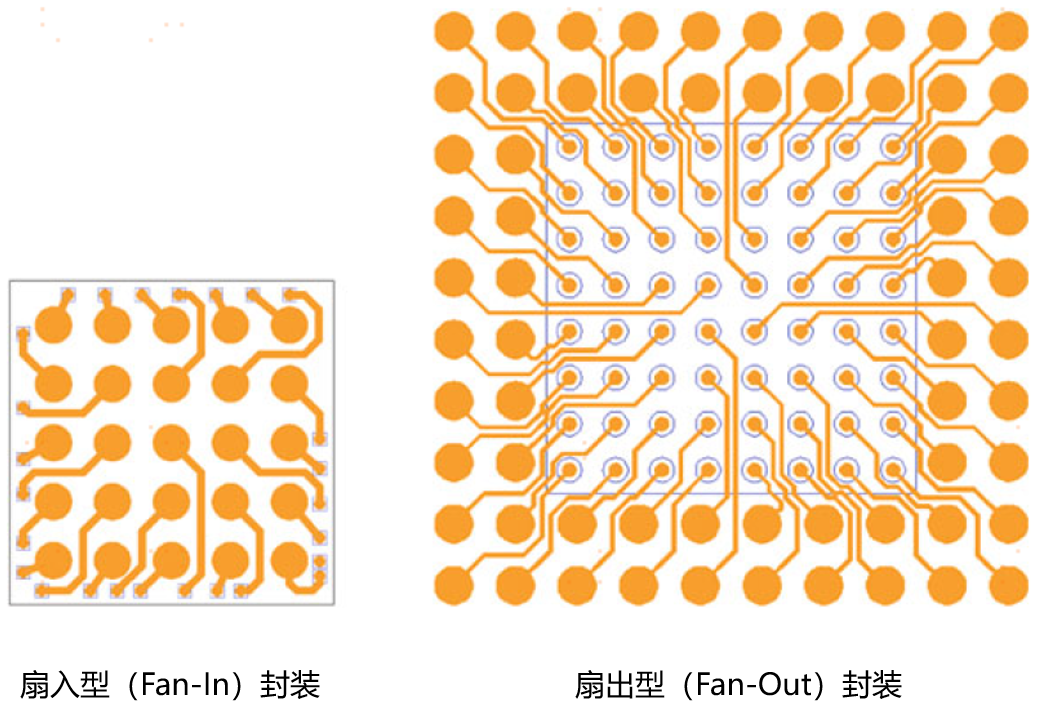

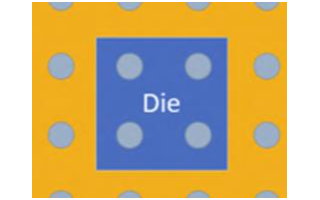

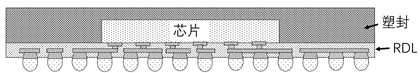

(Die)的下方, I/ O 接口的數量受限于芯片尺寸的大小, 隨著芯片技術的發展, I/ O接口的數量已經成為制約芯片性能發展的短板之一,而扇出型封裝則可以利用重布線(RDL)技術和模塑化合物提供

2024-04-07 08:41:00 2959

2959

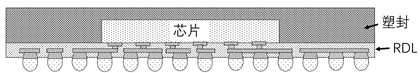

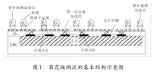

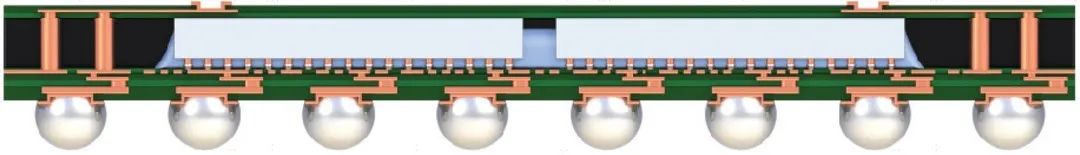

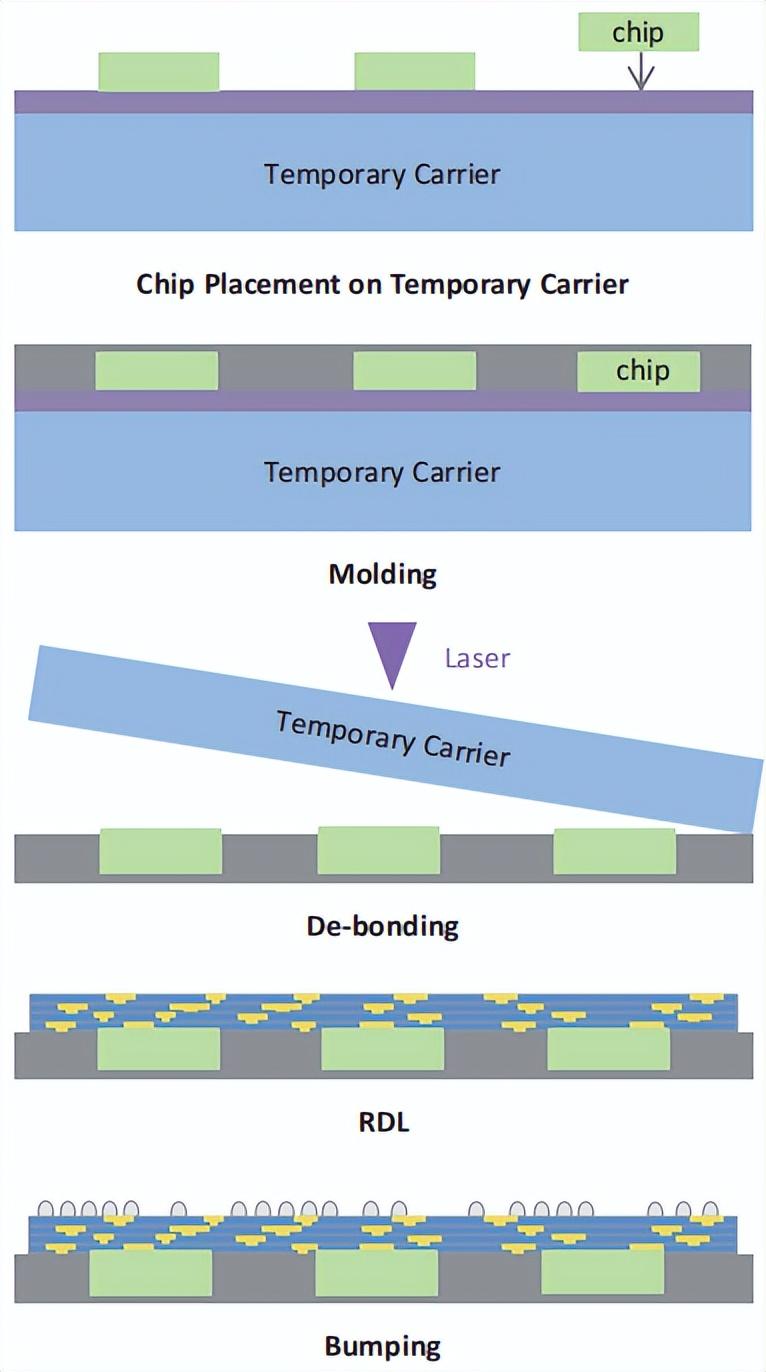

常規IC封裝需經過將晶圓與IC封裝基板焊接,再將IC基板焊接至普通PCB的復雜過程。與之不同,WLP基于IC晶圓,借助PCB制造技術,在晶圓上構建類似IC封裝基板的結構,塑封后可直接安裝在普通PCB

2025-05-14 11:08:16 2423

2423

IC封裝術語解析

1、BGA(ball grid array) 球形觸點陳列,表面貼裝型封裝之一。在印刷基板的背面按陳列方式制作出球形凸點用 以 代替引腳,在印刷

2010-02-21 11:13:26 941

941 傳蘋果(Apple)決定在下一款iPhone上采用扇出型晶圓級封裝(Fan-out WLP;FOWLP)技術。由于半導體技術日趨先進,無須印刷電路板(PCB)的封裝技術出現,未來恐發生印刷電路板市場逐漸萎縮的現象。

2016-05-06 09:05:33 2138

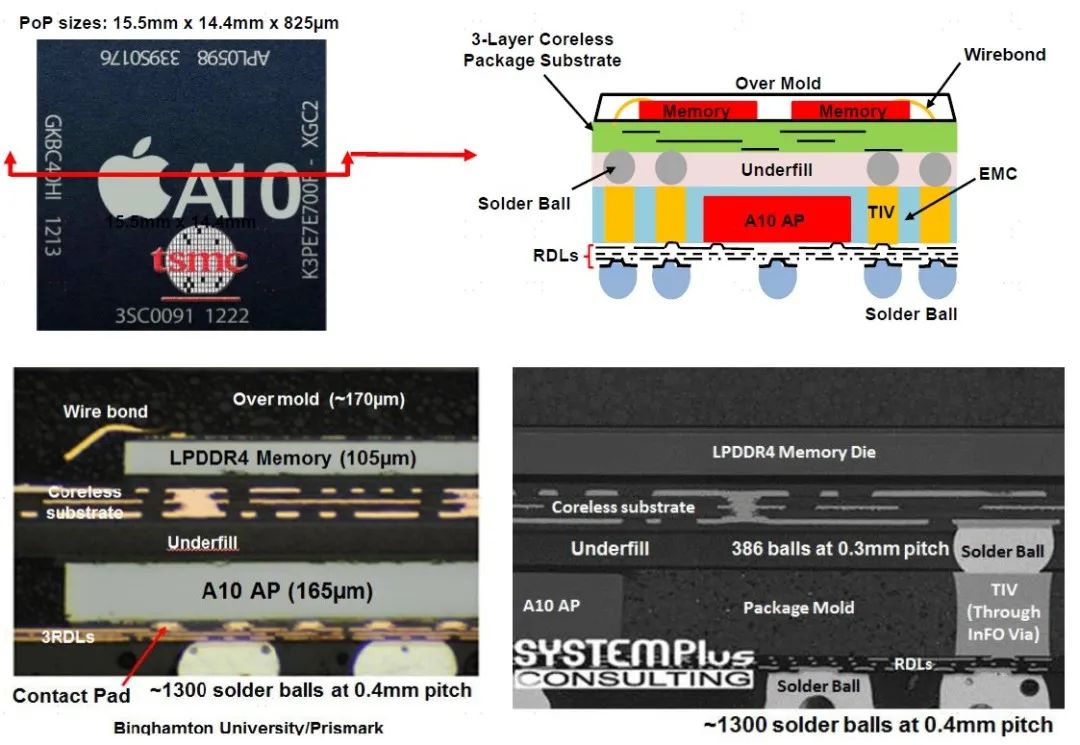

2138 高密度扇出型封裝技術滿足了移動手機封裝的外形尺寸與性能要求,因此獲得了技術界的廣泛關注。

2020-07-13 15:03:21 1588

1588

近幾年中,芯片特征尺寸已接近物理極限,而先進封裝技術成為延續摩爾定律的重要途徑。一系列新型封裝技術出現在人們視野之中。而其中扇出型晶圓級封裝(FOWLP)被寄予厚望,它將為下一代緊湊型、高性能的電子設備提供堅實而有力的支持。

2022-07-10 15:06:32 15700

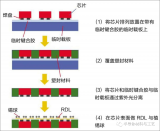

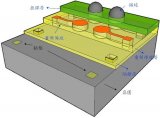

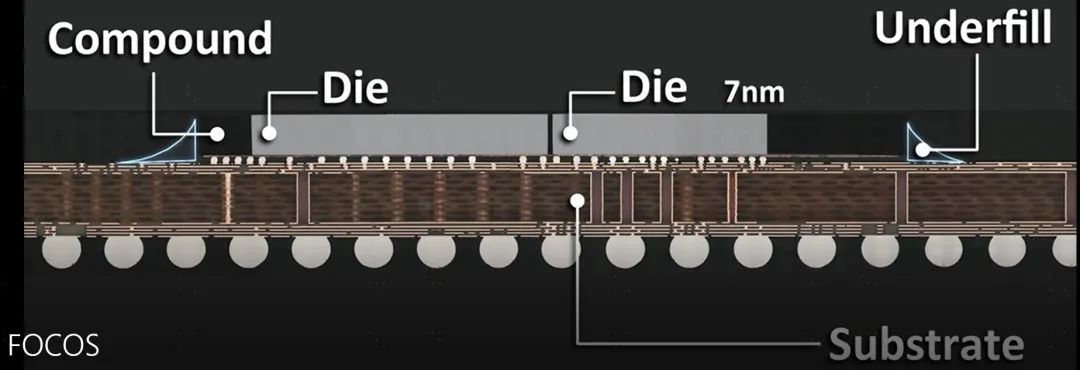

15700 扇出型圓片級封裝(FoWLP)是圓園片級封裝中的一種。相對于傳統封裝圓片級封裝具有不需要引線框、基板等介質的特點,因此可以實現更輕、薄短、小的封裝。扇出型圓片級封裝也可以支持多芯片、2.5D/3D

2023-05-08 10:33:17 3415

3415

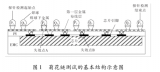

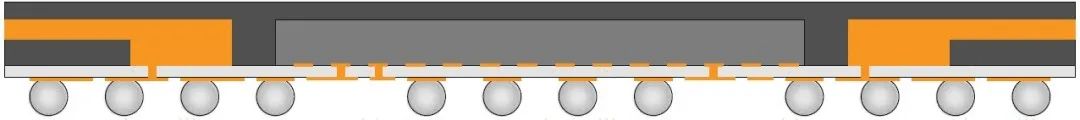

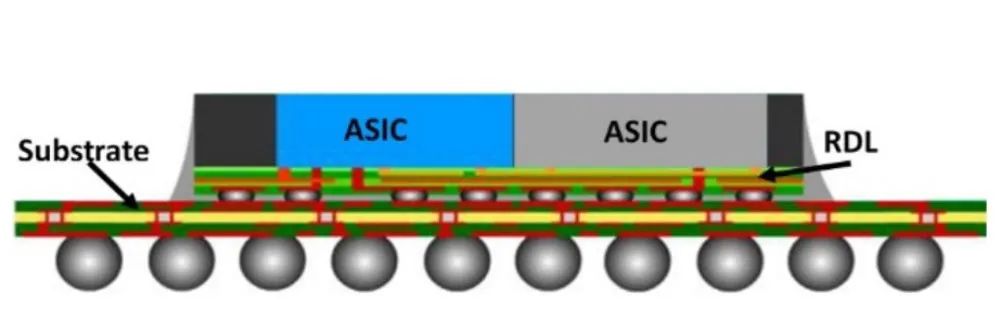

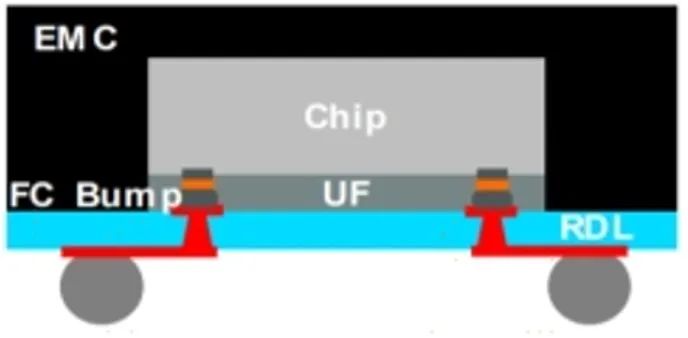

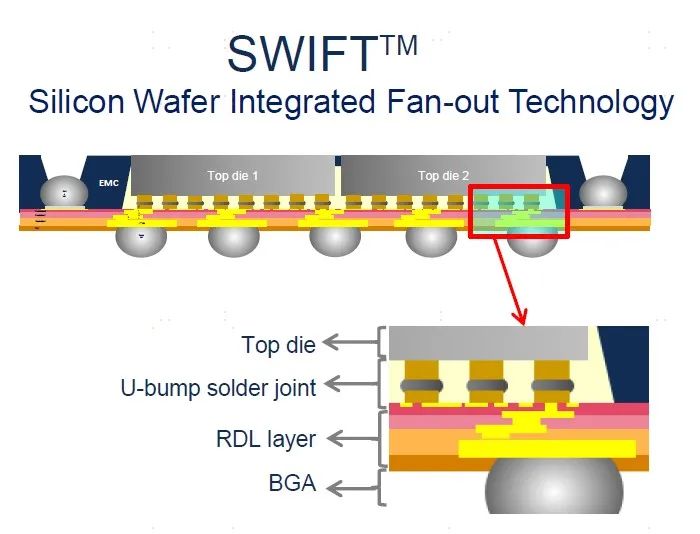

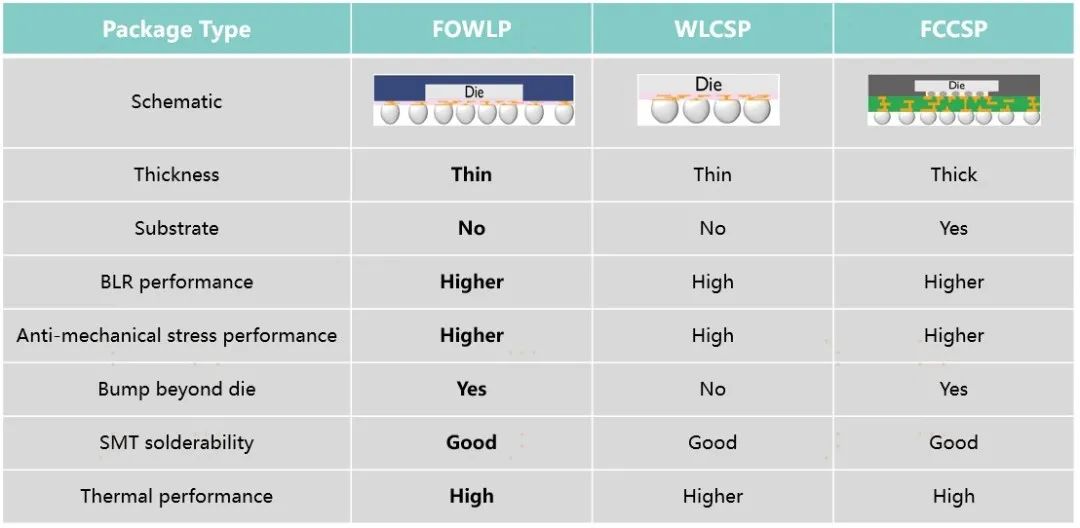

扇出型晶圓級封裝技術采取在芯片尺寸以外的區域做I/O接點的布線設計,提高I/O接點數量。采用RDL工藝讓芯片可以使用的布線區域增加,充分利用到芯片的有效面積,達到降低成本的目的。扇出型封裝技術完成芯片錫球連接后,不需要使用封裝載板便可直接焊接在印刷線路板上,這樣可以縮短信號傳輸距離,提高電學性能。

2023-09-25 09:38:05 3212

3212

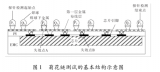

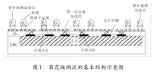

本文主要設計了用于封裝可靠性測試的菊花鏈結構,研究了基于扇出型封裝結構的芯片失效位置定位方法,針對芯片偏移、RDL 分層兩個主要失效問題進行了相應的工藝改善。經過可靠性試驗對封裝的工藝進行了驗證,通過菊花鏈的通斷測試和阻值變化,對失效位置定位進行了相應的失效分析。

2023-10-07 11:29:02 2145

2145

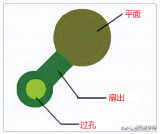

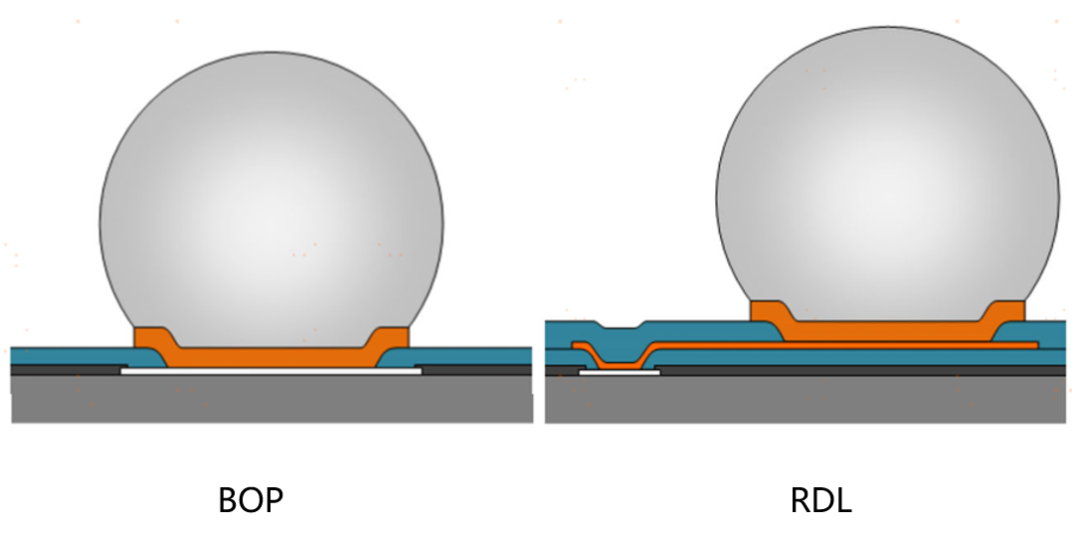

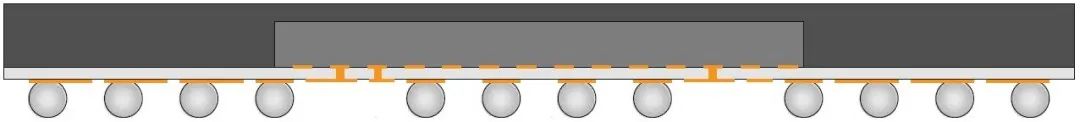

扇出型封裝一般是指,晶圓級/面板級封裝情境下,封裝面積與die不一樣,且不需要基板的封裝,也就是我們常說的FOWLP/FOPLP。扇出型封裝的核心要素就是芯片上的RDL重布線層(可參考下面圖表說明

2023-11-27 16:02:01 17600

17600

為適應異構集成技術的應用背景,封裝天線的實現技術也應有所變化,利用封裝工藝的優點以實現更佳的性能。

2024-02-29 11:11:30 2773

2773

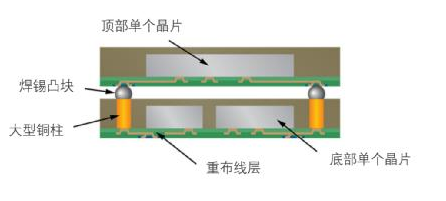

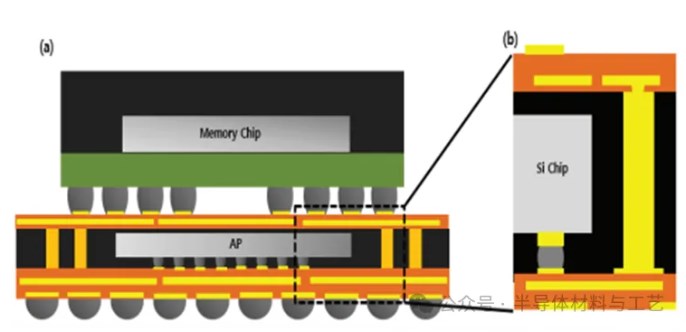

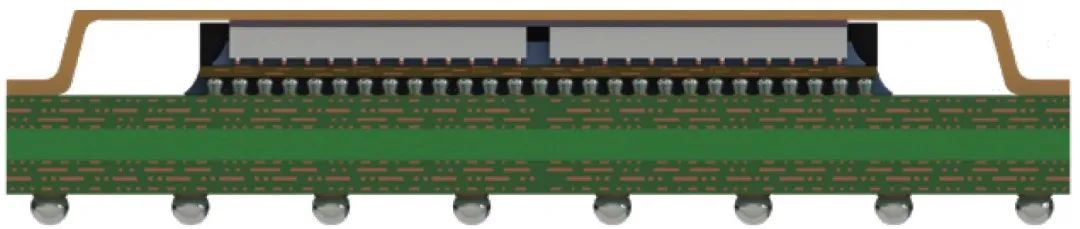

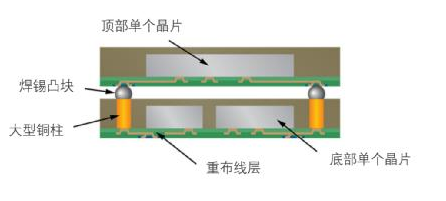

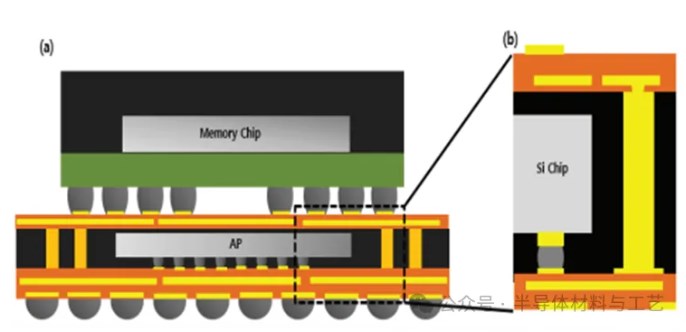

扇出型晶圓級中介層封裝( FOWLP)以及封裝堆疊(Package-on-Package, PoP)設計在移動應用中具有許多優勢,例如低功耗、短信號路徑、小外形尺寸以及多功能的異構集成。此外,它還

2025-01-22 14:57:52 4508

4508

晶圓級扇出封裝(FO-WLP)通過環氧樹脂模塑料(EMC)擴展芯片有效面積,突破了扇入型封裝的I/O密度限制,但其技術復雜度呈指數級增長。

2025-06-05 16:25:57 2152

2152

本文主要講述什么是系統級封裝技術。 從封裝內部的互連方式來看,主要包含引線鍵合、倒裝、硅通孔(TSV)、引線框架外引腳堆疊互連、封裝基板與上層封裝的凸點互連,以及扇出型封裝和埋入式封裝中的重布線等

2025-08-05 15:09:04 2135

2135

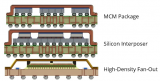

本文要點MCM封裝將多個芯片集成在同一基板上,在提高能效與可靠性的同時,還可簡化設計并降低成本。MCM封裝領域的最新進展包括有機基板、重分布層扇出、硅中介層和混合鍵合。這些技術能夠提升MCM

2025-12-12 17:10:14 6408

6408

本文的目的是了解為什么Deca的扇出技術最近被高通用于其PMIC扇入WLP die的保護層。嚴格的說,這仍舊是一個扇入die與側壁鈍化所做的扇出封裝。因此,本文的第一部分將描述扇入式WLP市場以及

2019-07-05 14:21:31 8337

8337 晶圓級扇出型封裝產業化項目。中科智芯半導體封測項目位于徐州經濟技術開發區鳳凰灣電子信息產業園,占地50畝,投資20億元,項目分兩期建設。 2018年9月一期開工建設,投資5億元,建成后將可形成年月能為12萬片12英寸晶圓。主廠房于2018年11月底封

2019-08-02 11:38:29 4829

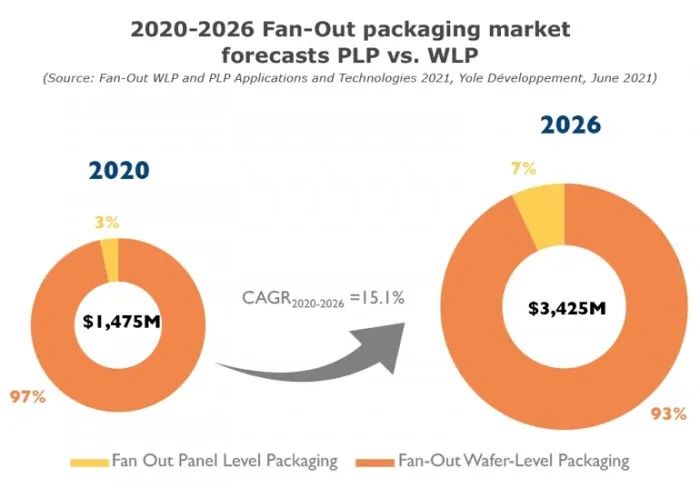

4829 電子發燒友網綜合報道,從臺積電InFO封裝在蘋果A10芯片的首次商用,到中國廠商在面板級封裝領域的集體突圍,材料創新與產業鏈重構共同推動著一場封裝材料領域的技術革命。 ? 據Yole數據,2025年

2025-06-12 00:53:00 1491

1491 好的傳感器的設計是經驗加技術的結晶。一般理解傳感器是將一種物理量經過電路轉換成一種能以另外一種直觀的可表達的物理量的描述。而下文我們將對傳感器的概念、原理特性進行逐一介紹,進而解析傳感器的設計的要點。

2020-08-28 08:04:04

,以扇出型疊層封裝(FO PoP)技術為主,其主要應用于智慧型手機,目前與兩岸部分手機芯片大廠合作中,2016年可望正式量產。由于矽品在模組設計與系統整合方面較為欠缺,因此近期積極尋求與EMS大廠鴻海

2017-09-18 11:34:51

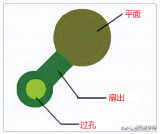

學習allegro 16.5 進行時,扇出使用的過孔問題請教,麻煩大家給答疑一下。謝謝了,祝大家勞動節快樂。看了于博士的視頻,4層的板子,對BGA器件進行了扇出操作。1:為什么信號引腳和電源引腳扇出

2015-04-30 23:50:16

Altium Designer 9,BGA扇出的時候,外面一圈焊盤出去的線不符合規則設置,我是對ROOM里的線寬設置的是6mil,外面的線是10mil,扇出時BGA外面一圈的焊盤引出的線是10mil,不知道是怎么回事?想刪掉重新扇出,不知道怎么刪,難不成要手動一個一個刪?求高手幫忙!

2015-01-07 15:56:28

,于是,電路的I/O數就需要更多,且I/O的密度也會不斷增加。對電路封裝的要求也更加嚴格。再采用QFP封裝技術,通過增加I/O數,減小引線間距, 已經不能滿足電子產品發展的要求。為了解決這一問題,國外

2015-10-21 17:40:21

1、BGA(ball grid array) 球形觸點陳列,表面貼裝型封裝之一。在印刷基板的背面按陳列方式制作出球形凸點用 以 代替引腳,在印刷基板的正面裝配LSI 芯片,然后用模壓樹脂或灌封方法

2011-07-23 09:23:21

QFP(quad flat package)四側引腳扁平封裝。表面貼裝型封裝之一,引腳從四個側面引出呈海鷗翼(L)型。基材有 陶 瓷、金屬和塑料三種。

2020-04-07 09:01:08

;7805中文資料_引腳圖_電路圖_封裝_PDF資料7805中文資料7805引腳圖7805電路圖7805封裝7805 PDF資料7805中文資料7805中文資料在第一價值網里面有。它是已經IC網絡超市

2010-11-03 15:42:09

廣泛,b型u***插座技術參數及應用范圍是小編有提到過的,今天主要是針對a型u***插座封裝和a型u***插座封裝尺寸進行解析。 a型u***插座封裝-a型u***插座引腳功能 引腳序列號功能名典

2016-06-08 16:01:04

隨著市場對芯片集成度要求的提高,I/O引腳數急劇增加,功耗也隨之增大,對集成電路封裝更加嚴格。為了滿足發展的需要,BGA封裝開始被應用于生產。BGA也叫球狀引腳柵格陣列封裝技術,它是一種高密度表面

2018-09-18 13:23:59

求助0.5mm焊盤,間距0.8mm的BGA封裝怎么設置自動扇出45度;我規則設置線寬4mil,間距也是4mil,可是自動扇出45度的方向失敗,而且有些焊盤扇出不了,如下面第一張圖;;;手動扇出是沒有問題的,下面第二張圖@Kivy @Pcbbar 謝謝!!

2019-09-19 01:08:11

光耦PC817中文解析

2012-08-20 14:32:28

。RDL不會直接與電路板連接。相反,WLP會在封裝體底部使用錫球,從而將RDL連接到電路板。圖4:扇入型封裝、倒裝芯片與扇出型封裝技術的比較(來源:Yole)第三類:基于基板的封裝。與此同時,基于基板

2019-02-27 10:15:25

氮化鎵功率半導體技術解析基于GaN的高級模塊

2021-03-09 06:33:26

我用的是AD13,BGA封裝器件扇出后無網絡的焊盤自然也會扇出到一個過孔,可最后進行DRC檢查時這些扇出的無網絡焊盤就會報短路,請問要怎么解決?這是正常現象還是規則哪里沒設置對,最后沒辦法只好在規則里將短路的規則中設置所有no net的網絡都可以短路,不知道這么做對不,請高手指點

2014-11-12 10:40:14

隨著集成電路設計師將更復雜的功能嵌入更狹小的空間,異構集成包括器件的3D堆疊已成為混合與連接各種功能技術的一種更為實用且經濟的方式。作為異構集成平臺之一,高密度扇出型晶圓級封裝技術正獲得越來越多

2020-07-07 11:04:42

球柵陣列封裝是目前FPGA和微處理器等各種高度先進和復雜的半導體器件采用的標準封裝類型。用于嵌入式設計的封裝技術在跟隨芯片制造商的技術發展而不斷進步,這類封裝一般分成標準和微型兩種。這兩種

2018-09-20 10:55:06

請問下誰知道DDR扇出為什么只扇出電源和地的部分,其他都沒有扇出來?

2016-11-28 13:04:19

轉載一篇講述高扇出的解決辦法的博文。鏈接:http://blog.163.com/fabulous_wyg/blog/static/174050785201322643839347/

2014-04-29 21:41:20

扇出系數,扇出系數是什么意思

扇出系數No:扇出系數No是指與非門輸出端連接同類門的最多個數。它反映了與非門的帶負載能力 。

2010-03-08 11:06:20 8439

8439 WILSONVILLE, Ore., 2016年3月15日— Mentor Graphics公司(納斯達克代碼:MENT)今天發布了一款結合設計、版圖布局和驗證的解決方案,為TSMC集成扇出型 (InFO) 晶圓級封裝技術的設計應用提供支持。

2016-03-15 14:06:02 1296

1296 傳蘋果在2016年秋天即將推出的新款智能型手機iPhone 7(暫訂)上,將搭載采用扇出型晶圓級封裝(Fan-out WLP;FOWLP)的芯片,讓新iPhone更輕薄,制造成本更低。那什么是FOWLP封裝技術呢?

2016-05-06 17:59:35 5105

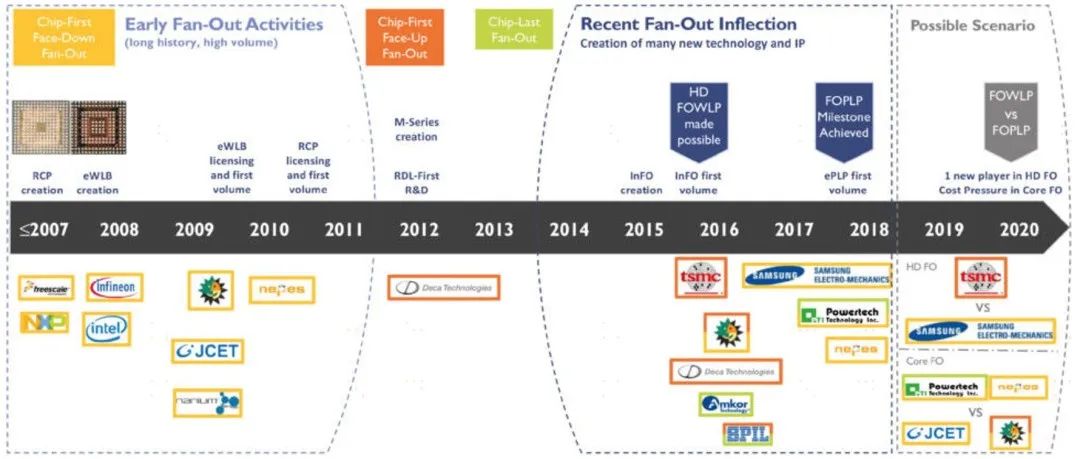

5105 2017年依然炙手可熱的扇出型封裝行業 新年伊始,兩起先進封裝行業的并購已經曝光:維易科(Veeco)簽訂了8.15億美元收購優特(Ultratech)的協議,安靠(Amkor Technology

2017-09-25 09:36:00 19

19 在談到多扇出問題之前,先了解幾個相關的信息,也可以當成是名詞解釋。 扇入、扇出系數 扇入系數是指門電路允許的輸入端數目。一般門電路的扇入系數為1—5,最多不超過8。扇出系數是指一個門的輸出端所驅動

2017-11-18 13:54:25 17986

17986 蘋果供應訂單的爭奪戰上,臺積電領先三星以7nm制程拿下蘋果新世代處理器訂單,但三星也不會坐以待斃,據悉,三星將發展扇出型晶圓級封裝(Fo-WLP)制程,想藉此贏回蘋果供應訂單。

2017-12-29 11:36:27 1307

1307 本文主要對特斯拉無人駕駛技術原理進行了最全面的解析,特斯拉的愿景是為所有人提供比人類駕駛更高的行車安全;為車主提供更低的交通成本;為無車之人提供低價、按需的出行服務。究竟特斯拉無人駕駛技術達到何種地步,人們能否完全在特斯拉電動車內解放雙手,下面給大家詳細的解析一下。

2018-01-04 16:09:48 61704

61704

韓媒報導,蘋果(Apple)決定將iPhone 7行動應用處理器(AP)A10交由臺積電代工,關鍵在于臺積電擁有后段制程競爭力。臺積電具備扇出型晶圓級封裝(Fan-out WLP;FoWLP)技術,將其稱為整合型扇型封裝(Intgrated Fan Out;InFO)。

2018-04-23 11:51:00 2554

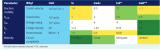

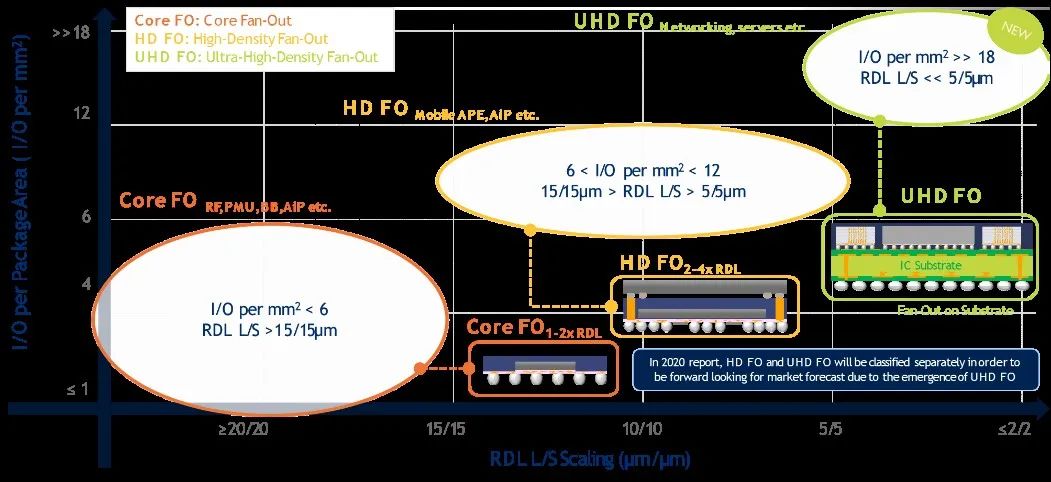

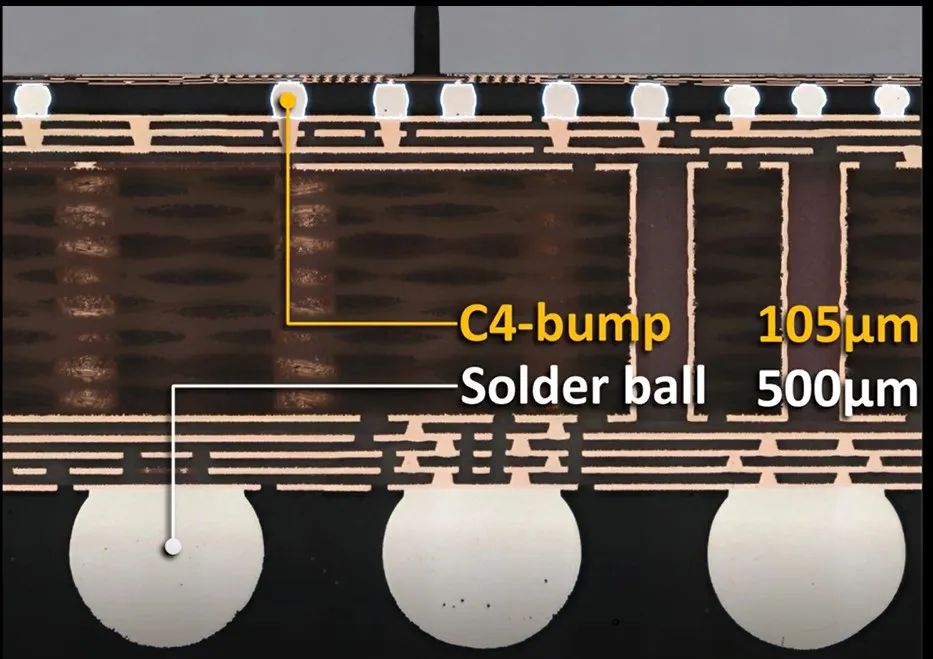

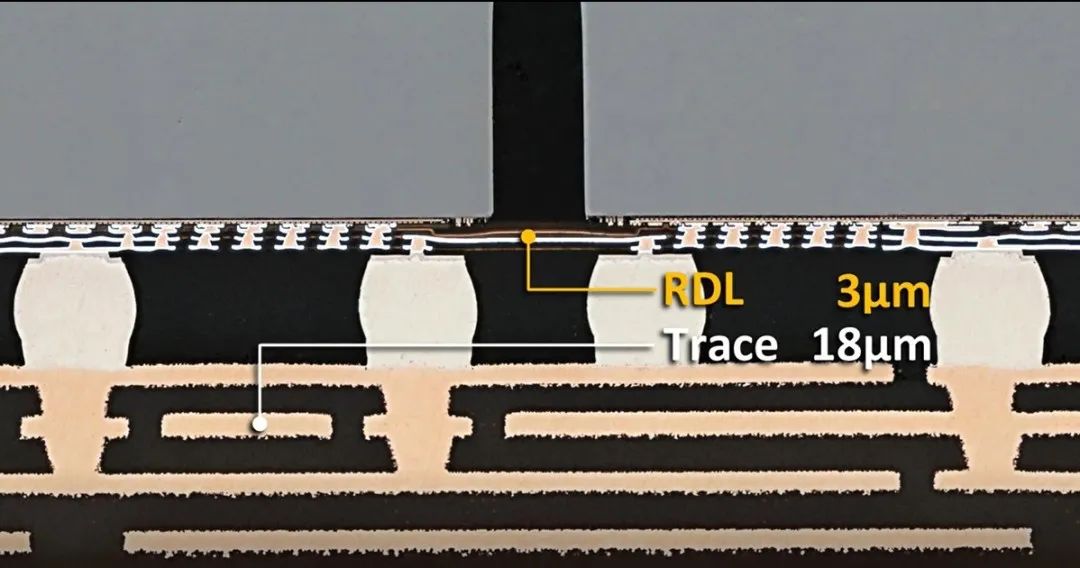

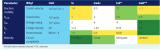

2554 對比來看,主要用于高端應用的扇出型封裝(Fan-Out),其標準密度是: I / O小于500的封裝,其線寬線距在8μm以上;而高密度扇出型封裝,其I / O大于500,線寬線距小于8μm。 同時,MIS材料本身相對較薄。該類基板在封裝過程中容易出現翹曲及均勻性問題。

2018-05-17 15:57:22 21197

21197

一文解析PLC的應用,具體的跟隨小編一起來了解一下。

2018-07-19 11:21:56 6116

6116

作為世界領先的濕制程生產設備商之一,Manz亞智科技宣布推出面板級扇出型封裝(FOPLP;Fan-out Panel Level Packaging)濕制程解決方案,透過獨家的專利技術,克服翹曲

2018-09-01 08:56:16 6215

6215 近日,華天科技(昆山)電子有限公司與江蘇微遠芯微系統技術有限公司合作開發的毫米波雷達芯片硅基扇出型封裝獲得成功,產品封裝良率大于98%,目前已進入小批量生產階段。

2018-12-02 11:56:00 2933

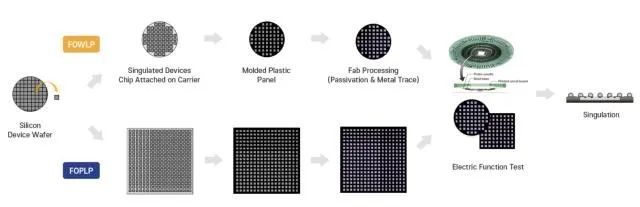

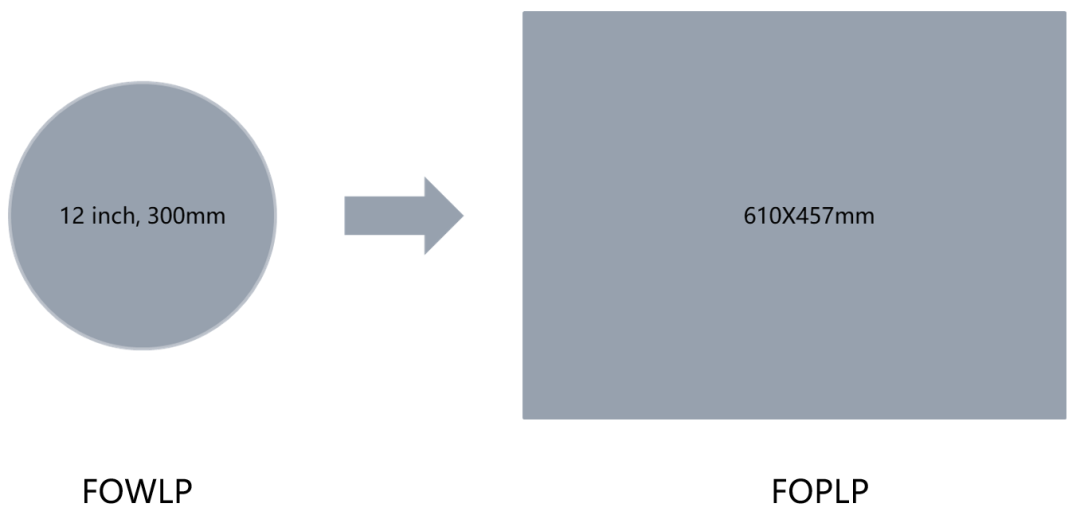

2933 面板級封裝(PLP)就是一種從晶圓和條帶級向更大尺寸面板級轉換的方案。由于其潛在的成本效益和更高的制造效率,吸引了市場的廣泛關注。由于面板的大尺寸和更高的載具使用率(95%),它還帶來了遠高于晶圓級尺寸扇出型晶圓級封裝(FOWLP)的規模經濟效益,并且能夠實現大型封裝的批量生產。

2018-12-30 10:24:00 12179

12179 據麥姆斯咨詢報道,先進封裝技術已進入大量移動應用市場,但亟需更高端的設備和更低成本的工藝制程。

2019-02-19 14:44:49 8230

8230

半導體封測大廠日月光半導體深耕5G天線封裝,產業人士指出,支援5G毫米波頻譜、采用扇出型封裝制程的天線封裝(AiP)產品,預估明年量產。

2019-09-17 11:39:54 4273

4273 全球領先的高科技設備制造商Manz亞智科技,交付大板級扇出型封裝解決方案于廣東佛智芯微電子技術研究有限公司(簡稱佛智芯),推進國內首個大板級扇出型封裝示范線建設,是佛智芯成立工藝開發中心至關重要的一

2020-03-16 16:50:22 4105

4105 近日,亞智科技向廣東佛智芯微電子技術研究有限公司(以下簡稱:佛智芯)交付大板級扇出型封裝解決方案。

2020-03-17 15:15:38 4829

4829 摩爾定律在晶圓工藝制程方面已是強弩之末,此時先進的封裝技術拿起了接力棒。扇出型晶圓級封裝(FOWLP)等先進技術可以提高器件密度、提升性能,并突破芯片I/O數量的限制。然而,要成功利用這類技術,在芯片設計之初就要開始考慮其封裝。

2020-11-12 16:55:39 1147

1147 Durendal?工藝提供了一種經濟高效的方式進行單個晶片堆疊,并能產出高良率以及穩固可靠的連接。在未來,我們期待Durendal?工藝能促進扇出型晶圓級封裝在單個晶片堆疊中得到更廣泛的應用。

2020-12-24 17:39:43 1299

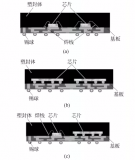

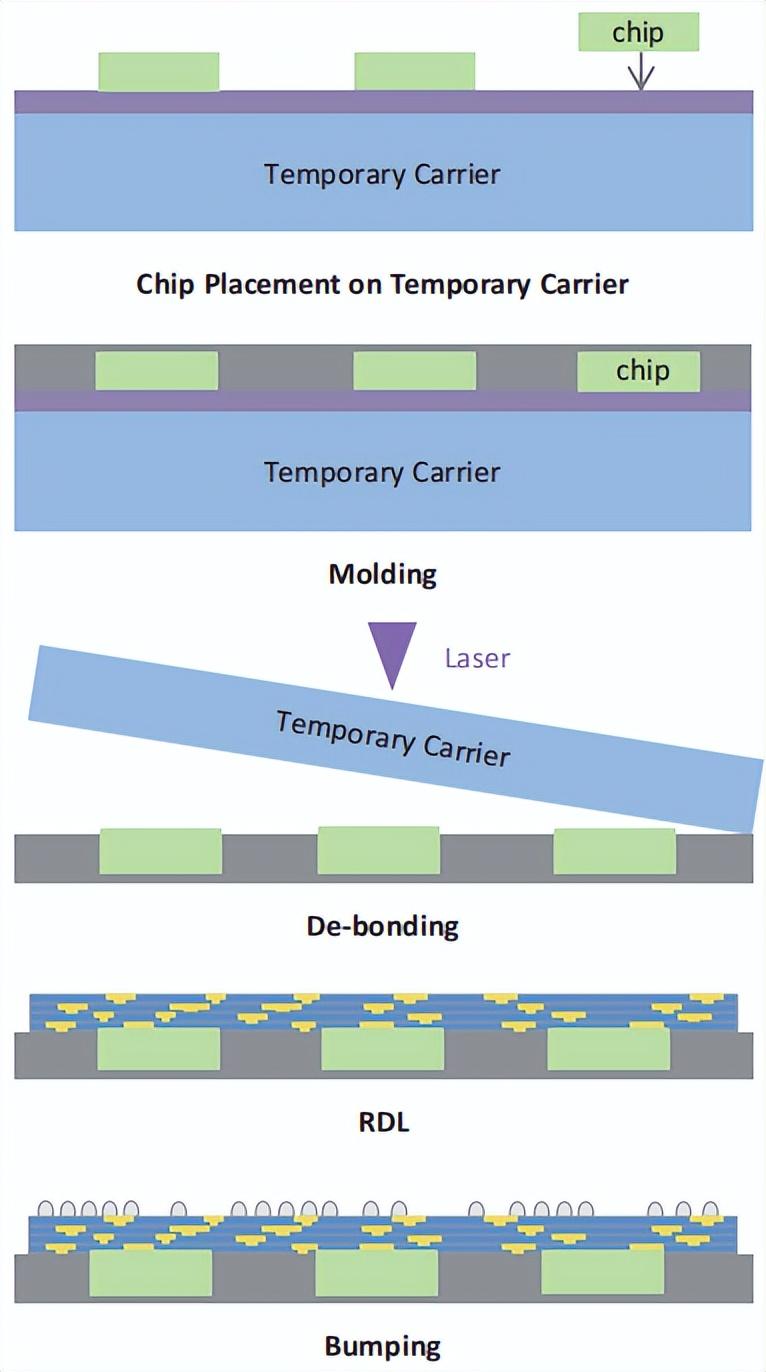

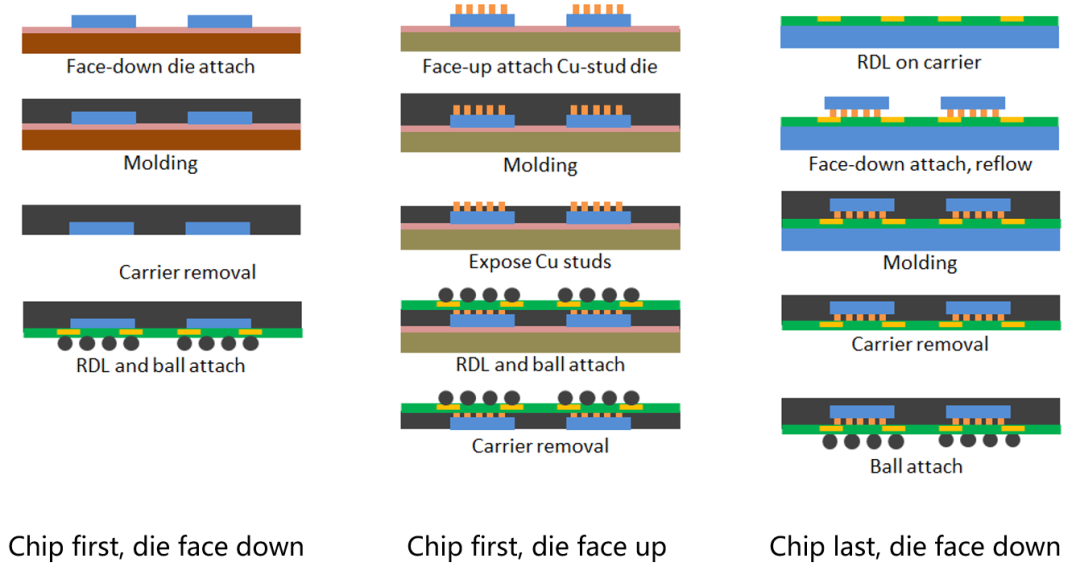

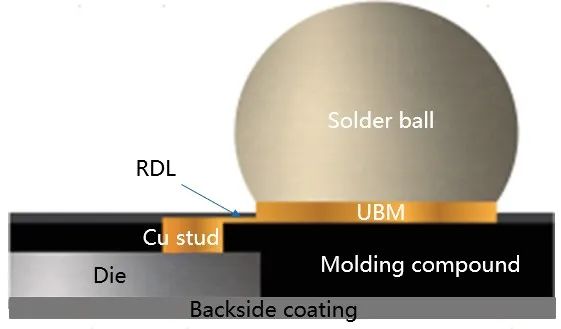

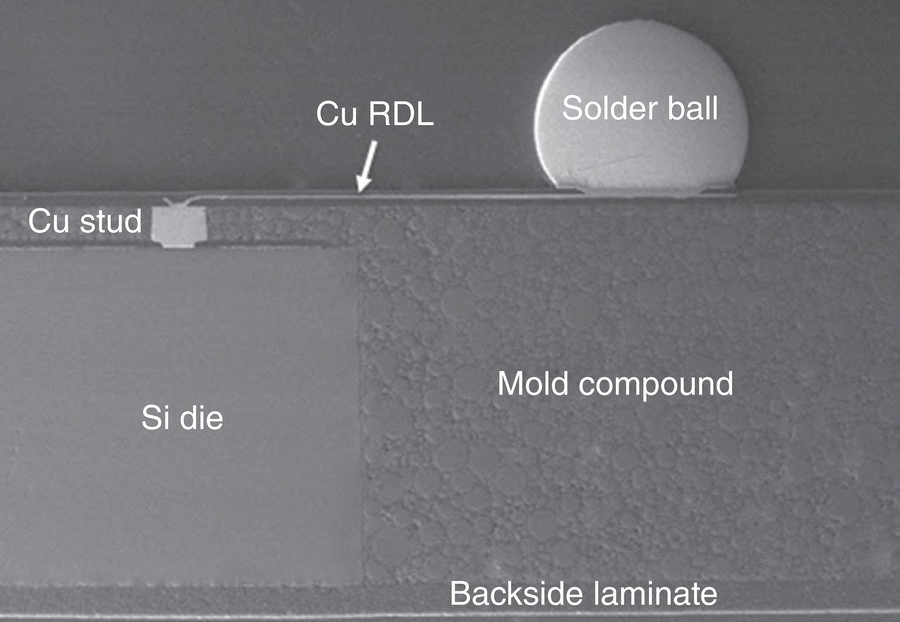

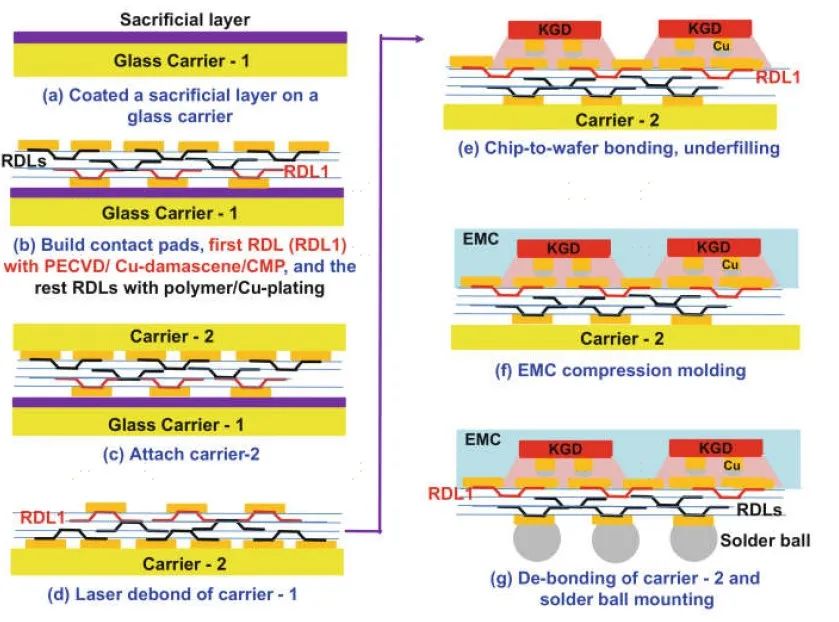

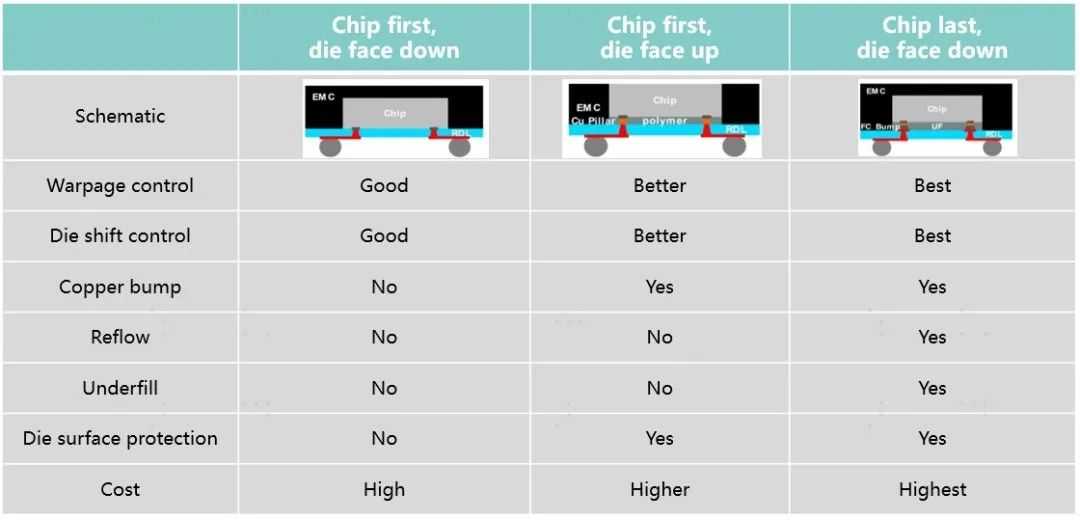

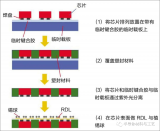

1299 Chip First工藝 自從Fan-Out封裝問世以來,經過多年的技術發展,扇出式封裝已經形成了多種封裝流程、封裝結構以適應不同產品需要,根據工藝流程,可以分為先貼芯片后加工RDL的Chip

2021-10-12 10:17:51 13257

13257 扇出型晶圓級封裝最大的優勢,就是令具有成千上萬I/O點的半導體器件,通過二到五微米間隔線實現無縫連接,使互連密度最大化,實現高帶寬數據傳輸,去除基板成本。

2022-03-23 14:02:25 2885

2885 日月光的扇出型封裝結構專利,通過偽凸塊增加了第一電子元件和線路層之間的連接強度,減少了封裝件的變形,并且減小了填充層破裂的風險,有效提高扇出型封裝結構的良率。

2022-11-23 14:48:33 884

884 移動電話技術變革,AP+內存堆棧技術運動,Interposer第一處理芯片

2022-11-30 11:26:09 2548

2548 一文詳解精密封裝技術

2022-12-30 15:41:12 2358

2358 高扇出指的是一個邏輯單元驅動的邏輯單元過多。常見于寄存器驅動過多的組合邏輯單元。至于驅動多少邏輯單元算過多,需要根據工藝,后端實現情況以及芯片本身類型來決定。

2023-03-22 14:45:42 1701

1701 據業內人士透露,三星電子已加緊布局扇出型(FO)晶圓級封裝領域,并計劃在日本設立相關生產線。

2023-04-10 09:06:50 2851

2851 當的方式為激光解鍵合。鴻浩半導體設備所生產的UV激光解鍵合設備具備低溫、不傷晶圓等技術特點,并且提供合理的制程成本,十分適合應用于扇出晶圓級封裝。 01 扇出晶圓級封裝簡介 扇出晶圓級封裝(Fan Out Wafer Level Packaging, FOWLP,簡稱扇出

2023-04-28 17:44:43 2743

2743

自從Fan-Out封裝問世以來,經過多年的技術發展,扇出式封裝已經形成了多種封裝流程、封裝結構以適應不同產品需要,根據工藝流程,可以分為**先貼芯片后加工RDL的Chip First工藝**和**先

2023-05-19 09:39:15 2002

2002

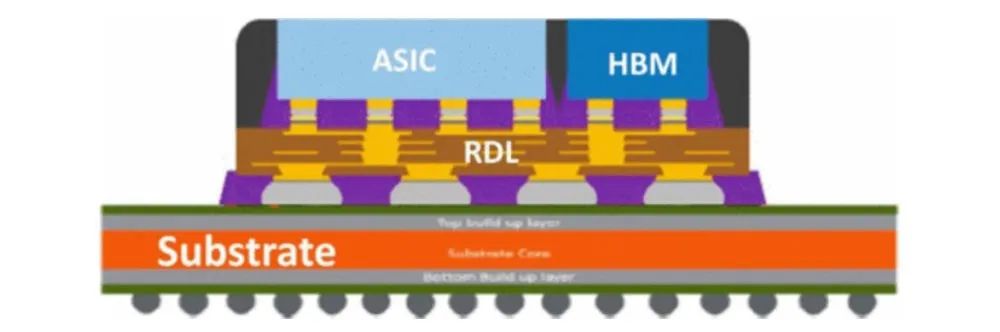

Chiplet技術是一種利用先進封裝方法將不同工藝/功能的芯片進行異質集成的技術。這種技術設計的核心思想是先分后合,即先將單芯片中的功能塊拆分出來,再通過先進封裝模塊將其集成為大的單芯片。

2023-07-17 09:21:50 7024

7024

在 PCB 布局設計中,特別是BGA(球柵陣列),PCB扇出、焊盤和過孔尤為重要。扇出是從器件焊盤到相鄰過孔的走線。

2023-07-18 12:38:12 5204

5204

ASICLAND代表Kang Sung-mo表示:與集成式扇出型封裝和有機基板封裝相比,CoWoS在性能和功耗方面有改進的空間。

2023-08-03 10:47:11 1609

1609 在扇出型晶圓級封裝(fowlp) 華海誠科的FOWLP封裝是21世紀前十年,他不對稱的封裝形式提出環氧塑封料的翹曲控制等的新要求環氧塑封料更加殘酷的可靠性要求,經過審查后也吐不出星星,芯片電性能維持良好。

2023-09-13 11:49:37 1711

1711 基于可靠性試驗所用的菊花鏈測試結構,對所設計的扇出型封裝結構進行了完整的菊花鏈芯片制造及后道組裝工藝制造,并對不同批次、不同工藝參數條件下的封裝樣品進行電學測試表征、可靠性測試和失效樣品分析。

2023-10-08 10:18:15 2065

2065

扇出型晶圓級封裝技術的優勢在于能夠利用高密度布線制造工藝,形成功率損耗更低、功能性更強的芯片封裝結構,讓系統級封裝(System in a Package, SiP)和3D芯片封裝更愿意采用扇出型晶圓級封裝工藝。

2023-10-25 15:16:14 2051

2051

如何對系統和組件進行可靠的封裝是微系統工業面臨的主要挑戰,因為微系統的封裝技術遠沒有微電子封裝技術成熟。微系統封裝在廣義上講有三個主要的任務:裝配、封裝和測試,縮寫為AP&T. AP&T在整個生產成本中占有很大的比例。

2023-11-06 11:38:40 2848

2848

激增的網絡流量導致網絡規模不斷升級,從100G升級至200G,再向400G邁進,數據運營商亟需經濟高效的網絡可擴展性。為了迎接這一挑戰,易飛揚推出了幾款特色的扇出型光模塊,作為網絡升級的樣板。

2023-12-07 11:09:59 1347

1347 據最新消息,全球顯示領導廠商群創光電近日成功拿下歐洲半導體大廠恩智浦的面板級扇出型封裝(FOPLP)大單。恩智浦幾乎包下了群創所有相關的產能,并計劃在今年下半年開始量產出貨。

2024-01-30 10:44:56 1428

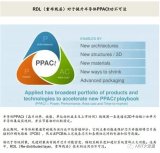

1428 RDL 技術是先進封裝異質集成的基礎,廣泛應用扇出封裝、扇出基板上芯片、扇出層疊封裝、硅光子學和 2.5D/3D 集成方法,實現了更小、更快和更高效的芯片設計。

2024-03-01 13:59:05 7303

7303

分為扇入型晶圓級芯片封裝(Fan-In WLCSP)和扇出型晶圓級芯片封裝(Fan-Out WLCSP),其特點是在整個封裝過程中,晶

2024-03-05 08:42:13 3555

3555

如今,再分布層(RDL)在高級封裝方案中得到了廣泛應用,包括扇出封裝、扇出芯片對基板方法、扇出封裝對封裝、硅光子學和2.5D/3D集成方法。

2024-04-08 11:36:48 5976

5976

業內人士普遍認為,英偉達的倡導將為臺灣封測行業帶來更多訂單機會。同時,英特爾、AMD等半導體巨頭也紛紛涉足面板級扇出型封裝,預計將使AI芯片供應更為流暢,推動AI技術的多元化發展。

2024-04-15 09:48:51 1699

1699 扇出技術是一種先進的封裝技術,能允許在晶圓級封裝之外的區域形成額外的I/O(輸入/輸出)點,從而提高芯片的性能和功能。與傳統的晶圓級封裝相比,扇出技術提供了更好的電氣和熱性能,同時還能實現更小的封裝尺寸。

2024-04-28 12:36:38 1677

1677

為解決CoWoS先進封裝產能緊張的問題,英偉達正計劃將其GB200產品提前導入扇出面板級封裝(FOPLP)技術,原計劃2026年的部署現提前至2025年。

2024-05-22 11:40:32 2042

2042 扇出型面板級封裝(Fan-out Panel Level Package,簡稱FOPLP)是近年來在半導體封裝領域興起的一種先進技術。它結合了扇出型封裝和面板級封裝的優點,為高性能、高集成度的半導體芯片提供了一種高效且成本較低的封裝解決方案。

2024-05-28 09:47:55 3731

3731

晶圓級封裝是一種先進的半導體封裝技術,被廣泛應用在存儲器、傳感器、電源管理等對尺寸和成本要求較高的領域中。在這些領域中,這種技術能夠滿足現代對電子設備的小型化、多功能、低成本需求,為半導體制造商提供了創新的解決方案,更好地應對市場的需求和挑戰。

2024-07-19 17:56:41 3194

3194 (Fan-Out Panel-Level Packaging,扇出型面板級封裝)技術,預計將于2025年第二季度正式開啟小規模出貨階段,標志著日月光在先進封裝領域的又一重大突破。

2024-07-27 14:40:32 1856

1856 電子發燒友網站提供《傳感器陣列扇出技術和實現.pdf》資料免費下載

2024-08-23 09:47:00 0

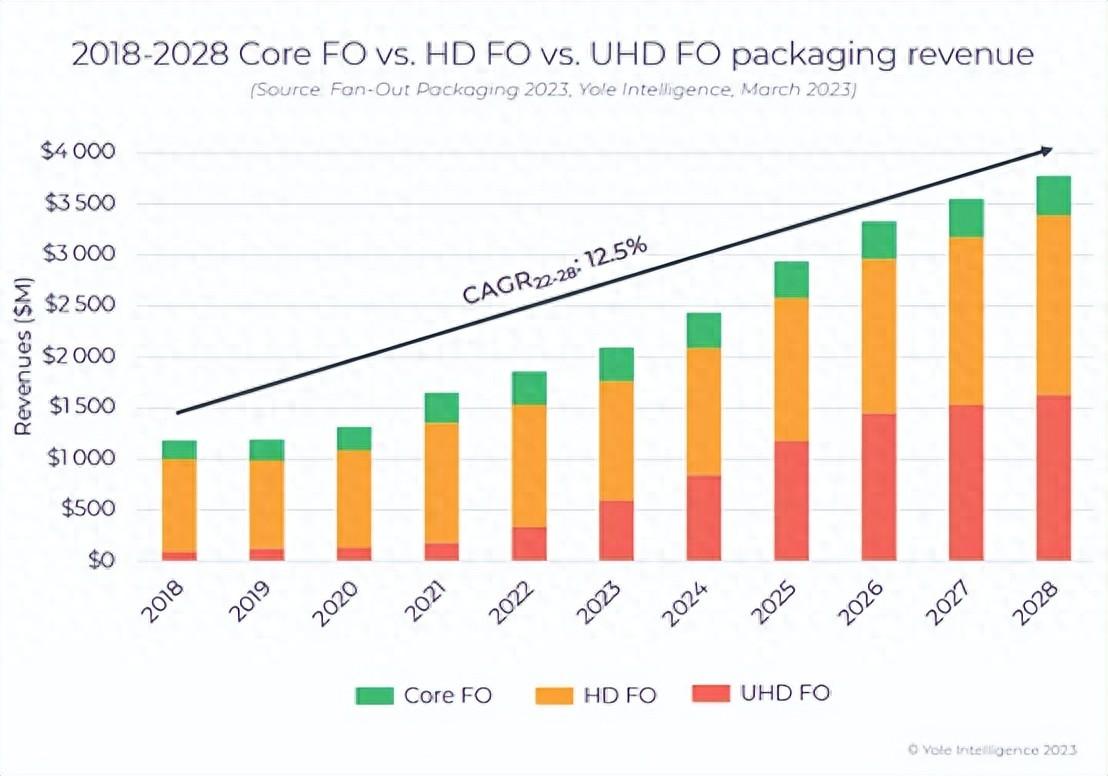

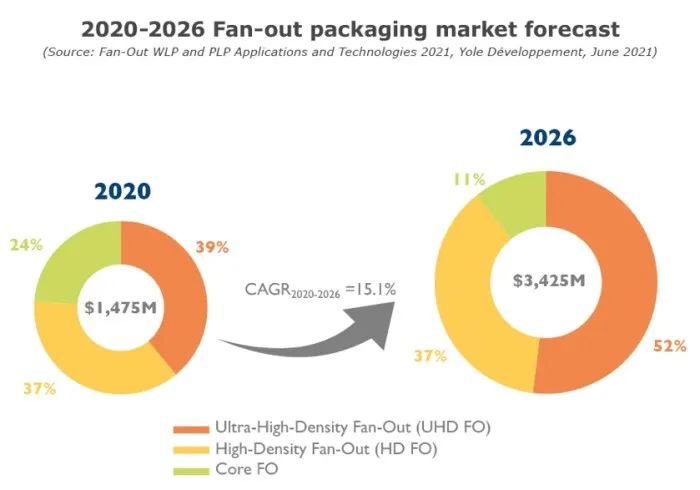

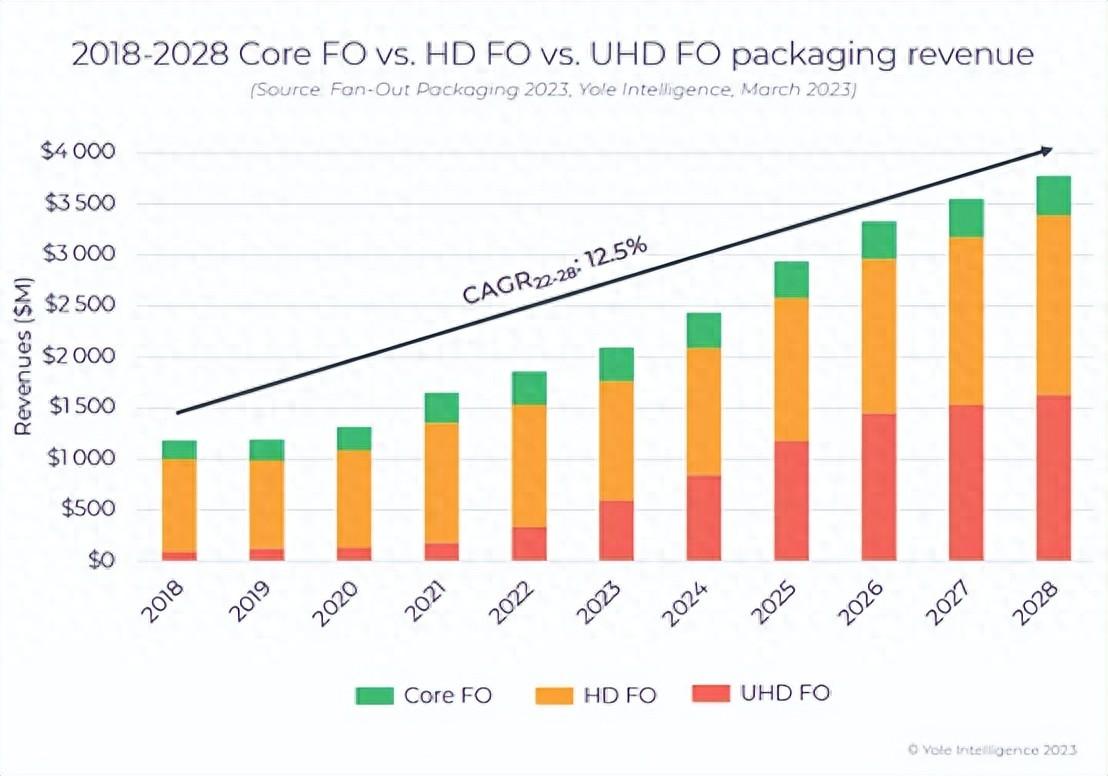

0 來源:深芯盟產業研究部 根據YOLE 2023年扇出型封裝市場報告數據,受高性能計算 (HPC) 和聯網市場對超高密度封裝的需求推動,扇出型封裝市場規模到2028 年將達到38 億美元。 *1未來五

2024-08-26 16:06:54 1540

1540

來源:華天科技 在半導體封裝領域, 扇出(Fan-Out)技術 正以其獨特的優勢引領著新一輪的技術革新。它通過將芯片連接到更寬廣的基板上,實現了更高的I/O密度和更優秀的熱性能。由于扇出型封裝不需要

2024-12-06 10:00:19 1367

1367 Advanced Packaging) - 4 Chiplet 異構集成(下) 先進封裝技術(Semiconductor Advanced Packaging) - 5 TSV 異構集成與等效熱仿真 隨著電子信息技術的快速發展,半導體電子行業及其基礎制造技術已成為過去半個世紀最重要的發展之一,集成

2024-12-06 11:37:46 3694

3694

(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP) 封裝技術從早期到現在的發展都是為了

2024-12-06 11:43:41 4730

4730

(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP) 先進封裝技術(Semiconductor Advanced Packaging) - ?7 扇出型板級封裝(FOPL

2024-12-24 10:57:32 3383

3383

(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP) 先進封裝技術(Semiconductor Advanced Pac

2024-12-24 10:59:43 3078

3078

多芯片封裝(Multi-Chip Packaging, MCP)技術通過在一個封裝中集成多個芯片或功能單元,實現了空間的優化和功能的協同,大幅提升了器件的性能、帶寬及能源效率,成為未來高性能計算

2024-12-30 10:36:47 1924

1924

(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP) 先進封裝技術(Semiconductor Advanced Pac

2025-01-08 11:17:01 3032

3032

日月光集團營運長吳田玉宣布,集團歷經十年研發,決定正式邁向面板級扇出型封裝(FOPLP)量產階段。為此,集團將斥資2億美元(約新臺幣64億元),在高雄設立專門的量產線。

2025-02-18 15:21:02 1332

1332 電子發燒友網站提供《一文解析工業互聯網.pptx》資料免費下載

2025-02-20 16:42:51 1

1 深入解析SN65LVEL11:高性能1:2 ECL扇出緩沖器 在電子設計領域,一款合適的緩沖器對于數據和時鐘信號的穩定傳輸至關重要。今天,我們就來詳細探討德州儀器(TI)的SN65LVEL11,這是

2025-12-25 13:45:02 129

129 深入解析RC190xx:PCIe Gen5/6高性能扇出緩沖器家族 在當今高速發展的電子科技領域,PCIe Gen5/6技術的應用越來越廣泛,對高性能扇出緩沖器的需求也愈發迫切。Renesas

2025-12-30 09:55:06 110

110 扇出型晶圓級封裝(FOWLP)的概念最早由德國英飛凌提出,自2016 年以來,業界一直致力于FOWLP 技術的發展。

2026-01-04 14:40:30 199

199

電子發燒友App

電子發燒友App

評論