由中國科學院微電子所、華進半導體共同出資成立的江蘇中科智芯集成科技有限公司的晶圓級扇出型(FO)封裝項目即將于2019年11月投產。

2018年3月,江蘇中科智芯集成科技有限公司成立,承接華進半導體晶圓級扇出型封裝產業化項目。中科智芯半導體封測項目位于徐州經濟技術開發區鳳凰灣電子信息產業園,占地50畝,投資20億元,項目分兩期建設。

2018年9月一期開工建設,投資5億元,建成后將可形成年月能為12萬片12英寸晶圓。主廠房于2018年11月底封頂;其他輔助建筑于2019年1月封頂,2019年7月凈化裝修施工基本完成,動力車間設備正在安裝,預計8月份開始設備安裝,9、10月份進行設備調試,11月初部分生產線投產。

中科智芯產品定位中高密度集成芯片扇出型(FO)封裝與測試,高頻率射頻芯片封裝的設計與制造。11月將陸續投產12英寸晶圓級扇出型封裝,逐步實現單芯片扇出型封裝、2D多芯片扇出型封裝、3D多芯片扇出型封裝量產。

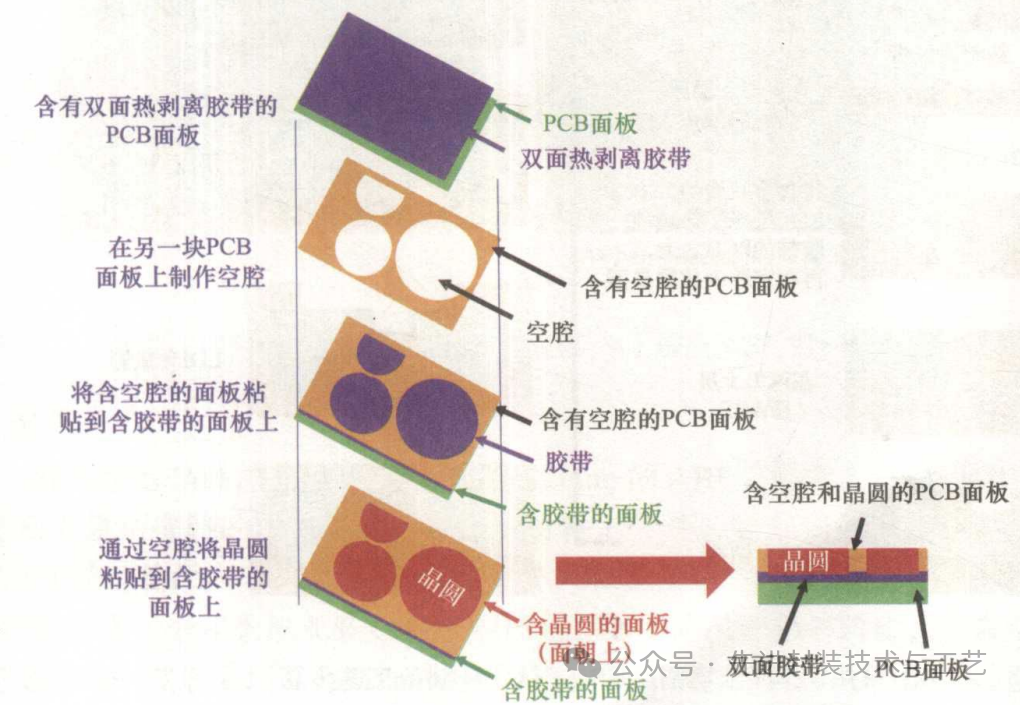

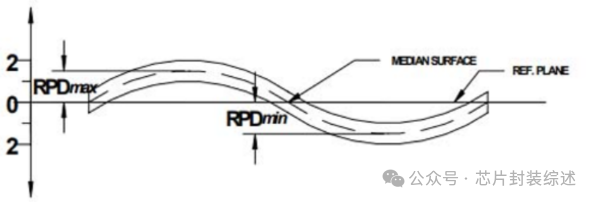

華進半導體相關人員表示,晶圓級扇出型封裝是最高性價比的集成電路封裝技術,無須使用印刷電路板,可直接在晶圓上實現芯片封裝。具體來說,第一,結合內嵌式印刷電路板技術的系統級封裝,雖符合移動設備小型化需求,然而供應鏈、產品良率(成本)存在很多問題;第二,硅穿孔(TSV)封裝技術可以實現產品良率的問題,但設計難度較大、制造成本極高。與上述兩種方案不同的晶圓級扇出封裝(Fan-Out)技術,可在單芯至多芯片的封裝中做到更高的集成度,而具有更好的電氣屬性,不僅降低封裝成本,并且讓系統計算速度加快,產生的功耗更小,更為重要的是,該技術能夠提供更好的散熱性能,并可以整合射頻元件,使網絡基帶性能更加優良。

鳳凰灣電子信息產業園內在中科智芯集成電路晶圓級封裝項目外,還引入了聯立LCD驅動芯片封裝、愛矽封測等項目。聯立LCD驅動芯片封裝項目擬建設具有月產能2.4萬片之8英寸芯片(晶圓凸塊及測試)、封裝(COG、COF)5千萬顆集成電路生產能力的生產線廠房正在進行內部裝修與機電安裝,預計年內投產;愛矽封測項目規劃年產5.4億個產品,正在進行機電安裝,預計年內投產。

中科智芯、聯立、愛矽等封裝項目投產后,將進一步補強徐州半導體封測產業鏈。

本文來源:麥姆斯咨詢

-

中科智芯

+關注

關注

2文章

4瀏覽量

1961

發布評論請先 登錄

什么是晶圓級扇入封裝技術

中科智芯晶圓級扇出型封裝即將投產,補強徐州短板

中科智芯晶圓級扇出型封裝即將投產,補強徐州短板

評論