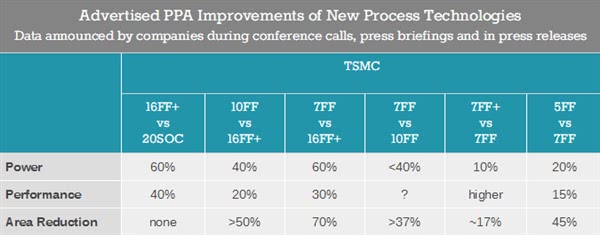

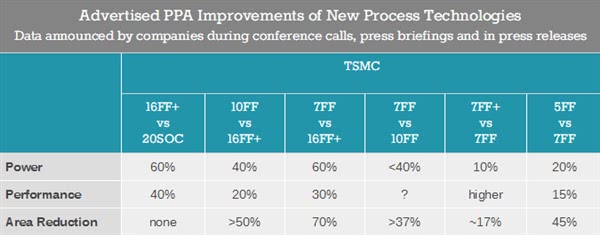

的性能和功耗優化。 采用5納米的新工藝,與公司的7納米工藝相比,相同的Cortex-A72內核可實現1.8倍的邏輯密度和15%的速度提升。 5nm工藝采用EUV光刻(極紫外曝光)制造,與公司以前的節點相比,通過簡化制造工藝和在同一發展階段實現出色的技術成熟度,可

2019-04-10 09:18:16 1470

1470 已經完成,現在可以為客戶提供樣品。通過在其基于極紫外(EUV)的工藝產品中添加另一個尖端節點,三星再次證明了其在先進晶圓代工市場的領導地位。 與7nm相比,三星的5nm FinFET工藝技術將邏輯區域效率提高了25%,功耗降低了20%,性能提高了10%,從而使其能夠擁有更多創

2019-04-18 15:48:47 7186

7186 共享一些設計規則。新的N5工藝將提供7nm變體以上的完整節點增加,并在10層以上的層中廣泛使用EUV技術,從而減少了7nm以上的生產總步驟。新的5nm工藝還采用了臺積電的下一代FinFET技術。 芯片命名 公開資料顯示,臺積電5nm EUV工藝可提供整體邏輯密度增加約1.84倍,功率

2019-12-13 11:18:57 5736

5736 TSMC 表示,其 5nm EUV 可將密度提升約 1.84 倍、能效提升 15%(功耗降低 30%)。當前測試的芯片有 256 Mb SRAM 和一些邏輯器件,平均良率為 80%、峰值為 90% 。

2019-12-16 08:41:30 6280

6280 TSMC在FinFET工藝量產上落后于Intel、三星,不過他們在10nm及之后的工藝上很自信,2020年就會量產5nm工藝,還會用上EUV光刻工藝。

2016-07-18 10:47:09 1381

1381 · 新思科技Custom Design Platform為三星7LPP工藝技術提供經認證的工具、PDK、仿真模型、運行集(runsets)以及定制參考流程。

· 新思科技Custom

2018-07-18 11:46:35 8001

8001 在7nm及以下節點上,臺積電的進展是最快的,今年量產7nm不說,最快明年4月份就要試產5nm EUV工藝了,不過這個節點的投資花費也是驚人的,臺積電投資250億美元建廠,5nm芯片設計費用也要比7nm工藝提升50%。

2018-10-08 09:52:33 4230

4230 10月10日晚間消息,著名半導體制造公司臺積電宣布了有關極紫外光刻(EUV)技術的兩項重磅突破,一是首次使用7nm EUV工藝完成了客戶芯片的流片工作,二是5nm工藝將在六個月后開始試產!

2018-10-11 11:45:23 4223

4223 1月12日晚間,三星舉辦了全球線上發布會,正式發布了 5nm 芯片 Exynos 2100。Exynos 2100 是三星首款集成 5G 的移動芯片組,基于 5nm EUV 工藝。與采用 7nm 工藝的前代產品相比,Exynos 2100 功耗降低 20%,整體性能提高了 10%。

2021-01-13 11:06:10 3594

3594 5nm工藝。不過,最近有消息傳出,三星遇到麻煩了,其5nm工藝的良率竟然低于50%。 韓國媒體報道,三星電子華城園區V1廠,最近面臨晶圓代工良率改善難題,5nm等部分工藝良率低于50%。 三星華城園區共有V1、S3及S4等晶圓廠,其中V1為EUV專用廠,于201

2021-07-05 18:35:59 4334

4334 3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是

2023-05-19 16:25:12 1405

1405

基于10nm++開發7nm工藝、基于7nm設計開發5nm工藝,基于5nm工藝來開發3nm工藝,毫無疑問,每一個“+”或者“++”所擁有的技術更新都將有可能進入下一代節點的設計之中。 在7nm節點之后

2020-07-07 11:38:14

是通過提升技術成本來平衡工序成本和周期成本。例如,按照格羅方德的測算,啟用EUV技術,在7nm和5nm節點,都僅需要1個光罩即可生產。這樣理論上來說,就可以起到簡化工藝流程,減少生產周期的作用。對此,芯謀

2017-11-14 16:24:44

想問一下,TSMC350nm的工藝庫是不是不太適合做LC-VCO啊,庫里就一個電容能選的,也沒有電感可以選。(因為課程提供的工藝庫就只有這個350nm的,想做LC-VCO感覺又不太適合,好像只能做ring-VCO了)請問350nm有RF工藝嘛,或者您有什么其他的工藝推薦?

2021-06-24 08:06:46

Sic mesfet工藝技術研究與器件研究針對SiC 襯底缺陷密度相對較高的問題,研究了消除或減弱其影響的工藝技術并進行了器件研制。通過優化刻蝕條件獲得了粗糙度為2?07 nm的刻蝕表面;犧牲氧化

2009-10-06 09:48:48

從7nm到5nm,半導體制程芯片的制造工藝常常用XXnm來表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工藝。所謂的XXnm指的是集成電路的MOSFET晶體管柵極

2021-07-29 07:19:33

Research、東京電子和中微半導體,而通過臺積電5nm工藝認證的則更少。在這個領域,中國大陸的中微半導體取得了可喜的進步,其5nm蝕刻機已經打入臺積電供應鏈。中微半導體主要生產蝕刻機、MOCVD等設備

2020-03-09 10:13:54

業界對哪種半導體工藝最適合某一給定應用存在著廣泛的爭論。雖然某種特殊工藝技術能更好地服務一些應用,但其它工藝技術也有很大的應用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-20 08:01:20

臺積電宣布5nm基本完工開始試產:面積縮小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

求TSMC90nm的工藝庫,請問可以分享一下嗎?

2021-06-22 06:21:52

新思科技與中芯國際合作推出用于中芯65納米低漏電工藝技術的、獲得USB標志認證的DesignWareUSB 2.0 nanoPHY

通過芯片驗證的DesignWare PHY IP

2010-05-20 17:39:09 899

899 隨著芯片微縮,開發先進工藝技術的成本也越來越高。TSMC對外發言人孫又文表示,臺積電會繼續先進工藝技術節點的投入和開發,今年年底臺積電將推出20nm工藝

2012-08-30 14:34:30 2301

2301 Mentor Graphics公司日前宣布Calibre LFD(光刻友好設計)光刻檢查工具已獲得TSMC的20nm IC制造工藝認證。 Calibre LFD可對熱點進行識別,還可對設計工藝空間是否充足進行檢查。光學臨近校正法

2012-09-29 10:30:46 2224

2224 電子發燒友網核心提示 :Mentor Graphics公司日前宣布Calibre LFD(光刻友好設計)光刻檢查工具已獲得TSMC的20nm IC制造工藝認證。 Calibre LFD可對熱點進行識別,還可對設計工藝空間是否充足進

2012-10-08 16:00:14 1265

1265 FinFET制程的設計規則手冊(DRM)第0.5版的認證,同時從即刻起可以提供一套TSMC 16-nm可互通制程設計套件(iPDK)。憑借其對iPDK標準強大的支持,Synopsys的Laker定制解決方案為用戶提供了從180-nm到16-nm的多種TSMC工藝技術的全面對接。

2013-09-23 14:45:30 1379

1379 ? Analog FastSPICE? 電路驗證平臺已完成了電路級和器件級認證,Olympus-SoC? 數字設計平臺正在進行提升,以幫助設計工程師利用 TSMC 10nm FinFET 技術更有效地驗證和優化其設計。10nm V1.0 工藝的認證預計在 2015 年第 4 季度完成。

2015-09-21 15:37:10 1664

1664 Technology (12FFC) 和最新版本 7nm FinFET Plus 工藝的認證。Nitro-SoCTM 布局和布線系統也通過了認證,可以支持 TSMC 的 12FFC 工藝技術。

2017-10-11 11:13:42 3456

3456 EUV被認為是推動半導體產業制造更小芯片的重要里程碑,但是根據目前的EUV微影技術發展進程來看,10奈米(nm)和7nm制程節點已經準備就緒,就是5nm仍存在很大的挑戰。

2018-01-24 10:52:39 2922

2922

TSMC最新版5nm FinFET 和 7nm FinFET Plus 工藝的認證。Mentor 同時宣布,已更新了 Calibre nmPlatform 工具,可支持TSMC的晶圓堆疊封裝 (WoW)技術

2018-05-17 15:19:00 4493

4493 Synopsys設計平臺用于高性能、高密度芯片設計 重點: Synopsys設計平臺獲得TSMC工藝認證,支持高性能7-nm FinFET Plus工藝技術,已成功用于客戶的多個設計項目。 針對

2018-05-17 06:59:00 5644

5644 Intel 10nm工藝還在苦苦掙扎,臺積電和三星已經開始量產7nm,下一步自然就是5nm,臺積電近日也首次公開了5nm的部分關鍵指標,看起來不是很樂觀。 明年,臺積電的第二代7nm工藝會在部分非

2018-05-15 14:35:13 4690

4690

5nm、4nm、3nm工藝,直逼 這兩年,三星電子、臺積電在半導體工藝上一路狂奔,雖然有技術之爭但把曾經的領導者Intel遠遠甩在身后已經是不爭的事實。

2018-06-08 07:12:00 4661

4661 Synopsys Synopsys近日宣布, Synopsys 設計平臺獲得TSMC最新版且最先進的5nm工藝技術認證,可用于客戶先期設計。通過與TSMC的早期密切協作,IC CompilerII

2018-06-01 09:35:00 4920

4920 10月10日晚間消息,著名半導體制造公司臺積電宣布了有關極紫外光刻(EUV)技術的兩項重磅突破,一是首次使用7nm EUV工藝完成了客戶芯片的流片工作,二是5nm工藝將在六個月后開始試產!

2018-10-11 08:44:33 5539

5539 基于7nm工藝技術的控制器和PHY IP具有豐富的產品組合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解決方案支持TSMC 7nm工藝技術所需的先進汽車設計規則,滿足可靠性和15年汽車運行要求。

2018-10-18 14:57:21 7324

7324 IC Compiler II和Design Compiler Graphical提供了統一流程,實現最低功耗、最佳性能和最優面積。

StarRC、PrimeTime和PrimeTime PX支持全流程設計實現并提供時序和功耗分析的signoff支持。

2018-10-23 14:29:14 6019

6019 新思科技(Synopsys)推出支持TSMC 7nm FinFET工藝技術的汽車級DesignWare Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2

2018-11-13 16:20:23 2042

2042 國內的中微電子已經研發成功5nm等離子刻蝕機,并通過了臺積電的認證,將用于全球首條5nm工藝。

2018-12-20 08:55:26 26103

26103 工智能(AI)市場。 臺積電表示,相較7nm制程,5nm的微縮功能在Arm的Cortex-A72核心上能夠提供1.8倍的邏輯密度,性能可提升15%。此外,5nm制程將會完全采用極紫外光(EUV)微影技術,因此可帶來EUV技術提供的制程簡化效益。 臺積電指出,5nm制程能提供芯片設計業者

2019-04-04 11:16:02 3456

3456 臺積電指出,5nm制程將會完全采用極紫外光(EUV)微影技術,因此可帶來EUV技術提供的制程簡化效益。5nm制程能夠提供全新等級的效能及功耗解決方案,支援下一代的高端移動及高效能運算需求的產品。目前,其他晶元廠的7nm工藝尚舉步維艱,在5nm時代臺積電再次領先。

2019-04-04 16:05:57 2115

2115 包括7nm批量生產和6nm產品的流片, 三星電子在基于EUV技術的先進制程工藝開發上取得重大進展 4月16日,三星電子宣布,其5nm FinFET( 鰭式場效應晶體管)工藝技術已經開發完成,該技術可

2019-04-18 20:48:54 636

636 新思科技近日宣布,三星(Samsung Electronics)認證了新思科技Fusion Design Platform?,用于三星采用EUV光刻技術的5納米Low-Power Early(早期

2019-06-12 13:48:35 4326

4326 臺積電計劃在明年第一季度開始量產5nm芯片,5nm較7nm晶體數量將增加1.8倍,性能提升15%。不過在今年,2019款iPhone還是繼續采用7nm工藝制程的芯片,性能較上代的A12有所提升。而高通下一代旗艦芯片驍龍865將由三星代工,也是7nm EUV工藝制造。

2019-06-17 10:36:28 1404

1404 近日,全球知名的EDA工具廠商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學習平臺設計取得了重大突破,這將為三星后續5nm、4nm、3nm工藝的量產和良品率的提升奠定堅實基礎。

2019-07-09 17:13:48 5070

5070 全球知名的EDA工具廠商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先進工藝的良率學習平臺設計取得了重大突破

2019-07-11 14:49:47 3943

3943 采用極紫外(EUV)光刻技術的Cadence 數字全流程解決方案已通過Samsung Foundry 5nm早期低功耗版(5LPE)工藝認證。

2019-07-11 16:36:47 4273

4273 近兩年先進半導體制造主要是也終于迎來了EUV光刻機,這也使7nm之后的工藝發展得以持續進行下去。臺積電和三星都對自家工藝發展進行了規劃,現在兩家已經逐步開始進行7nm EUV工藝的量產,隨后還有5nm工藝及3nm工藝。

2019-07-24 11:45:42 3224

3224 7nm+ EUV節點之后,臺積電5nm工藝將更深入地應用EUV極紫外光刻技術,綜合表現全面提升,官方宣稱相比第一代7nm EDV工藝可以帶來最多80%的晶體管密度提升,15%左右的性能提升或者30%左右的功耗降低。

2019-09-26 14:49:11 5945

5945 日前,高通發布了新一代旗艦平臺驍龍865、主流平臺驍龍765/765G,分別采用臺積電7nm、三星8nm工藝制造。那么,高通為何在兩個平臺上使用兩種工藝?驍龍865為何沒用最新的7nm EUV?5nm方面高通有何規劃?

2019-12-09 17:23:23 7069

7069 在全球晶圓代工市場上,已經沒有公司能超過臺積電了,他們的16/12nm訂單居高不下,7nm及改良版7nm EUV工藝如火如荼,下一代的5nm工藝進展也非常順利,據悉現在的良率就比7nm工藝初期要好了。

2019-12-01 09:57:11 1047

1047 高通昨晚發布了第三代5G基帶芯片——驍龍X50,使用的是5nm工藝。高通對5nm工藝的代工廠來源守口如瓶,不過外媒報道稱驍龍X60首發了三星的5nm工藝。

2020-02-19 15:09:36 3574

3574 臺積電作為5nm芯片生產規模最大的代工廠之一,根據其計劃,5nm工藝芯片將在今年上半年正式量產。

2020-03-06 13:54:30 5366

5366 臺積電將會在今年年中開始進行5nm EUV工藝的量產,屆時臺積電的主要5nm工藝客戶有蘋果和華為兩家。根據MyDrivers報道,華為的下一代旗艦處理器可能命名為麒麟1020,有5nm EUV工藝加持后性能會比麒麟990 5G SoC提升50%!

2020-03-07 15:52:09 3150

3150 臺積電5nm制造工藝基于ULV,也就是紫外線光刻技術實現,之前的7nm EUV工藝同樣也是基于這項技術。那么制程的縮小又意味著什么?相比于7nm工藝,5nm工藝可以進一步提升芯片的晶體管密度,提升性能并降低功耗,可廣泛用于PC、智能手機等設備的元器件中。

2020-03-12 14:10:44 3184

3184 在開發5nm制程技術僅一年之后,三星就開始了 5nm EUV(極紫外)生產線的建設。三星公司希望在2030年之前擊敗臺積電,并成為半導體業務的領導者。

2020-03-12 14:30:36 2526

2526 2020年,全球最先進的半導體工藝要從7nm升級到5nm了,臺積電最近上半年就開始量產5nm EUV工藝,而三星也加碼投資,預計6月底完成5nm EUV生產線。

2020-03-13 08:35:01 3238

3238 臺積電上周發布了3月及Q1季度財報,營收同比大漲了42%,淡季不淡。不過接下來的日子半導體行業可能不太好過了,ASML的EUV光刻機已經斷貨,要延期交付,好在臺積電今年已經在5nm工藝上搶先三星了。

2020-04-15 08:55:17 3633

3633 4月20日消息,據國外媒體報道,按計劃,在7nm工藝量產近兩年之后,芯片代工商臺積電今年將大規模量產5nm芯片,臺積電方面日前也透露,他們的5nm工藝已經量產,良品率也非常可觀。

2020-04-20 17:00:03 3185

3185 ,雖然整體多少還是受到疫情影響,但臺積電強調5nm工藝技術影響程度不大,僅接下來的3nm工藝試產可能會有延后情況。

2020-04-21 15:56:23 2913

2913 CFan曾在《芯希望來自新工藝!EUV和GAAFET技術是個什么鬼?》一文中解讀過EUV(極紫外光刻),它原本是用于生產7nm或更先進制程工藝的技術,特別是在5nm3nm這個關鍵制程節點上,沒有

2020-09-01 14:00:29 3544

3544 基于5nm EUV工藝。 到底哪家的5nm工藝更穩,要等雙雙有終端上市后才能掰一掰腕子。 另外,AMD的Zen3和RDNA2都沒有上馬5nm,而是7nm增強版。除了

2020-09-17 13:58:01 979

979 芯片是三星與vivo聯手定制,有望被vivo X60系列首發。 和三星去年同期推出的Exynos 980(8nm)相比,Exynos 1080在最新5nm工藝的加持下可以讓性能提升14%,功耗降低30

2020-11-14 09:58:05 14683

14683 (功耗、性能和面積)優勢,同時加快產品上市時間 ● 新思科技進一步強化關鍵產品,以支持TSMC N3制造的進階要求 新思科技(Synopsys)近日宣布,其數字和定制設計平臺已獲得TSMC 3nm制造技術驗證。此次驗證基于TSMC的最新設計參考手冊(DRM)和工藝設計工具包(

2020-10-14 10:47:57 2543

2543 重點 ● TSMC認證基于新思科技3DIC Compiler統一平臺的CoWoS和InFO設計流程 ● 3DIC Compiler可提高先進封裝設計生產率 ● 集成Ansys芯片封裝協同分析解決方案

2020-10-14 11:11:21 2815

2815 5nm工藝是7nm之后臺積電又一項行業領先、可帶來持久營收的重要工藝,隨著投產時間的延長,其產能也會有明顯提升,會有更多的客戶獲得產能,5nm工藝為臺積電帶來的營收也會大幅增加。

2020-10-16 16:40:02 2297

2297 在先進半導體工藝上,臺積電已經一騎絕塵了,其他人望不到尾燈了,今年量產了5nm,明年就輪到3nm了。

2020-10-17 09:12:38 2410

2410 為臺積電帶來了近 10 億美元的營收。 同此前的 7nm 工藝一樣,臺積電的 5nm 工藝也不只一代,他們還將推出第二代的 5nm 工藝,也就是他們所說的 N5P。 在 8 月底的全球技術論壇期間,臺積電曾披露,同第一代 5nm 工藝相比,第二代 5nm 工藝所制造的芯片,理論上性能將提升

2020-11-06 16:19:02 2235

2235 蘋果的iPhone 12系列及華為的Mate40系列都用上了5nm工藝,A14、麒麟9000是臺積電5nm工藝最早的兩個產品之一,接下來三星、聯發科的5nm旗艦芯片也快了。

2020-11-09 10:49:19 2076

2076 1080處理器是三星首款基于最新的5nm EUV FinFET工藝制造的處理器,進一步提高設備的電源效率和性能。 三星Exynos在11月12日在上海舉行首場國內線下發布會;據介紹,vivo將首發搭載

2020-11-12 18:13:20 4092

4092 Shin稱,通過采用和集成現有的最先進技術,例如5nm EUV和最新的處理內核,Exynos 1080可以在移動設備中提供5G,設備內置AI技術

2020-11-12 16:48:02 2150

2150 制造工藝EUV(極紫外光刻)。Exynos 1080 所采用的 5nm EUV 工藝與 8nm LPP(成熟低功耗)相比,性能提升 14%,功耗降低 30%;與 7nm DUV(深紫外光刻)相比,

2020-11-12 16:48:29 2309

2309 今天高通的驍龍888 5G平臺刷屏了,不論CPU還是GPU、AI提升都很大,制程工藝也升級到了5nm。只不過高通在發布會上對5nm工藝的代工廠一直閉口不提,今天才確認是三星5nm工藝。

2020-12-03 09:03:48 2892

2892 昨天高通的驍龍888 5G平臺刷屏了,不論CPU還是GPU、AI提升都很大,制程工藝也升級到了5nm。只不過高通在發布會上對5nm工藝的代工廠一直閉口不提,今天才確認是三星5nm工藝。

2020-12-03 10:37:02 5772

5772 ,AMD、NVIDIA等公司也會跟進5nm,不過至少要到2021年底了,在此之前臺積電的5nm工藝會有一段空缺,有報告稱明年Q2季度5nm利用率會降至80%以下。 誰能來填補這個空缺?礦機廠商現在已經找到機會了,一方面是最近比特幣價格大漲,數字貨幣市場全面復興

2020-12-22 14:12:28 2103

2103 從 2020 年下半年開始,各家手機芯片廠商就開始了激烈的 5nm 芯片角逐,蘋果、華為、高通、三星相繼推出旗艦級 5nm 移動處理器,并宣稱無論是在性能上還是在功耗上都有著優秀的表現。 不過

2021-01-20 14:57:54 42511

42511

昨天聯發科發布了天璣1200、天璣1000系列處理器,使用的是臺積電6nm EUV工藝,相當于7nm的改進版,而友商的旗艦5G處理器大都說用了更先進的5nm工藝,甚至還有更強的X1架構。

2021-01-21 15:38:28 2067

2067 5nm是EUV(極紫外線)光刻機能實現的目前最先進芯片制程工藝,也是智能手機廠商爭搶的宣傳賣點,進入2020年下半年后,蘋果A14、麒麟9000、驍龍888等5nm工藝芯片相繼粉墨登場。

2021-01-25 13:45:56 10690

10690 從制程工藝來講,以手機為代表的消費電子產品要遠遠領先于車載芯片。但在昨晚,這一局面發生了改變。 高通發布了第4代驍龍汽車數字座艙平臺,并帶來了全球第一款5nm汽車芯片,為下一代汽車架構演進指明方向

2021-01-27 11:48:44 3121

3121 作為臺積電的頭號客戶,蘋果每年都可以用上臺積電最先進的工藝,iPhone 12的A14又是首發5nm工藝。 上馬新工藝不是簡單一句話的事,因為臺積電的新工藝價格越來越貴,此前CSET分析過不同工藝

2021-01-28 09:44:06 1997

1997 功耗是芯片制造工藝演進時備受關注的指標之一。比起7nm工藝節點,5nm工藝可以使產品性能提高15%,晶體管密度最多提高1.8倍。三星獵戶座1080、華為麒麟9000、驍龍888和蘋果的A14芯片都

2021-02-04 14:33:10 8222

8222 SoC 設計與應用技術領導廠商Socionext Inc.(以下“Socionext”)宣布,公司將采用臺積電最新5nm制程工藝(N5P)用于下一代汽車定制芯片業務。Socionext汽車定制芯片

2021-02-05 11:50:27 2703

2703 )宣布,其數字和定制/模擬流程已獲得 TSMC N3 和 N4 工藝技術認證,支持最新的設計規則手冊(DRM)。通過持續合作,Cadence 和 TSMC 發布了 TSMC N3 和 N

2021-10-26 15:10:58 3128

3128 ”)已在5nm、4nm和3nm工藝技術中認證了新思科技的PrimeLib統一庫表征和驗證解決方案,可滿足高性能計算、5G、汽車、超連接、以及人工智能芯片等下一代設計的高級計算需求。此次認證還包括

2021-11-09 16:59:26 2372

2372 技(Synopsys)近日宣布其數字定制設計平臺已獲臺積公司N3制程技術認證,雙方將共同優化下一代芯片的功耗、性能和面積(PPA)。基于多年的密切合作,本次經嚴格驗證的認證是基于臺積公司最新版本的設計規則手冊(DRM)和制程設計套件(PDK)。此外,新思科技

2021-11-16 11:06:32 2328

2328 Siemens Digital Industries Software 宣布,其用于模擬、數字和混合信號 IC 設計的電源完整性分析的全新 mPower? 解決方案現已通過 TSMC 的 N7 和 N5 工藝技術認證。

2022-03-16 14:36:14 2279

2279 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其數字和定制 / 模擬設計流程已獲得 TSMC N3E 和 N4P 工藝認證,支持最新的設計規則手冊(DRM)。

2022-06-17 17:33:05 6035

6035 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其面向 TSMC N7、N6 和 N5 工藝技術 PCI Express?(PCIe?) 5.0 規范的 PHY 和控制器

2022-06-23 10:17:30 2557

2557 新思科技數字和定制設計流程獲得臺積公司的N3E和N4P工藝認證,并已推出面向該工藝的廣泛IP核組合。

2022-07-12 11:10:51 1782

1782 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發

2023-05-09 10:09:23 2046

2046 最新節點進行優化 中國上海, 2023 年 7 月 5 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,其數字和定制/模擬流程已通過 Samsung Foundry

2023-07-05 10:12:14 1327

1327 流程現已通過 Intel 16 FinFET 工藝技術認證,其 Design IP 現可支持 Intel Foundry Services(IFS)的此工藝節點。 與此同時,Cadence 和 Intel 共同發布

2023-07-14 12:50:02 1450

1450

Cadence近日宣布,其數字和定制/模擬流程在Intel的18A工藝技術上成功通過認證。這一里程碑式的成就意味著Cadence的設計IP將全面支持Intel的代工廠在這一關鍵節點上的工作,并提

2024-02-27 14:02:18 1332

1332 概倫電子(股票代碼:688206.SH)近日宣布其新一代大容量、高性能并行SPICE仿真器NanoSpice通過三星代工廠3/4nm工藝技術認證,滿足雙方共同客戶對高精度、大容量和高性能的高端電路仿真需求。

2024-06-26 09:49:14 1378

1378 )計劃從2025年1月起對3nm、5nm先進制程和CoWoS封裝工藝進行價格調整。 先進制程2025年喊漲,最高漲幅20% 其中,對3nm、5nm等先進制程技術訂單漲價,漲幅在3%到8%之間,而AI相關高性能計算產品的訂單漲幅可能高達8%到10%。此外,臺積電還計劃對CoWoS先進封裝服務進行漲

2025-01-03 10:35:35 1088

1088

電子發燒友App

電子發燒友App

評論