5nm是EUV(極紫外線)光刻機能實現的目前最先進芯片制程工藝,也是智能手機廠商爭搶的宣傳賣點,進入2020年下半年后,蘋果A14、麒麟9000、驍龍888等5nm工藝芯片相繼粉墨登場。

然而,公開的信息顯示,無論A14、麒麟9000,還是驍龍888,均被曝出芯片的實際功耗發熱與廠商宣傳的美好相差甚遠,一時間,“5nm芯片集體翻車”的話題成為網絡熱點。

驍龍888功耗等于低壓酷睿?

根據報道,5nm芯片最讓人詬病的,是性能雖然有所提升,但功耗卻比7nm的明顯增加,這其中表現最差的就是驍龍888,被調侃為“火龍888”。

數碼評測媒體極客灣對驍龍888、驍龍865、驍龍855測試的功耗數據表明,單核功耗上,驍龍865最低,為2.3瓦,其次是驍龍855的2.4瓦,驍龍888最高,達3.3瓦,相比驍龍865高了1瓦,高出幅度達43.5%。多核功耗方面,最低的依然是驍龍865,為5.9瓦,其次是驍龍855的6.1瓦,驍龍888依然落在最后,功耗高達7.8瓦,是驍龍865的1.32倍。

驍龍888多核功耗高達7.8瓦是個什么概念?英特爾第11代低壓酷睿i7處理器的功耗在7——15瓦,可用于超輕輕薄筆記本電腦(在無風扇散熱時,功耗鎖定為7瓦)。也就是說,驍龍888的多核功耗已經相當于一顆第11代低壓酷睿i7處理器,但需要明確的是,低壓酷睿i7處理器采用的是10nm工藝制程,落后臺積電、三星的5nm不少。

英特爾處理器采用復雜指令集,理論上相比采用精簡指令集的驍龍888更為耗電,但驍龍888在占據工藝先進至少一代的優勢下,功耗竟然相當于英特爾低壓酷睿。不知道英特爾看到這里會是什么心情。

驍龍888功耗猛增,最直觀的體驗就是,手機如果運行較大型的游戲,發熱就比較明顯。極客灣的數據表明,在某款游戲的測試中,玩了20分鐘后,小米11背面溫度達到了48℃,而搭載驍龍865的小米10在相同的測試環境下,溫控表現更好只有41℃。

愛范兒對搭載A14芯片的iPhone12運行《原神》游戲測試表明,20分鐘后,手機背面最高溫度達到47℃,接近小米11。

5nm的芯片在制程工藝上更先進,為何功耗表現卻落后于7nm芯片?答案是和芯片內部的晶體管漏電有直接關系。

為何晶體管漏電是元兇?

A14、驍龍和麒麟等手機SoC芯片屬于數字集成電路,而隨著制造工藝的不斷進步,集成電路的功耗越來越復雜,但總體可分為電路邏輯狀態轉換產生的動態功耗,以及CMOS晶體管各種泄露電流產生的靜態功耗(又稱漏電流功耗)。

在芯片進入深亞微米工藝時代之前,動態功耗一直是芯片設計關注的焦點,但在進入深亞微米工藝時代之后,動態功耗在總功耗中的比例越來越小,靜態功耗的比例則越來越大。

當芯片制造工藝進入納米時代后,漏電流功耗對整個功耗的影響已經變得非常顯著。有研究表明,在90nm工藝的電路中,靜態功耗可以占到總功耗的40%以上。

究其原因,是因為集成電路每一代制造工藝的進步,都是以縮短CMOS晶體管的溝道長度為目標,7nm工藝指的就是指溝道長度。溝道長度不斷縮短,使得電源電壓、閾值電壓、柵極氧化層厚度等工藝參數也在不斷地按比例縮小,直接導致短溝道效應(SCE)、柵極隧穿電流、結反偏隧穿電流等漏電流機制越來越顯著,表現為芯片漏電流功耗不斷上升。

有研究表明,當晶體管的溝道長度從130nm縮短到90nm時,即縮小30.77%,漏電流功耗上升大約39.25%,但縮短到45nm,即縮小65.4%時,漏電流功耗上升大約273.28%(具體見下圖)。

也就是說,漏電流功耗和縮小的溝道長度之間不是簡單的比例關系,即使溝道長度縮短一點,漏電流功耗也會有一個數量級的增長,而且隨著溝道長度越來越短,漏電流功耗增長越來越快。

如果復盤芯片制造歷史,會發現漏電流功耗曾長期困擾英特爾、三星和臺積電等制造大廠。

臺積電為何被稱臺漏電?

長期以來,芯片制造大廠一直在和漏電流功耗作斗爭,每有進展,都是值得大書特書的新聞,比如英特爾。

相反,臺積電2010年剛推出28nm工藝制程時,由于技術不成熟,漏電流功耗高,導致芯片的功耗大到難以接受,被市場調侃為“臺漏電。”有長達6年時間,都摘不掉這頂帽子。

在當時,如何壓制漏電流功耗幾乎可以決定芯片工藝制程賽道上選手的身位。彼時,英特爾還是制造技術大拿,率先通過Gate-last技術壓制了漏電流功耗,臺積電則走了一些彎路,沿用IBM的Gate-first 技術,但效果不佳,在28nm上栽了跟斗,后在蔣尚義的主導下,改走英特爾Gate-last技術路線,才算解決漏電流功耗過高難題。

2011年第4季度,歷經波折后,臺積電終于量產成熟可靠的28nm制程。三星本來在32納米制程也采用Gate-first 技術,但后來在28 納米制程時,快速切換到Gate-Last 路線,之后的14納米也基于Gate-Last。

據說,三星是通過梁孟松解決漏電流功耗問題,成功縮短與臺積電的工藝差距。結果引發臺積電起訴梁孟松,迫使后者離開三星半導體,輾轉到中芯國際。

由此可見,壓制晶體管漏電流功耗有多重要。

為何老邁的技術不退休?

臺積電、三星和英特爾之所以能壓制漏電流功耗問題,主要原因是采用了創新的鰭式場效應晶體管(簡稱FinFET,見附圖),以替代傳統的平面式晶體管。但由加州大學伯克利分校胡正明教授發明的鰭式場效應晶體管(FinFET),通過局部技術改良,從28nm工藝制程一直沿用至今,可謂發揮到了極限。隨著制程工藝進入EUV時代,漏電流功耗重新成為挑戰。

在7nm時,老邁的鰭式場效應晶體管(FinFET)技術就應該謝幕了,由環繞柵極晶體管(GAAFET)接替。但由于技術風險和成本壓力,大廠們在5nm時代仍不得不使用老邁的鰭式場效應晶體管(FinFET)技術,結果就是如前文所述,5nm的芯片漏電流功耗飆漲,在功耗上集體翻車,幾乎消耗掉制程工藝進步的紅利。也可以看出,芯片制造技術每往前跨一步,其實都極為不易。

那么,鰭式場效應晶體管(FinFET)會應用到什么時候?

從公開的信息看,英特爾計劃在5nm(接近臺積電3nm工藝)時切換到環繞柵極晶體管(GAAFET),臺積電則計劃3nm之后再說,三星為了追平與臺積電的工藝差距,決定豪賭一把,搶先臺積電一步,在3nm時就采用環繞柵極晶體管(GAAFET)。

總之,在環繞柵極晶體管(GAAFET)正式擼起袖子上陣之前,芯片的發熱仍然會是一個問題。

責任編輯:tzh

-

處理器

+關注

關注

68文章

20255瀏覽量

252300 -

芯片

+關注

關注

463文章

54010瀏覽量

466089 -

晶體管

+關注

關注

78文章

10396瀏覽量

147764

發布評論請先 登錄

臺積電2nm芯片成本暴漲80%!蘋果A20、高通驍龍旗艦芯片集體漲價

1600TOPS!美國新勢力車企自研5nm芯片,轉用激光雷達硬剛特斯拉

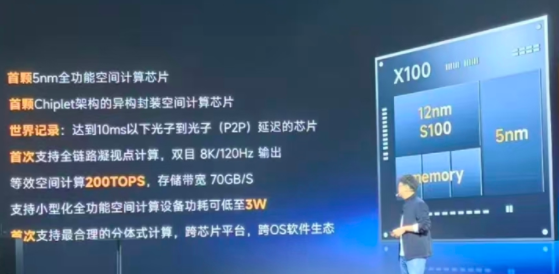

國內首顆5nm MR芯片問世: Chiplet架構、9ms P2P延遲打破紀錄

歐洲之光!5nm,3200 TFLOPS AI推理芯片即將量產

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

今日看點丨蔚來自研全球首顆車規5nm芯片!;沃爾沃中國區啟動裁員計劃

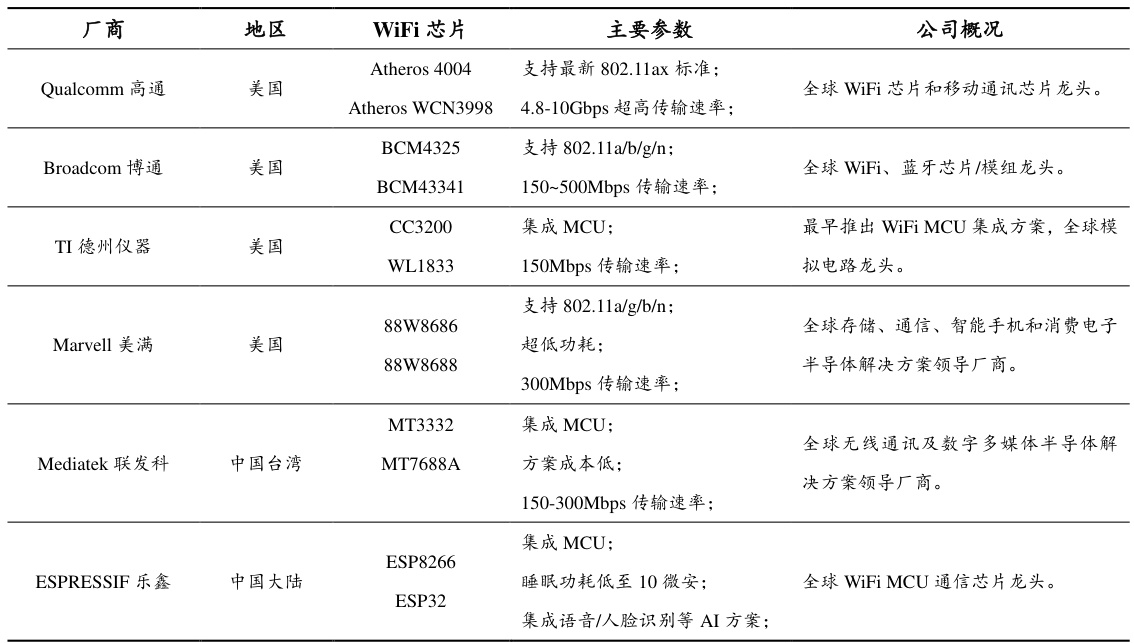

WiFi芯片廠商集體起飛!高通、博通狂攬百億訂單,中國黑馬增速超300%

三星在4nm邏輯芯片上實現40%以上的測試良率

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

5nm芯片為何集體翻車?

5nm芯片為何集體翻車?

評論