Synopsys設計平臺用于高性能、高密度芯片設計

重點:

Synopsys設計平臺獲得TSMC工藝認證,支持高性能7-nm FinFET Plus工藝技術,已成功用于客戶的多個設計項目。

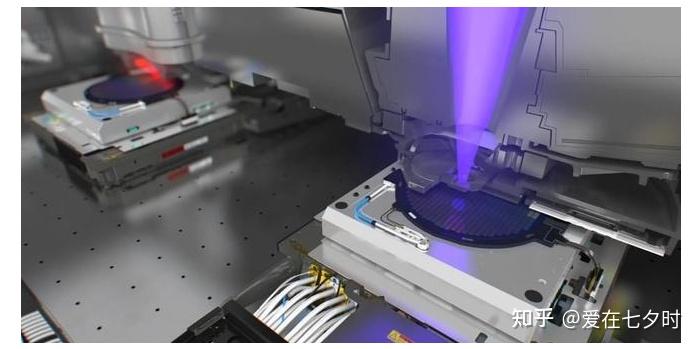

針對7-nm FinFET Plus工藝的極紫外光刻技術,IC Compiler II 進行了專門的優化,進一步節省芯片面積。

采用TSMC的Wafer-on-Wafer?(WoW)技術,平臺內全面支持多裸晶芯片堆疊集成,從而提高生產效率,加快實現大批量生產。

全球第一大芯片自動化設計解決方案提供商及全球第一大芯片接口IP供應商、信息安全和軟件質量的全球領導者Synopsys(NASDAQ: SNPS)近日宣布,Synopsys 設計平臺獲得TSMC最新工藝認證,符合TSMC最新版設計規則手冊(DRM)規定的7-nm FinFET Plus先進工藝技術的相關規范。目前,基于Synopsys 設計平臺完成的數款測試芯片已成功流片,多位客戶也正在基于該平臺進行產品設計研發。Synopsys設計平臺在獲得TSMC的此項認證后,將可以更加廣泛地用于基于此工藝技術的芯片設計,包括高性能、高密度計算和低功耗移動應用。

該認證意味著TSMC極紫外光刻(EUV)工藝取得顯著進步。與非EUV工藝節點相比,前者的芯片面積顯著減少,但仍保持卓越的性能。

以Design Compiler? Graphical綜合工具和IC Compiler?II布局布線工具為核心Synopsys設計平臺性能顯著增強,可充分利用TSMC的7-nm FinFET Plus工藝實現高性能設計。Design Compiler Graphical可以通過自動插入過孔支柱(via-pillar)結構,提高性能以及防止信號電遷移(EM)違規,并且可將信息傳遞給IC Compiler II進行進一步優化。它還會在邏輯綜合時自動應用非默認規則(NDR),并感知繞線層以優化設計、提高性能。這些優化(包括IC Compiler II總線布線),將會在整個布局布線流程中繼續進行,以滿足高速網絡嚴格的延遲匹配要求。

PrimeTime?時序分析工具全面支持先進的波形傳播(AWP)技術和參數化片上偏差(POCV)技術,并已經進行充分優化,可解決更高性能和更低電壓場景中波形失真和非高斯分布偏差造成的影響。此外,PrimeTime感知物理信息的Sign-off擴展了對過孔支柱的支持。

Synopsys強化了設計平臺功能,可以執行物理實現、寄生參數提取、物理驗證和時序分析,以支持TSMC的WoW技術。其中基于IC Compiler II的物理實現流程,全面支持晶圓堆疊設計,包括最初的裸晶布局規劃準備到凸塊(bumps)布局分配,以及執行芯片布線。物理驗證由Synopsys 的IC Validator工具執行DRC/LVS檢查,由StarRC?工具執行寄生參數提取。

TSMC設計基礎架構營銷事業部資深處長Suk Lee表示:“與Synopsys的持續合作以及TSMC 7-nm FinFET Plus工藝技術的早期客戶合作,使我們可以提供差異化的平臺解決方案,幫助我們的共同客戶更快地將開創性新產品推向市場。Synopsys設計平臺成功通過認證,讓我們共同客戶的設計方案首次實現了基于EUV工藝技術的批量生產。”

Synopsys設計事業群營銷和業務開發副總裁 Michael Jackson說:“我們與TSMC就7-nm FinFET Plus量產工藝進行合作,使客戶公司可以放心地開始運用高度差異化的Synopsys 設計平臺,設計日益龐大的SoC和多裸晶堆疊芯片。TSMC 7-nm FinFET Plus工藝認證,讓我們的客戶可以享受到先進的EUV工藝所帶來的功率和性能上的顯著提升,以及面積更大程度的節省,同時加快了其差異化產品的上市時間。”

-

芯片

+關注

關注

463文章

54010瀏覽量

466096 -

IC

+關注

關注

36文章

6411瀏覽量

185643

發布評論請先 登錄

重磅研究:7nm FinFET 性能優化的隱藏密碼 —— 柵極與鰭片間距調控

旋極星源基于22nm工藝完成關鍵IP發布與驗證

技術報告 | Gate 和 Fin Space Variation 對應力調制及 FinFET 性能的影響

半導體“光刻(Photo)”工藝技術的詳解;

AI如何重塑模擬和數字芯片工藝節點遷移

芯片鍵合工藝技術介紹

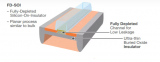

SOI工藝技術介紹

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

TSV技術的關鍵工藝和應用領域

TSMC A14 第二代 GAA 工藝解讀

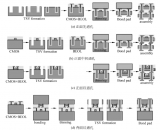

BiCMOS工藝技術解析

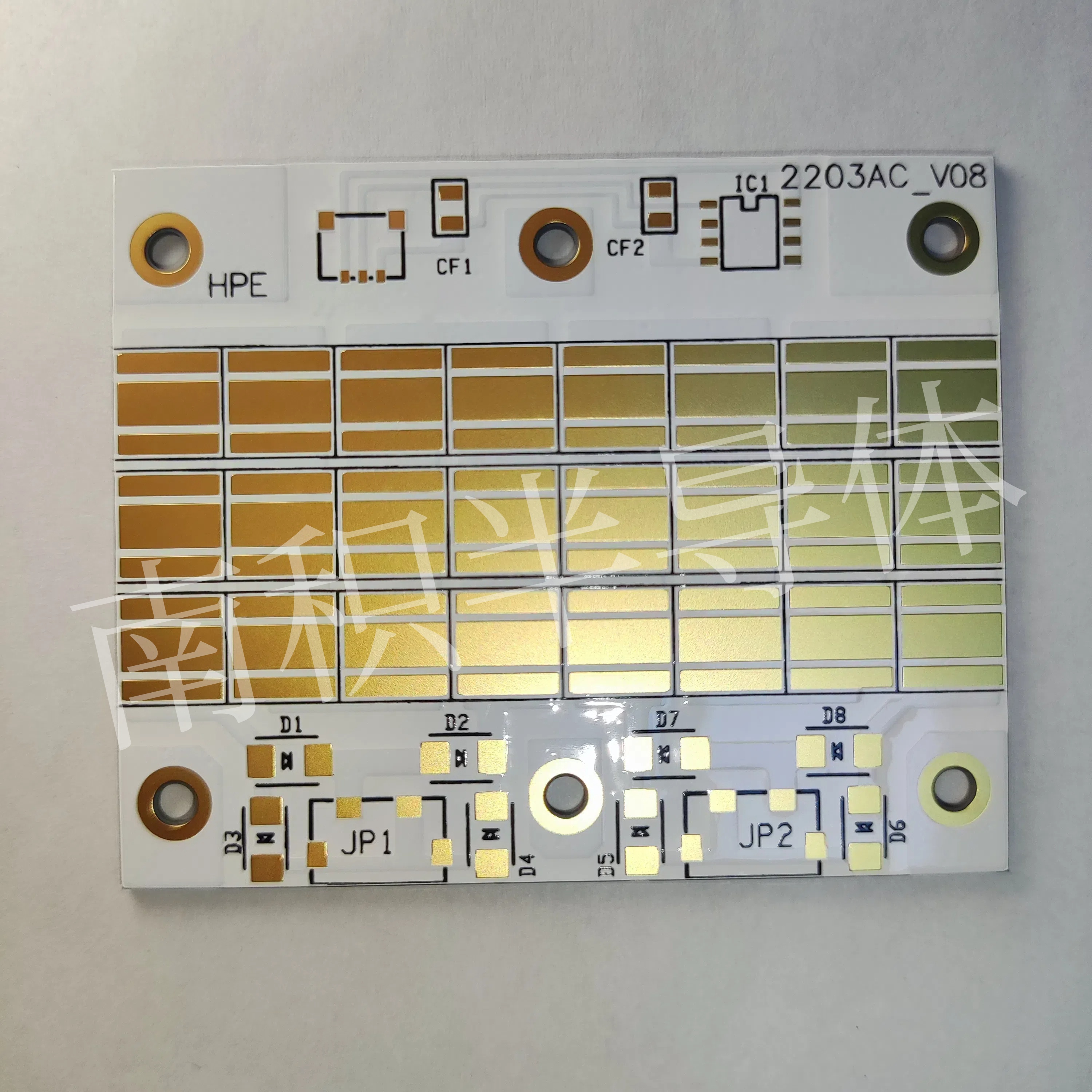

陶瓷基板五大工藝技術深度剖析:DPC、AMB、DBC、HTCC與LTCC的卓越表現

Synopsys設計平臺獲得TSMC工藝認證_7-nm FinFET Plus工藝技術

Synopsys設計平臺獲得TSMC工藝認證_7-nm FinFET Plus工藝技術

評論