隨著集成電路的廣泛應用,集成度越來越高,在BGA技術開始推廣的同時,另外一種從BGA發展來的CSP封裝技術正在逐漸展現它的生力軍本色。作為新一代的芯片封裝技術,CSP封裝可以讓芯片面積與封裝面積之比接近為1,而且電器性能以及可靠性也有大幅提升。正因于此,CSP封裝不斷滲透更多的應用市場,并且還在不斷擴大,而與此同時,與其相關的測試技術也在迅速發展。

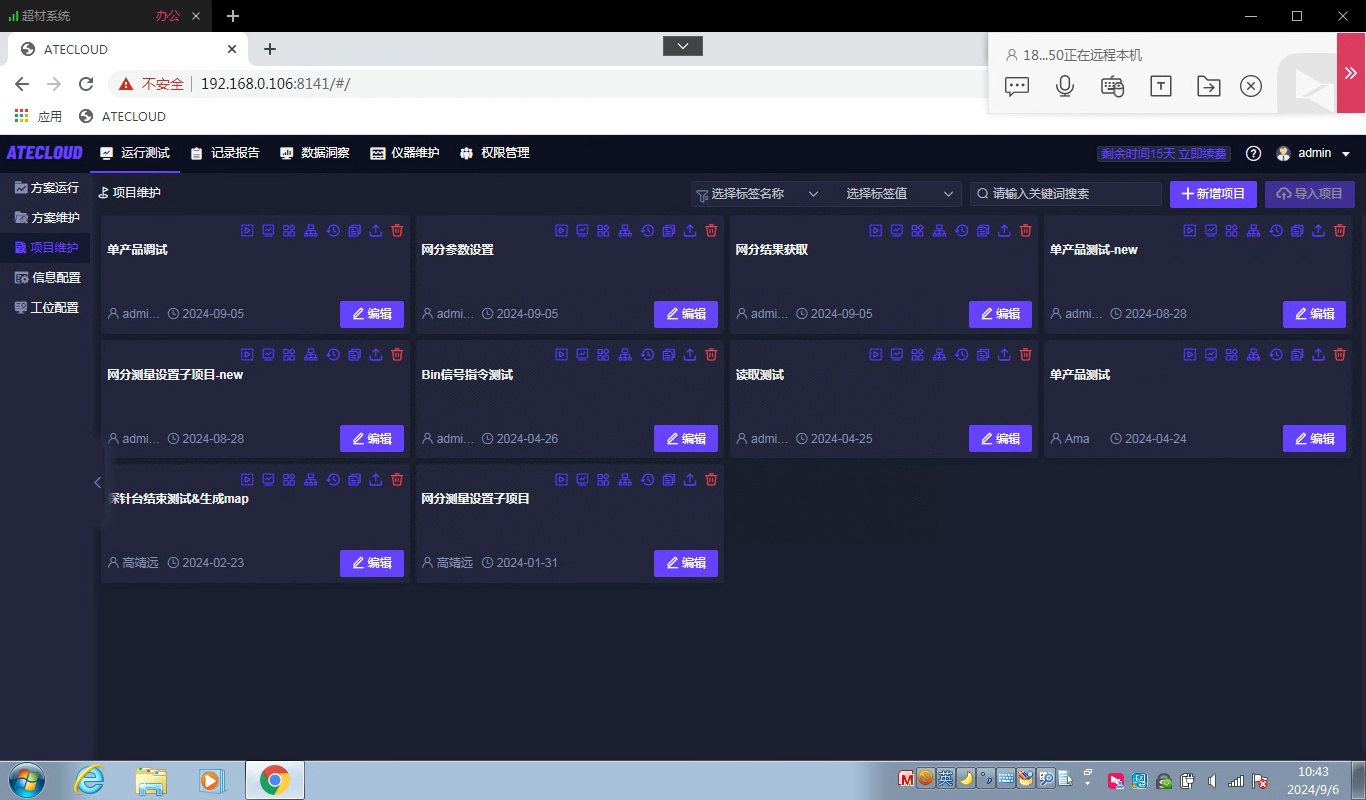

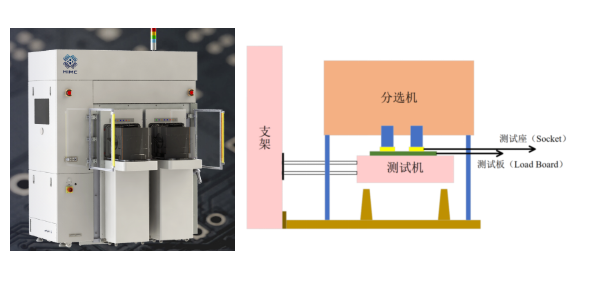

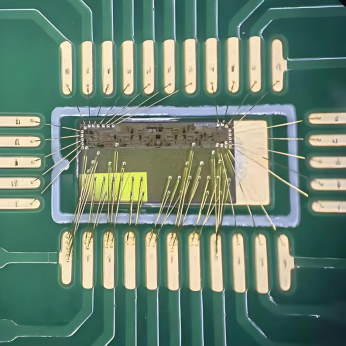

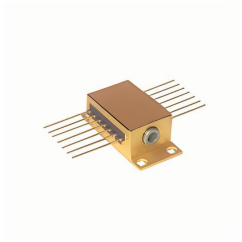

CSP封裝的芯片測試,由于其封裝較小,無法采用普通的機械手測試實現,只有通過類似晶圓測試的方法,在芯片完成植球封裝后,先不做劃片,而直接用探針卡進行測試,測試完成后,再實行劃片、分選和包裝。測試時探針卡固定在探針臺上,探針直接扎在CSP封裝的錫球上以實現電氣連接,然后測試機通過導線施加電壓或波形等激勵進行測試芯片的相關電氣參數。

然而不同于晶圓測試時,探針是扎在管芯的PAD上,鋁質的PAD對探針污染很小,測試過程中不需要經常對探針進行清潔。而CSP封裝測試時,錫球的氧化容易對探針造成嚴重的污染,以至于影響探針和錫球之間的電氣接觸,并同時造成探針與錫球之間的接觸電阻過大,從而導致測試結果失效。

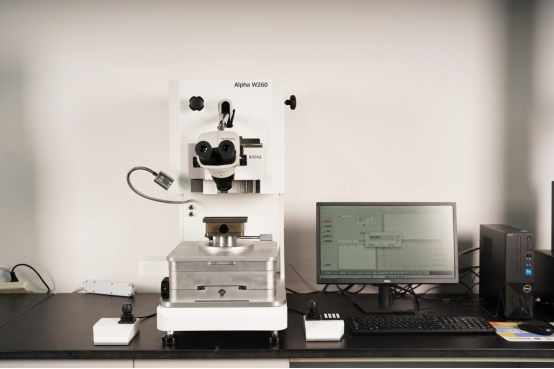

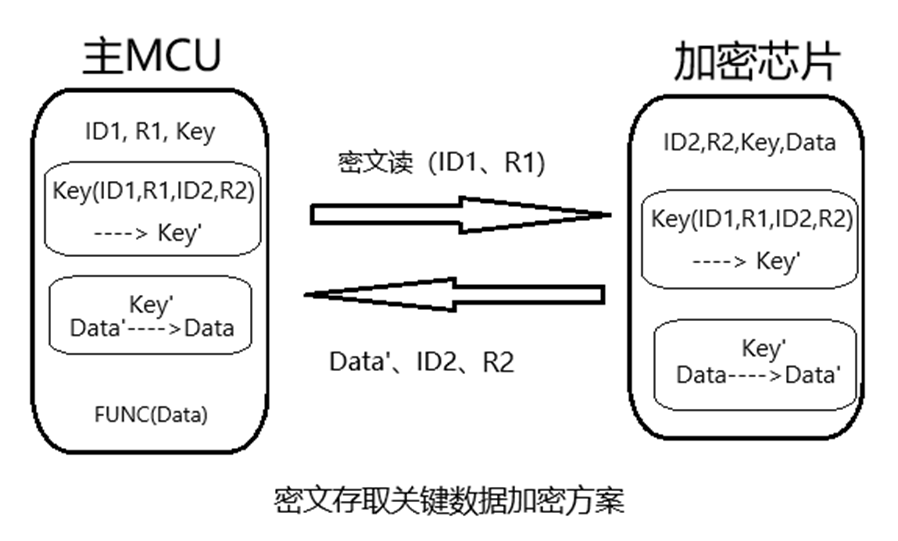

為了能夠減小接觸電阻或者消除接觸電阻的影響,深圳市泰克光電科技有限公司自主研發的飛針測試機(型號PT-198A)采用開爾文連接方式(或稱四線測試方式),既對于每個測試點都有一條激勵線F和一條檢測線S,二者嚴格分開,各自構成獨立回路;同時要求S線必須接到一個有極高輸入阻抗的測試回路上,使流過檢測線S的電流極小,近似為零,這樣在S線上就不會有電壓損失,檢測出來的電壓最為準確。

編輯:fqj

電子發燒友App

電子發燒友App

評論