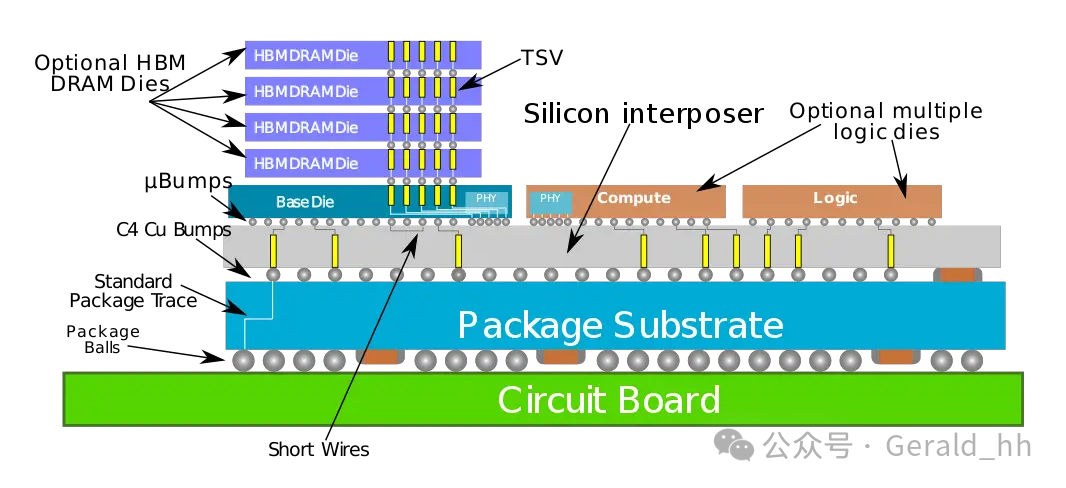

前言: 當臺積電、日月光等企業頭宣布加速擴張CoWoS先進封裝產能,當資本市場以半導體設備股的上漲予以回應,一個明確的信號正在釋放:異質集成(Heterogeneous Integration)的時代已全面加速。然而,在這場以“封裝”為名的產能競賽背后,一個更深刻、更棘手的挑戰正浮出水面:我們如何確認,那些通過數萬根微米級凸點(bump)和硅中介層(interposer)精密“焊接”在一起的不同芯粒(Chiplet),能夠作為一個整體,可靠地工作數年之久? CoWoS將制造復雜度從晶圓前道推向了封裝后道,也從根本上顛覆了芯片“最終測試”的定義與范式。在這里,一場關于“系統級可靠性”的終極考核,正決定著這些昂貴“微系統”的真正價值。

一、 趨勢洞察:從“芯片測試”到“微系統認證”的范式遷移

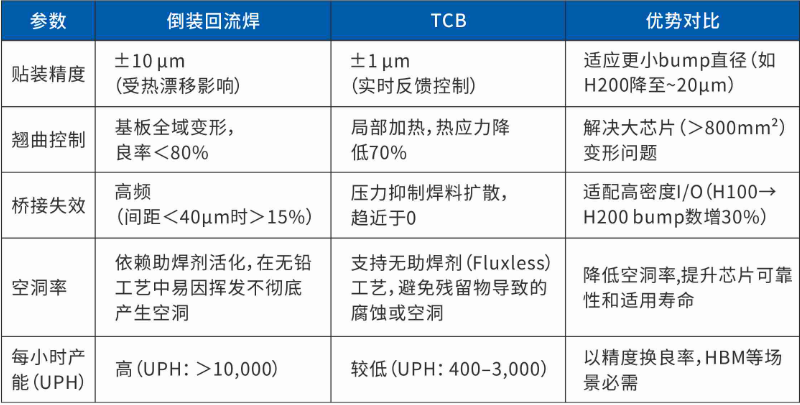

CoWoS產能的超預期需求,直接由GPU、ASIC等高性能計算芯片驅動。這些芯片將計算芯粒、高帶寬內存(HBM)、I/O芯粒等異構單元集成于單一封裝體內,實現了性能的飛躍。這一制造革命,使得傳統的半導體測試金字塔——從晶圓測試(CP)到最終測試(FT)——出現了關鍵的“斷層”。

封裝不再是制造流程的終點,而是創造了一個全新的、更復雜的測試對象。測試的目標,從驗證單個裸片(Die)的電性功能,躍升為認證這個由多個裸片、中介層、基板構成的 “微系統” 的整體行為。這包括:各單元間的電氣互連是否完美無缺?在協同全速運行時,電源噪聲和熱量能否被有效管理?系統級的功能與長期可靠性是否達標?因此,系統級測試(System Level Test, SLT) 不再是一個可選項或補充項,而是成為決定CoWoS芯片能否出廠、能否贏得數據中心客戶信任的強制性最終關卡。這標志著一場從“部件檢查”到“整車路試”的范式遷移。

二、 技術挑戰:異質集成“微系統”的四大考核難題

對CoWoS這類異質集成芯片進行終極考核,面臨前所未有的復雜性,集中體現在四個相互關聯的維度:

三維互連的“隱匿缺陷”篩查

芯粒間通過數以萬計的微凸點連接,任何微小的空洞、虛焊或電遷移,都可能在高負載下引發間歇性故障。這些缺陷在靜態或低速測試中難以暴露。挑戰在于設計高頻、高覆蓋率的互連測試向量,能夠在封裝后有限的可訪問性下,精確診斷出個別失效的互連通道或潛在弱連接,這需要與設計階段協同規劃的可測試性設計(DFT)作為基礎。

系統級的“功耗-熱-性能”協同驗證

計算芯粒與HBM在協同工作時,會產生瞬間的極高功耗峰值,導致復雜的電源噪聲和局部熱點。測試必須模擬最嚴苛的真實工作負載(如AI訓練中的矩陣運算),同時監測整個封裝體的電壓穩定性、電流紋波、熱分布以及由此引發的時鐘抖動和性能波動。單一芯片的測試環境無法復現這種多芯片耦合的“系統級工作態”。

異構單元的“協同啟動”與燒錄

CoWoS芯片在首次上電前,需要為一個包含CPU、GPU、HBM控制器等在內的“多核系統”進行初始化配置。燒錄流程必須能夠并行或有序地為不同架構、不同指令集的芯粒,載入正確的固件、微碼、訓練參數和安全密鑰。這不僅要求燒錄設備支持多協議,更需要一個頂層的“配置管理引擎”,確保所有組件能協調一致地啟動,避免因配置沖突導致系統“死鎖”。

封裝后診斷與可追溯性的物理限制

一旦芯片被密封在封裝體內,傳統的物理探針診斷手段幾乎失效。當SLT測試失敗時,如何快速、低成本地定位故障是位于某個芯粒、互連還是中介層?這要求測試系統能提供極其豐富的數字診斷日志和性能遙測數據,并與前道晶圓測試數據、封裝工藝數據進行關聯分析,構建覆蓋芯片全生命周期的“數字孿生”,以實現精準的根因分析。

解決方案:構建面向“微系統”的智能認證體系

應對上述挑戰,需要構建一套全新的、貫穿設計、制造與測試的智能認證體系,其核心支柱如下:

設計-測試協同(DfT for SI/PI):推動在芯片與封裝設計階段,就將系統級的信號完整性(SI)和電源完整性(PI) 可測試性納入規劃。例如,在互連網絡中植入監測電路,為關鍵電源網絡提供可觀測的測試點,從而在最終測試時能夠“看見”封裝內部的狀態。

基于仿真的復合驗證平臺:建立一個結合 “電-熱-力”多物理場仿真 的測試環境。在SLT階段,不僅運行軟件工作負載,更能根據仿真預測的“最壞情況場景”,動態調整測試向量的電壓、頻率和負載模式,主動激發并捕捉潛在的系統級邊際失效。

高吞吐、多協議的協同配置與燒錄站:開發新一代燒錄解決方案,它應能理解整個CoWoS芯片的拓撲結構,像“交響樂指揮”一樣,同步管理流向不同芯粒的數據流,并確保配置的原子性和一致性。同時,將每一次燒錄操作與芯片的最終序列號、生產批次深度綁定,形成不可篡改的“系統出生證明”。

數據閉環與智能診斷:將SLT過程中采集的海量功耗、性能、溫度數據,與CP測試數據、封裝工藝參數進行大數據關聯分析。利用機器學習算法,建立良率預測模型和早期失效預警系統,將測試從“事后篩選”部分轉變為 “過程質量監控與優化” 的前瞻性工具。

結語:

CoWoS產能的狂飆,標志著半導體性能競賽的主場,正從前道制程工藝逐步轉向后道系統集成能力。而這場競賽的終極裁判,正是那個能夠確保這些復雜“微系統”在現實世界中萬無一失的 “最終測試”新范式。

在您看來,推動CoWoS等異質集成技術大規模落地的最大測試瓶頸是什么?是高昂的系統級測試成本、缺乏統一的互連測試標準,還是故障定位與分析的極端困難? 歡迎在評論區分享您的專業見解與實踐挑戰。當芯片的“大腦”、“內存”與“神經網絡”被封裝進同一個“顱腔”,我們需要的,是一套能夠透視其協同生命力的全新“體檢”標準。在這一前沿領域,與具備從芯片級到系統級全面驗證視野、并擁有深度數據整合能力的伙伴合作,正從可選項變為確保投資回報與產品成功的必選項。

審核編輯 黃宇

-

封裝

+關注

關注

128文章

9302瀏覽量

148931 -

芯片測試

+關注

關注

6文章

181瀏覽量

21174 -

燒錄

+關注

關注

8文章

321瀏覽量

37157 -

CoWoS

+關注

關注

0文章

170瀏覽量

11527

發布評論請先 登錄

CoWoS(Chip-on-Wafer-on-Substrate)先進封裝工藝的材料全景圖及國產替代進展

芯粒設計與異質集成封裝方法介紹

AI芯片發展關鍵痛點就是:CoWoS封裝散熱

CoWoS產能狂飆下的隱憂:當封裝“量變”遭遇檢測“質控”瓶頸

HBM量價齊飛,UFS加速普及:存儲狂飆下的“最后質檢”攻堅戰

高算力低功耗背后的半導體革新

臺積電CoWoS平臺微通道芯片封裝液冷技術的演進路線

【2025九峰山論壇】破局摩爾定律:異質異構集成如何撬動新賽道?

HBM技術在CowoS封裝中的應用

CoWoP能否挑戰CoWoS的霸主地位

普萊信成立TCB實驗室,提供CoWoS、HBM、CPO、oDSP等從打樣到量產的支持

新能源車產線必備!汽車電子組裝測試線憑啥讓產能翻倍?

CoWoS產能狂飆的背后:異質集成芯片的“最終測試”新范式

CoWoS產能狂飆的背后:異質集成芯片的“最終測試”新范式

評論