文章來源:學習那些事

原文作者:小陳婆婆

本文主要講述KGD測試和MCP封裝技術。

在半導體封裝領域,已知合格芯片(KGD)作為多層芯片封裝(MCP)的核心支撐單元,其價值在于通過封裝前的裸片級嚴格篩選,確保堆疊或并聯(lián)芯片的可靠性,避免因單顆芯片失效導致整體封裝報廢,從而顯著提升良率與成本效益。KGD需經(jīng)歷全流程的電路特性驗證與加速壽命測試——包括輸入/輸出電壓/電流匹配性、功能邏輯驗證、動態(tài)功耗分析及時序一致性測試,同時通過高溫老化試驗誘發(fā)潛在缺陷,確保其滿足至少1000小時以上的工作壽命要求。

多層芯片封裝(MCP)的技術路徑依據(jù)應用場景需求分化。

平面并排型通過芯片水平排列優(yōu)化散熱路徑,適用于高功率器件如微處理器(MPU)與靜態(tài)隨機存儲器(SRAM)的集成,但受限于基板面積難以實現(xiàn)高密度集成。

垂直堆疊型則通過硅通孔(TSV)或鍵合線實現(xiàn)三維互聯(lián),在存儲器堆疊中可將安裝密度提升3倍以上,但需采用背面研削工藝將芯片減薄至50微米以下,這對超薄芯片的機械強度與熱管理提出嚴苛挑戰(zhàn),常需引入臨時鍵合與解鍵合技術以避免碎片化風險。

混合型封裝則融合二者優(yōu)勢,在邏輯-存儲混合系統(tǒng)中平衡性能與集成度,例如在移動設備SoC中集成高速緩存與基帶處理器。

KGD的測試實現(xiàn)依賴精密載體系統(tǒng),如具備微米級定位精度的測試插座與溫濕度可控的老化夾具,確保裸片在測試過程中免受機械應力與污染影響。近年來,測試向量優(yōu)化技術通過分析歷史缺陷模式,動態(tài)調(diào)整測試序列,將KGD篩選效率提升40%以上;而量子點傳感技術在老化測試中的應用,實現(xiàn)了納米級缺陷的實時監(jiān)測,進一步提升了可靠性驗證的精度。

此外,針對3D MCP的特殊需求,開發(fā)了基于紅外熱成像的堆疊溫度分布分析系統(tǒng),可精準定位堆疊層間的熱點,避免因熱應力導致的失效。

隨著先進封裝技術的演進,KGD的定義正擴展至異構集成場景,如芯片-晶圓混合封裝(CoWoS)中,需對不同工藝節(jié)點的芯片進行跨工藝兼容性驗證。同時,基于數(shù)字孿生的虛擬測試平臺正逐步應用于KGD篩選,通過仿真預測芯片在實際工況下的性能衰減,大幅縮短測試周期并降低成本。這些進展共同推動著KGD技術在系統(tǒng)級封裝(SiP)與三維集成中的深化應用,支撐著半導體行業(yè)向更高集成度、更低功耗的方向持續(xù)突破。

-

晶圓

+關注

關注

53文章

5420瀏覽量

132404 -

封裝技術

+關注

關注

12文章

601瀏覽量

69318 -

芯片封裝

+關注

關注

13文章

616瀏覽量

32317

原文標題:KGD測試與MCP封裝技術

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

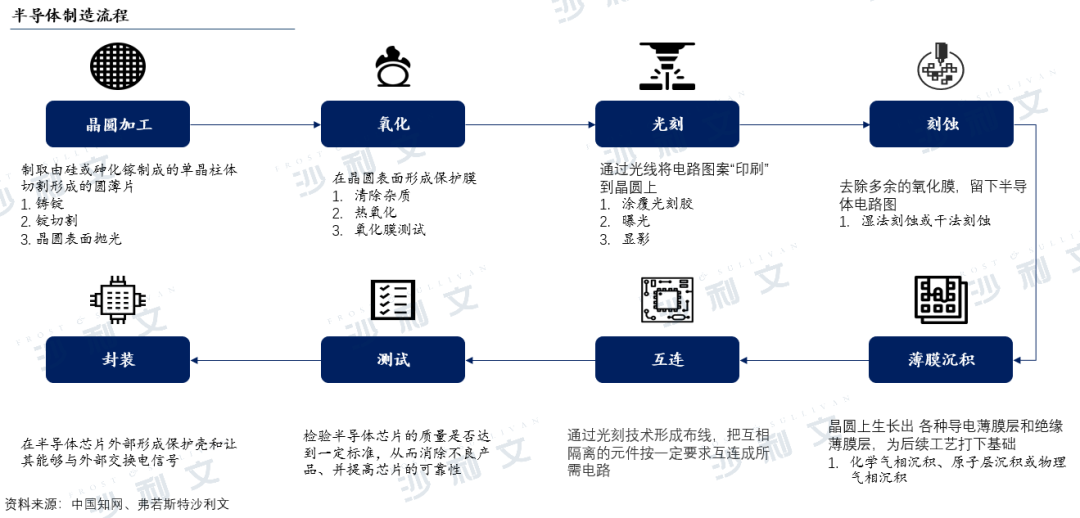

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

半導體制程

半導體制造的難點匯總

半導體制造車間的環(huán)境與生產(chǎn)要求以及設施規(guī)劃

半導體制冷片的工作原理是什么?

半導體制造工藝教程的詳細資料免費下載

半導體制造技術節(jié)點:電子科技飛速發(fā)展的幕后英雄

半導體制造中的多層芯片封裝技術

半導體制造中的多層芯片封裝技術

評論