為實現更高性能目標,AI與HPC芯片設計正加速向芯粒架構演進。但是傳統單片機SOC已經很難在尺寸上繼續擴張,異構集成已成為推動半導體創新的核心動力。然而,它也增加了芯片設計的復雜性,需要更先進的測試方法和經過改進的自動化測試設備(ATE),才能保持信號的完整性、準確性和性能。

隨著半導體復雜性的增加,器件的結構測試變得更具挑戰性,既要求配備高帶寬測試數據接口進行高速測試、確認真正良裸晶粒(KGD),也要在合理的時間范圍內實現高測試覆蓋率和低DPPM數。在將芯粒集成到復雜的異構集成封裝中之前,必須確保單個芯粒達到最高測試覆蓋率,否則將導致將多個芯粒封裝到一起時遇到良率問題。

測試復雜器件時必須用到的向量數量大幅增加,而用于執行測試的通用IO(GPIO)引腳數量其實非常有限。GPIO速度限制了測試數據吞吐量,降低了有效測試當今設計時的整體覆蓋率,盡管傳統的高速I/O協議(PCIe/USB)滿足帶寬要求,但它需要昂貴的硬件設置。

復雜的異構芯片導致測試成本不斷增加

HPC和AI計算芯片的功能變得越來越復雜,驗證步驟的數量也隨之顯著增加。在IO引腳數量有限的場景下,驗證時間成為關鍵瓶頸,不僅會延長開發周期,更使測試成本居高不下。

高帶寬測試訪問端口的可用性有限,尤其是在Multi-Die設計中,這凸顯了對特定IO的需求——既要求其運行速度遠高于傳統GPIO,不能增加額外的硬件,也不能讓支持初始化/校準順序的接口協議變得更復雜,同時更要兼容先進制程的信號完整性要求。

為應對種種挑戰,新思科技優化了高速測試GPIO(HSGPIO)設計,可滿足這些高速測試要求。新思科技的這款多功能產品確保單個IO可以根據其在制造過程中作為“測試端口”的用途進行多路復用;支持調試期間的“高速時鐘觀測”;在量產階段還可以配置為“GPIO”。這種創新設計可以有效支持全面測試需求,在業內獨樹一幟。

高速測試IO有利于實現簡單可靠測試

與其他測試IO相比,新思科技高速測試GPIO IP大幅提高了數據速率,可以高效匹配先進測試設備的需求,支持無協議要求的高速可靠性測試。其主要優勢還表現在可以簡化測試過程,免除了初始化、校準或訓練序列等環節。經過精心設計,其IO在最大速率下仍能保障穩定性和信號完整性。

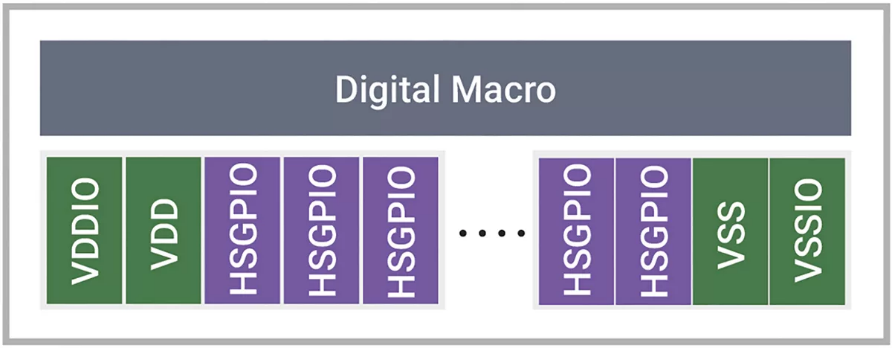

此外,該解決方案節省了GPIO模式和非測試場景下消耗的能源,這種超低功耗特性對于HPC應用至關重要。單端IO設計有助于實現小尺寸、低成本解決方案。得益于其可擴展性,HSGPIO的實現高度靈活,對IO的數量或位置布局沒有限制,可以放置在芯片的左側、右側或周圍。這種靈活性讓IO可以更緊臨被測電路,從而提高驗證效率和便利性。

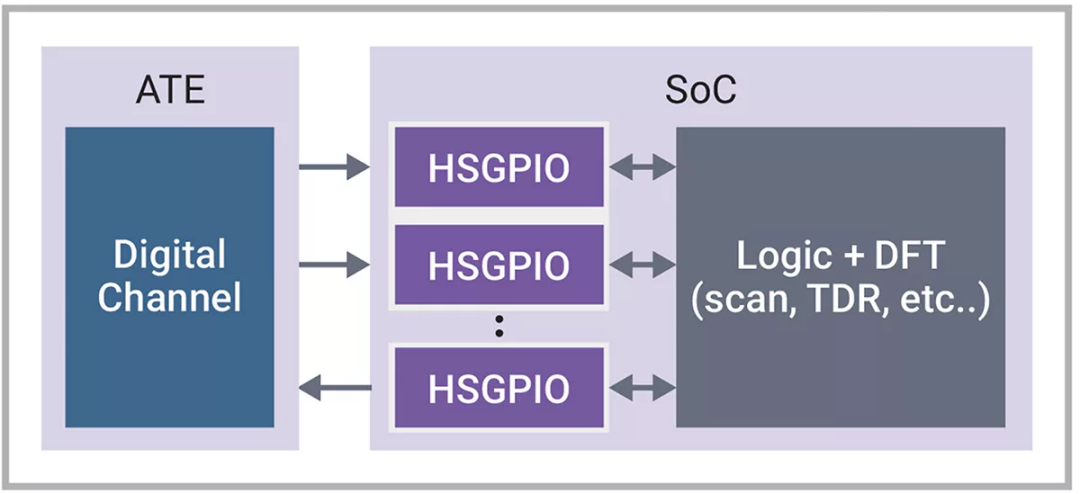

▲圖1:用于測試和實施的新思科技高速測試GPIO(HSGPIO)

通過多種模式增強IO性能并優化功耗

在向芯粒架構演進的過程中,許多常規高速接口在單個芯粒上的可用性顯著降低。UCIe等Die-to-Die接口負責處理芯粒之間的通信,并占用了大多數連接端口,導致可用于外部測試的接口數量變得有限。考慮到封裝引腳非常寶貴,在現場操作中,新思科技高速測試IO支持重復使用與低功耗GPIO相同的高速測試引腳。該解決方案用途廣泛,支持各種測試場景,包括BIST和掃描測試,測試覆蓋率非常高。此外只需要一個單端PAD即可進行信號傳輸和測試。總之,相關設計可以簡化電路板布局,有效減少PAD數量,提高利用率。

該架構不僅保障了高效的測試性能,還增強了SoC驗證階段的可測試性和可維護性:

測試:高速測試IO在制造過程中充當測試端口,在ATE和SoC之間傳輸高達3GBPS的數據,適配裸片(晶圓級)和封裝級測試要求

觀測:IO可復用為參考驗證平臺(RVP)板上的高速時鐘觀測器,以便觀測CLK

節能模式:同一端口在量產環節可配置為GPIO,常規工作頻率高達200MHz,支持低功耗模式

結語

隨著SoC復雜性的增加,解決測試中的挑戰已成為保障功能性和高產量的關鍵。新思科技高速測試IO IP采用創新設計,在有限的封裝引腳下支持高速測試,在量產模式下實現了低功耗GPIO,有助于高速、高效地測試復雜半導體。相關產品不僅大幅縮短測試時間,更在先進ATE測試儀上實現了高吞吐量,無需復雜的接口協議,同時仍能滿足嚴苛的高速要求。新思科技IO團隊將持續為臺積公司的先進節點提供高速測試IO IP支持。

-

晶圓

+關注

關注

53文章

5434瀏覽量

132515 -

封裝

+關注

關注

128文章

9302瀏覽量

148904 -

新思科技

+關注

關注

5文章

970瀏覽量

52966

原文標題:新思科技測試IO方案:晶圓級到封裝級 3Gbps帶寬,加速HPC和AI芯片高質量量產

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

2026新思科技IP技術開放日精彩回顧

AI服務器量產關鍵:高效安規測試方案解決多點測試挑戰

格羅方德收購新思科技處理器 IP 解決方案業務, 擴充實力以加速物理 AI 應用落地

新思科技以AI驅動EDA加速Multi-Die創新

新思科技旗下Ansys仿真和分析解決方案產品組合已通過臺積公司認證

威宏科技加入Arm Total Design生態系統,攜手推動AI與HPC芯片創新

思科Cisco 8223:51.2Tbps P200芯片助力AI數據中心

新思科技邀您相約2025上海汽車測試及質量監控博覽會

普迪飛攜AI測試解決方案與愛德萬測試V93000平臺高效集成,加速提升測試效能

新思科技測試IO方案加速HPC和AI芯片量產

新思科技測試IO方案加速HPC和AI芯片量產

評論