什么是靜電放電(ESD)

Electro-Static Discharge,是指在特定環(huán)境下,由于靜電的積累到達(dá)一定程度后,電荷以迅速釋放的方式恢復(fù)電平衡的現(xiàn)象。這種放電可能由接觸、摩擦或感應(yīng)等多種方式引發(fā)。ESD的特點(diǎn)是電荷積累時(shí)間長(zhǎng)、放電電壓高、涉及電量少、電流小且作用時(shí)間極短。

靜電測(cè)試(ESD)有哪些方式

ESD(靜電放電)測(cè)試方法主要包括以下幾種:

直接放電測(cè)試(Direct Discharge Test)?:使用帶有特定功能的靜電槍直接對(duì)測(cè)試器件進(jìn)行電擊,模擬不同電壓和電流下的ESD事件,以評(píng)估器件在不同場(chǎng)景下的耐受能力?。

間接放電測(cè)試(Indirect Discharge Test)?:通過(guò)預(yù)設(shè)的阻抗或電阻載體與測(cè)試器件相連,進(jìn)行放電測(cè)試。通過(guò)調(diào)整電阻載體的參數(shù),模擬各種放電條件,驗(yàn)證設(shè)備在各種ESD環(huán)境下的抗干擾性能?。

模擬放電測(cè)試(Simulated ESD Event Test)?:利用電容器、電感等元件構(gòu)建的特殊模擬器件,生成類似ESD事件的放電脈沖。通過(guò)測(cè)量器件對(duì)模擬ESD事件的響應(yīng),評(píng)估其在真實(shí)環(huán)境下的表現(xiàn)?。

靜電靈敏度測(cè)試(Electrostatic Sensitivity Test)?:將被測(cè)器件置于特定的ESD環(huán)境中,利用不同的電場(chǎng)和電荷量進(jìn)行測(cè)試。通過(guò)分析器件的響應(yīng)和損壞情況,量化其靜電靈敏度和魯棒性?。

ESD發(fā)生率測(cè)試(ESD Trigger Rate Test)?:通過(guò)長(zhǎng)時(shí)間、連續(xù)的ESD事件模擬,測(cè)試器件在長(zhǎng)期暴露于ESD環(huán)境下的可靠性。監(jiān)測(cè)器件的故障率和性能變化,評(píng)估其長(zhǎng)期耐用性?。

人體模擬器測(cè)試(Human Body Model Test, HBM)?:采用人體模型進(jìn)行ESD測(cè)試,模擬人體觸摸設(shè)備時(shí)產(chǎn)生的靜電放電。通過(guò)模擬人體的電容和電阻特性,評(píng)估設(shè)備在人為ESD事件下的抗干擾能力?。

電子設(shè)備模擬測(cè)試(Equipment Model Test, EMM)?:連接模擬的設(shè)備模型和測(cè)試器件,模擬真實(shí)環(huán)境中的ESD放電事件。通過(guò)調(diào)整設(shè)備模型的參數(shù)和測(cè)試條件,模擬多種ESD事件場(chǎng)景,全面評(píng)估器件性能?。

瞬態(tài)建模分析(Transient Modelling Analysis)?:利用數(shù)學(xué)建模和仿真技術(shù),對(duì)器件的ESD性能進(jìn)行深入分析和評(píng)估。通過(guò)模擬器件在不同ESD事件下的瞬態(tài)響應(yīng),優(yōu)化設(shè)計(jì)以提高其抗ESD能力?。

這些測(cè)試方法各有側(cè)重,綜合使用可以全面評(píng)估電子設(shè)備在不同ESD環(huán)境下的性能和可靠性。

靜電放電(ESD)的危害性

ESD對(duì)多個(gè)行業(yè),尤其是半導(dǎo)體行業(yè)構(gòu)成了嚴(yán)重威脅。據(jù)估計(jì),約有40%的集成電路失效是由ESD引起的。在電子電器產(chǎn)品中,ESD是導(dǎo)致設(shè)備運(yùn)行不穩(wěn)定甚至損壞的主要原因之一。隨著集成電路技術(shù)的發(fā)展,元件集成度提高,特征尺寸縮小,電子元件對(duì)ESD的敏感性也隨之增加。在ESD的高壓和大電流作用下,電子元件可能會(huì)遭受不可逆的損傷,造成產(chǎn)品損壞或性能下降

所以,ESD是電子行業(yè)中一個(gè)不可忽視的問(wèn)題,它對(duì)產(chǎn)品的可靠性和壽命有著直接的影響。隨著技術(shù)的發(fā)展,對(duì)ESD的測(cè)試和防護(hù)要求也越來(lái)越高。通過(guò)嚴(yán)格的ESD測(cè)試和有效的防護(hù)措施,可以顯著提高電子產(chǎn)品的抗靜電能力,減少因ESD造成的損失。因此,對(duì)于電子元件制造商和用戶來(lái)說(shuō),了解ESD的原理、危害和測(cè)試方法,采取適當(dāng)?shù)姆雷o(hù)措施,對(duì)于保障產(chǎn)品質(zhì)量和可靠性至關(guān)重要。

靜電放電(ESD)的意義

確保可靠性?:驗(yàn)證電子設(shè)備在靜電放電時(shí)能否正常工作,避免故障。

發(fā)現(xiàn)問(wèn)題?:提前識(shí)別并解決靜電引起的潛在問(wèn)題,提高產(chǎn)品質(zhì)量。

符合標(biāo)準(zhǔn)?:確保產(chǎn)品滿足國(guó)際ESD標(biāo)準(zhǔn),順利進(jìn)入市場(chǎng)。

降低成本?:減少因靜電損壞導(dǎo)致的維修和維護(hù)費(fèi)用。

保障安全?:提升設(shè)備的穩(wěn)定性和用戶使用安全性。

簡(jiǎn)而言之,靜電放電ESD測(cè)試是為了讓電子設(shè)備更可靠、更安全、更耐用。

審核編輯 黃宇

-

ESD

+關(guān)注

關(guān)注

50文章

2398瀏覽量

179699 -

靜電放電

+關(guān)注

關(guān)注

4文章

310瀏覽量

45912

發(fā)布評(píng)論請(qǐng)先 登錄

關(guān)于“靜電放電(ESD)現(xiàn)象”的詳解

ESD測(cè)試的詳細(xì)解釋

ESD防護(hù)入門(mén):靜電放電的本質(zhì)與測(cè)試體系

靜電放電?ZLG致遠(yuǎn)電子的“防護(hù)盾”了解一下

ESD防靜電閘機(jī)應(yīng)用在芯片封裝車間

半導(dǎo)體器件的靜電放電(ESD)失效機(jī)理與防護(hù)設(shè)計(jì)

為什么 ESD 測(cè)試能過(guò),但實(shí)際應(yīng)用還是被擊壞?

TVS布局對(duì)靜電放電防護(hù)效果的影響分析

IEC 61000-4-2:2025版靜電放電(ESD)標(biāo)準(zhǔn)解讀

半導(dǎo)體芯片的ESD靜電防護(hù):原理、測(cè)試方法與保護(hù)電路設(shè)計(jì)

用靜電電流校準(zhǔn)靶檢驗(yàn)靜電放電發(fā)生器電流波形

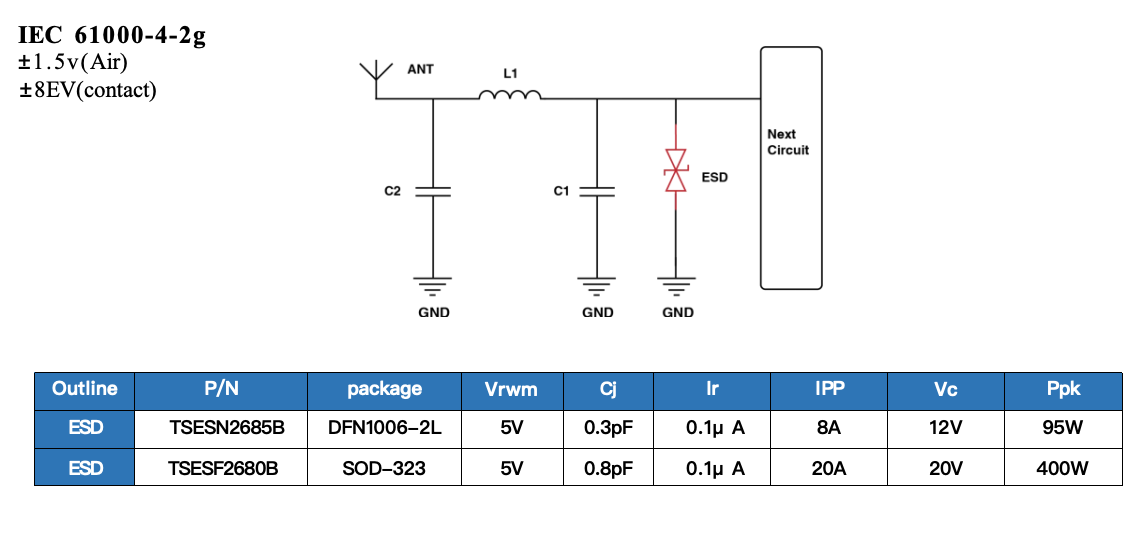

時(shí)源芯微ESD防護(hù)ANT靜電防護(hù)方案

MDDESD靜電放電對(duì)電子元器件的影響:從損壞機(jī)制到防護(hù)策略

淺談靜電放電(ESD)測(cè)試

淺談靜電放電(ESD)測(cè)試

評(píng)論