文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了三維集成封裝技術的進展。

三維集成封裝技術演進

在半導體封裝領域,堆疊技術作為推動高集成度與小型化的核心趨勢,正通過垂直堆疊芯片或封裝實現更緊湊的封裝尺寸及優化的電氣性能——其驅動力不僅源于信號傳輸與功率分布路徑的縮短,更體現在對系統級封裝(SiP)與三維集成(3D IC)的深度探索中。

盡管散熱挑戰與制造成本仍是主要瓶頸,但通過硅/芯片積極減薄、垂直互連技術(如TSV、TGV、TMV及引線鍵合)的創新應用,以及通孔形成(濕/干化學刻蝕、激光鉆孔等)與金屬化(CVD/PVD沉積、電鍍銅等)工藝的優化,堆疊封裝正逐步突破技術限制。

本文分述如下:

多芯片模塊封裝

疊片封裝和疊層封裝

三維集成電路(3D IC)

多芯片模塊封裝

多芯片模塊(MCM)作為早期高集成度封裝的典范,通過將多個半導體芯片與無源元件集成于統一基板,形成單一封裝體,實現了體積縮減與電氣性能的雙重優化,其起源可追溯至半導體封裝對鄰近部件間電氣路徑縮短的需求驅動。基于基板技術,MCM分為MCM-L(層壓基板)、MCM-D(沉積基板)和MCM-C(陶瓷基板)三類。

早期代表如Intel奔騰Pro的陶瓷多芯片組件,通過雙空腔結構集成微處理器與高速緩存芯片,配合多層金線鍵合與外置散熱器設計,在512KB二級緩存場景下驗證了散熱與電氣互連的可行性。相較于傳統分立封裝,MCM的優勢顯著:封裝體積縮小、開發周期縮短、設計錯誤率降低、物料清單簡化,并通過減少PCB層數、批量采購組件及提升裝配效率,實現系統成本優化——以Acme Systems的FOX Board嵌入式系統為例,其ETRAX100LX MCM4+16模塊集成CPU、4MB閃存、16MB SDRAM及以太網收發器等組件,采用256引腳PBGA封裝,尺寸27mm×27mm×2.76mm。

在保持與純CPU封裝相同占地面積的同時,通過高密度互連(HDI)基板技術實現系統級功能整合,僅需外置3.3V電源與晶體振蕩器即可構建全功能Linux計算機,廣泛應用于網關、門禁及工業控制器領域。當前,MCM技術正與先進封裝趨勢深度融合,例如在高性能計算(HPC)芯片中采用硅基板與混合鍵合技術實現亞微米級互連密度,結合嵌入式液冷通道與石墨烯散熱材料提升熱管理能力;在5G通信模塊中,通過有機基板與微凸點技術實現射頻前端與基帶芯片的垂直集成,降低信號延遲并提升功率效率。

這些創新不僅延續了MCM在系統小型化與性能優化上的核心價值,更通過新材料與新工藝的引入,拓展了其在人工智能、自動駕駛等新興領域的應用邊界,持續推動半導體封裝向更高集成度、更低損耗的智能集成方向發展。

疊片封裝和疊層封裝

在半導體封裝技術演進路徑中,疊片封裝與疊層封裝作為實現高集成度與空間優化的核心手段,正通過工藝創新與材料突破持續拓展應用邊界。早期芯片堆疊多芯片模塊(MCM)以金絲鍵合技術為基石,依托晶圓減薄至25μm級、超薄硅芯片處理、低輪廓反向引線鍵合及低拉絲樹脂注入等工藝,在DRAM存儲器模塊中實現多芯片垂直堆疊——典型如2007年量產的20芯片堆疊MCP,整體封裝高度僅1.4mm,顯著提升了存儲密度。

然而,該技術面臨層間間隙控制、導線間距精度及故障成本高等挑戰:層間需預留空間避免導線短路,基板需數百微米水平間距容納導線,且單根導線失效可能導致整個模塊報廢,對工藝精度與良率提出嚴苛要求。為突破傳統金絲鍵合限制,行業探索了混合堆疊方案,如結合倒裝芯片與引線鍵合的復合結構,但消費電子領域對成本與性能的平衡需求使其在批量生產中應用受限。

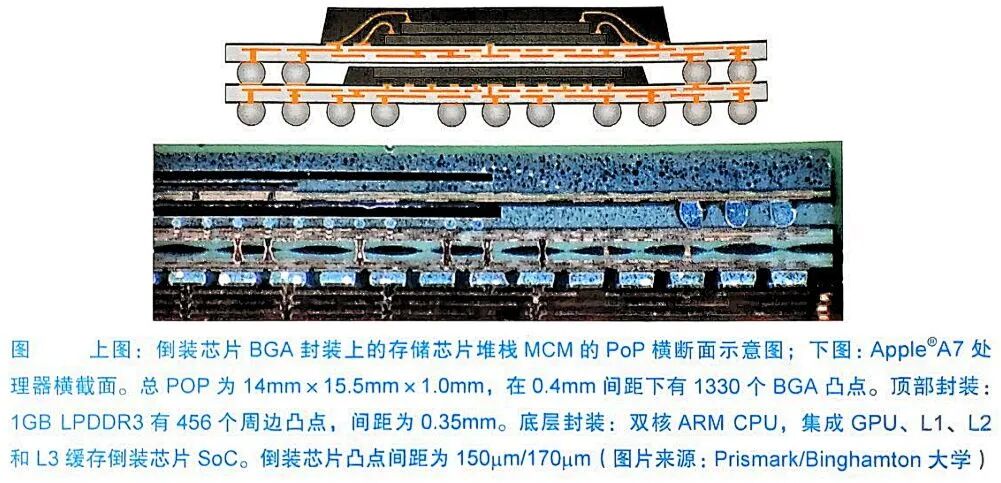

與此同時,疊層封裝技術(PoP)通過將成品封裝垂直堆疊,有效規避了堆疊芯片封裝中的已知良好芯片(KGD)驗證、工藝損傷及混合邏輯-存儲器SiP組裝測試復雜度等問題,早期代表如Tessera開發的uZTM球形PoP,在DRAM模塊中驗證了其空間節省與良率優勢。PoP的典型配置包括純內存堆疊與混合邏輯-內存堆疊(底部為邏輯芯片如CPU,頂部為存儲器),后者因邏輯芯片需更多BGA連接而采用底部布局。在工藝優化方面,底部封裝采用倒裝芯片技術可釋放X/Y方向空間,避免引線鍵合所需的隔離區域,配合下填充材料提升可靠性,同時降低頂部與底部封裝間的間隙高度,支持更小焊球與更緊密互連間距,從而實現對整體封裝高度的精準控制,該方案在移動電子設備中已廣泛應用,如Apple A7微處理器與內存的PoP堆棧。

當前,疊片與疊層封裝技術正與前沿創新深度融合:3D堆疊技術如硅通孔(TSV)與混合鍵合(銅-銅直接鍵合)的應用,顯著提升了互連密度與電氣性能;高密度互連(HDI)基板與有機基板的引入,結合人工智能驅動的布局布線優化算法,進一步提高了PoP的信號完整性與良率;新型材料如碳納米管、石墨烯在堆疊結構中的集成,不僅增強了導電性與熱管理能力,還為高頻、高功率場景下的性能提升提供了新路徑。這些進展持續推動著疊片與疊層封裝向更高集成度、更低損耗、更優熱管理的方向發展,在5G通信、人工智能計算、自動駕駛等新興領域展現出廣闊的應用前景。

三維集成電路(3D IC)

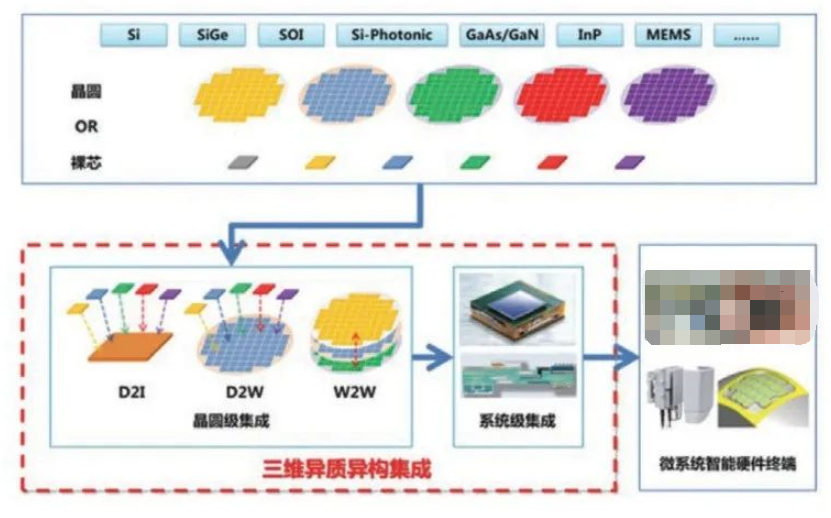

三維集成電路(3D IC)作為芯片級集成的終極形態,通過垂直與水平方向的多層有源電子元件集成,推動半導體技術向更高密度、更低功耗演進。

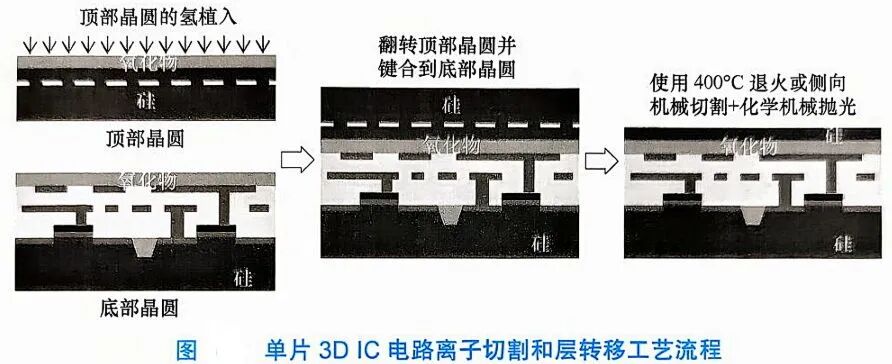

其核心構建路徑分為單片3D IC與TSV 3D IC兩大體系:單片3D IC依托單晶圓分層制造技術,通過離子切割與氫注入實現薄硅層轉移,結合高溫(>800℃)與低溫(<400℃)雙階段工藝,在基板晶圓頂部形成多層無缺陷硅層,完成晶體管布線與層間連接,無需硅通孔即可實現有源層零間隙集成,該技術由DARPA資助的斯坦福大學研究團隊及Monolithic 3D公司推進,已在SOI晶圓生產中驗證其可行性;TSV 3D IC則通過晶圓堆疊(WoW)、芯片-晶圓堆疊(CoW)及芯片-芯片堆疊(CoC)三種工藝實現垂直互連——WoW需在獨立晶圓上預制組件層后鍵合切割,面臨晶圓尺寸匹配與缺陷導致的成品率挑戰;CoW與CoC通過已知良好芯片(KGD)堆疊優化產量,支持混合匹配以適配移動設備等場景的功耗性能需求。當前,TSV技術已突破金屬-金屬直接鍵合瓶頸,配合銅互連與硅通孔微凸點,實現亞微米級互連密度,在高性能計算(HPC)芯片中驗證了信號延遲降低與熱管理提升的實效。

同時,3D IC正與硅光子集成、碳納米管導熱材料等前沿技術融合,例如在光通信模塊中實現光電協同集成,或在人工智能加速器中通過3D堆疊提升內存帶寬與計算效率。這些創新不僅延續了3D IC在系統集成與性能優化上的核心價值,更通過新材料與新工藝的引入,拓展了其在自動駕駛、量子計算等新興領域的應用邊界,持續推動半導體封裝向更高集成度、更低損耗的智能集成方向發展。

-

半導體

+關注

關注

339文章

31004瀏覽量

265488 -

三維

+關注

關注

1文章

529瀏覽量

29963 -

集成封裝

+關注

關注

0文章

14瀏覽量

10169

原文標題:三維集成封裝技術演進

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

三維封裝工藝流程與技術

世界級專家為你解讀:晶圓級三維系統集成技術

三維觸控技術突破“二向箔”的束縛

三維快速建模技術與三維掃描建模的應用

廣西掃描服務三維檢測三維掃描儀

三維設計應用案例

基于LTCC技術的三維集成微波組件

淺談三維集成封裝技術的演進

淺談三維集成封裝技術的演進

評論