其他工藝器件的參與才能保障芯片的高良率。 ? 以光刻膠為例,這是決定芯片 圖案能否被精準 刻下來的“感光神經膜”。并且隨著芯片步入 7nm及以下先進制程芯片 時代,不僅需要EUV光刻機,更需要EUV光刻膠的參與。但在過去 國內長期依賴進

2025-10-28 08:53:35 6234

6234 了全球 EUV 光刻設備市場,成為各國晶圓廠邁向 7nm、5nm 乃至更先進制程繞不開的 “守門人”。然而,近日俄羅斯科學院微結構物理研究所公布的一份國產 EUV 光刻設備長期路線圖,引發了業界的廣泛關注與討論 —— 俄羅斯,正在試圖挑戰 ASML 的霸權。 ?

2025-10-04 03:18:00 9690

9690

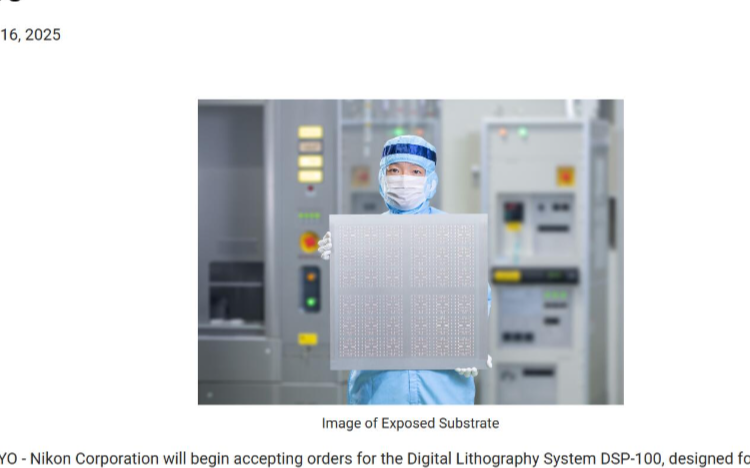

7月16日,全球三大光刻巨頭之一的日本尼康公司宣布,正式推出全球首款專為半導體后道工藝設計的無掩模光刻系統——DSP-100,這款設備為先進封裝量身定制,可以容納600mm大基板,并提供1.0μm

2025-07-24 09:29:39 7815

7815

光罩是半導體制造中光刻工藝所使用的圖形轉移工具或母版,它承載著設計圖形,通過光刻過程將圖形轉移到光刻膠上,再經過刻蝕等步驟轉移到襯底上,是集成電路、微電子制造的關鍵組件,其存放條件直接影響到生產的良

2026-01-05 10:29:00 41

41

實現0.2nm工藝節點。 ? 而隨著芯片工藝節點的推進,芯片供電面臨越來越多問題,所以近年英特爾、臺積電、三星等廠商相繼推出背面供電技術,旨在解決工藝節點不斷推進下,芯片面臨的供電困境。 ? 正面供電面臨物理極限 ? 在半導體技術發展的歷程中

2026-01-03 05:58:00 3946

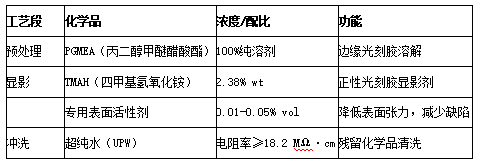

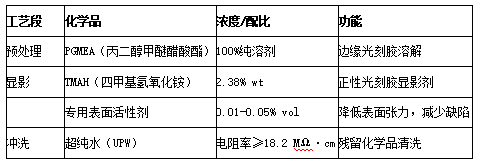

3946 導語 顯影工藝作為光刻制程的核心環節,直接決定晶圓圖形轉移的精度與良率。顯影濕法設備憑借高均勻性噴淋、精準溫度控制及智能缺陷攔截系統,突破16nm以下制程的顯影挑戰,為邏輯芯片、存儲器件及先進封裝

2025-12-24 15:03:51 144

144

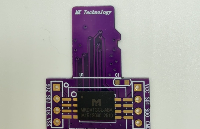

①成本優勢,貨源穩定

②功耗降低30%-50%,工藝制程采用22nm,主頻由64M升級到128M。且54系列是M33的核。

③54系列支持藍牙6.0 ,支持channelsounding功能,52系列不支持。

④54系列支持最新的NCS

2025-12-24 11:09:50

在半導體制造過程中,晶圓去膠工藝之后確實需要進行清洗和干燥步驟。以下是具體介紹:一、清洗的必要性去除殘留物光刻膠碎片:盡管去膠工藝旨在完全去除光刻膠,但在實際操作中,可能會有一些微小的光刻膠顆粒殘留

2025-12-16 11:22:10 110

110

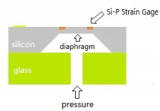

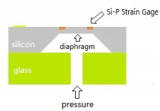

在7納米、3納米等先進芯片制造中,光刻機0.1納米級的曝光精度離不開高精度石英壓力傳感器的支撐,其作為“隱形功臣”,是保障工藝穩定、設備安全與產品良率的核心部件。本文聚焦石英壓力傳感器在光刻機中

2025-12-12 13:02:26 423

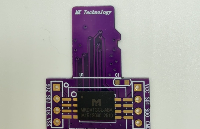

423 2025年11月20日, 國內領先的FPGA芯片供應商廣東高云半導體科技股份有限公司(以下簡稱“高云半導體”)隆重出席2025集成電路發展論壇(成渝)暨第31屆集成電路設計業展覽會(ICCAD 2025)。展會期間,高云半導體全面展示了其布局完善的22nm全系列FPGA產品及解決方案。

2025-11-27 11:10:45 1294

1294

如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習! 在半導體行業,光刻(Photo)工藝技術就像一位技藝高超的藝術家,負責將復雜的電路圖案從掩模轉印到光滑的半導體晶圓上。作為制造過

2025-11-10 09:27:48 1746

1746

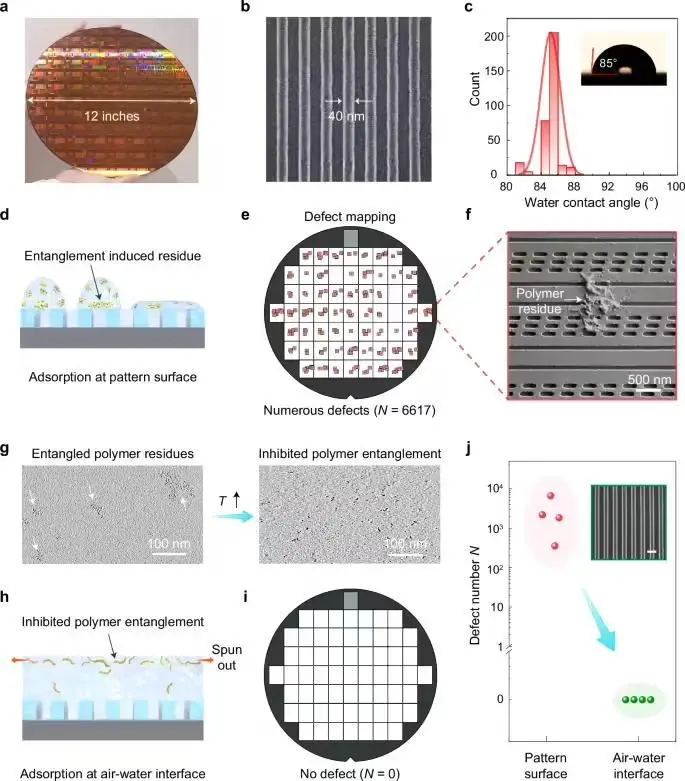

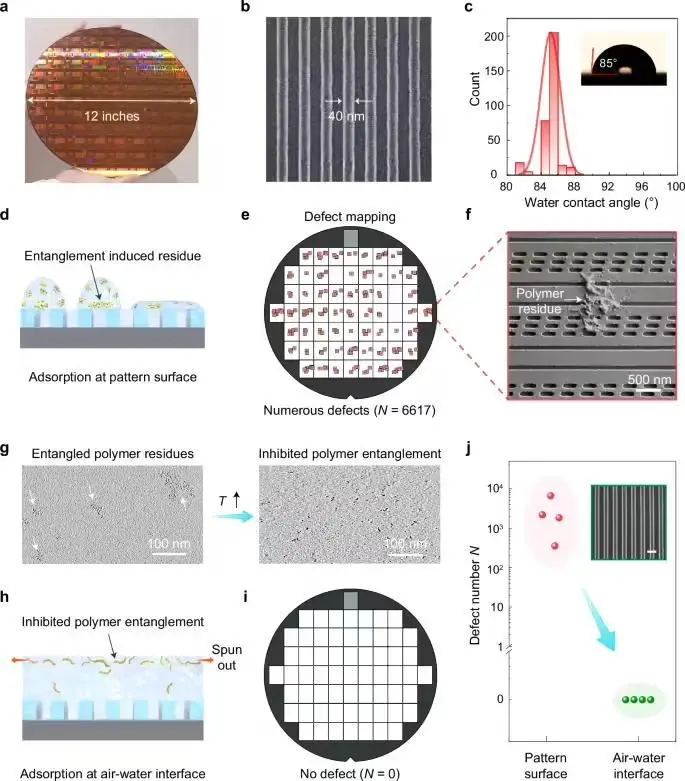

電子發燒友網綜合報道 近日,我國半導體材料領域迎來重大突破。北京大學化學與分子工程學院彭海琳教授團隊及合作者通過冷凍電子斷層掃描技術,首次在原位狀態下解析了光刻膠分子在液相環境中的微觀三維結構、界面

2025-10-27 09:13:04 6178

6178

光刻與刻蝕是納米級圖形轉移的兩大核心工藝,其分辨率、精度與一致性共同決定器件性能與良率上限。

2025-10-24 13:49:06 1666

1666

系列。該系列產品主要面向mini/micro LED光電器件、光芯片、功率器件等化合物半導體領域,可靈活適配硅片、藍寶石、SiC等不同襯底材料,滿足多樣化的膠厚光刻工藝需求。 WS180i系列光刻機優勢顯著。其晶圓覆蓋范圍廣,可處理2~8英寸的晶圓;分

2025-10-10 17:36:33 928

928 一、引言

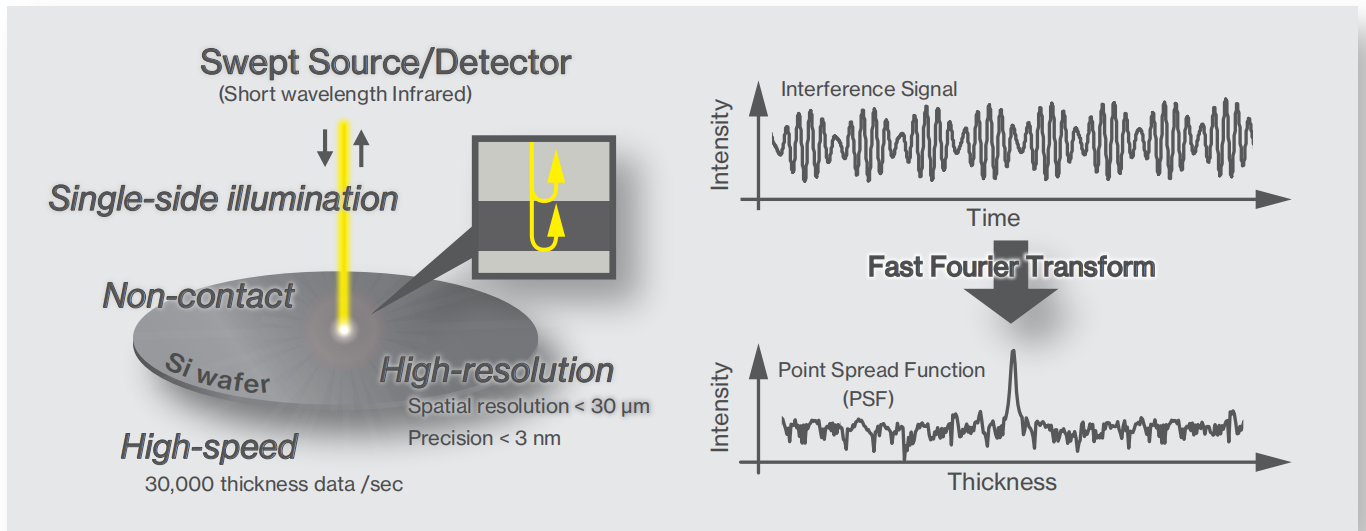

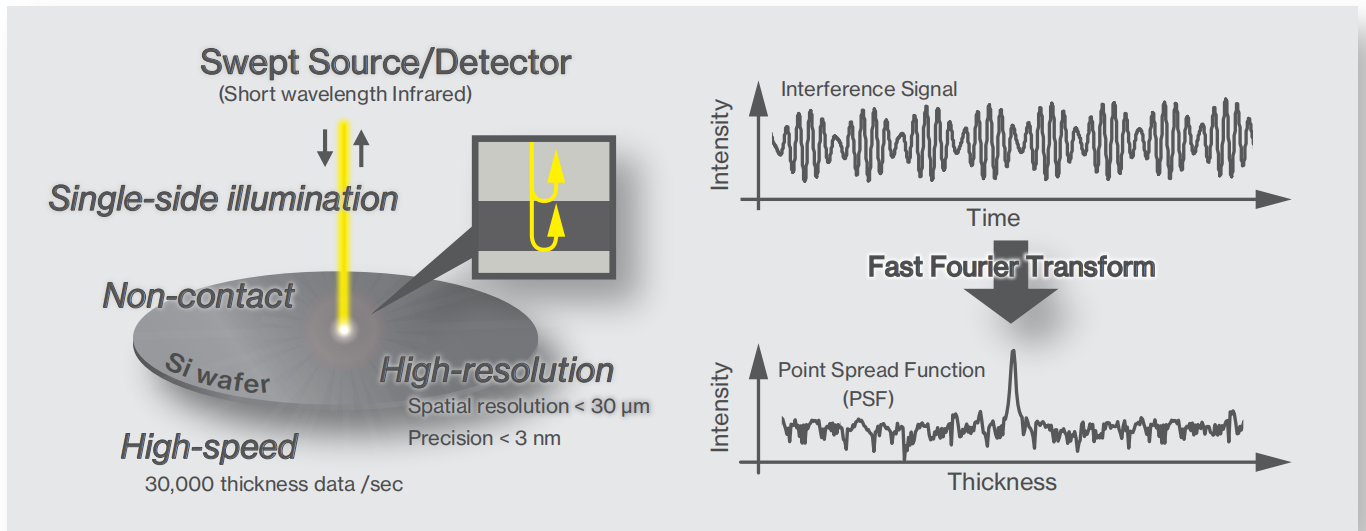

玻璃晶圓在半導體制造、微流控芯片等領域應用廣泛,光刻工藝作為決定器件圖案精度與性能的關鍵環節,對玻璃晶圓的質量要求極為嚴苛 。總厚度偏差(TTV)是衡量玻璃晶圓質量的重要指標,其厚度

2025-10-09 16:29:24 575

575

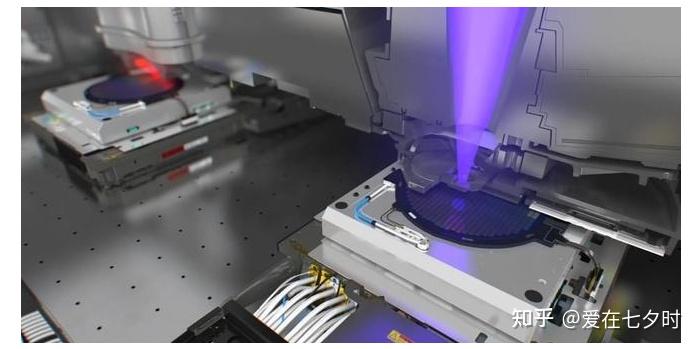

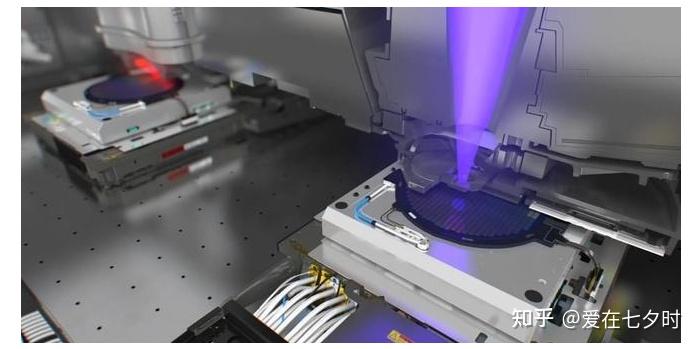

浸沒式光刻(Immersion Lithography)通過在投影透鏡與晶圓之間填充高折射率液體(如超純水,n≈1.44),突破傳統干法光刻的分辨率極限,廣泛應用于 45nm 至 7nm 節點芯片制造。

2025-09-20 11:12:50 841

841 EUV(極紫外)光刻技術憑借 13.5nm 的短波長,成為 7nm 及以下節點集成電路制造的核心工藝,其光刻后形成的三維圖形(如鰭片、柵極、接觸孔等)尺寸通常在 5-50nm 范圍,高度 50-500nm。

2025-09-20 09:16:09 592

592 光刻膠剝離工藝是半導體制造和微納加工中的關鍵步驟,其核心目標是高效、精準地去除光刻膠而不損傷基底材料或已形成的結構。以下是該工藝的主要類型及實施要點:濕法剝離技術有機溶劑溶解法原理:使用丙酮、NMP

2025-09-17 11:01:27 1282

1282

%。至少將GAA納米片提升幾個工藝節點。

2、晶背供電技術

3、EUV光刻機與其他競爭技術

光刻技術是制造3nm、5nm等工藝節點的高端半導體芯片的關鍵技術。是將設計好的芯片版圖圖形轉移到硅晶圓上的一種精細

2025-09-15 14:50:58

BCM56771A0KFSBG性能密度:單芯片 12.8Tbps + 32×400G 端口,降低設備數量與 TCO。技術前瞻:PAM4 調制 + 7nm 工藝,平滑演進至 800G 時代。能效比

2025-09-09 10:41:47

。

FinFET是在22nm之后的工藝中使用,而GAA納米片將會在3nm及下一代工藝中使用。

在叉形片中,先前獨立的兩個晶體管NFET和PFET被連接和集成在兩邊,從而進一步提升了集成度。同時,在它們之間

2025-09-06 10:37:21

在鈣鈦礦太陽能電池串聯結構的制備過程中,需對不同功能膜層進行精確定位劃線。目前,劃刻工藝主要包括掩模板法、化學蝕刻、機械劃片與激光劃片等方式,其中激光劃片因能夠實現更高精度的劃區逐漸成為主流技術

2025-09-05 09:04:36 879

879

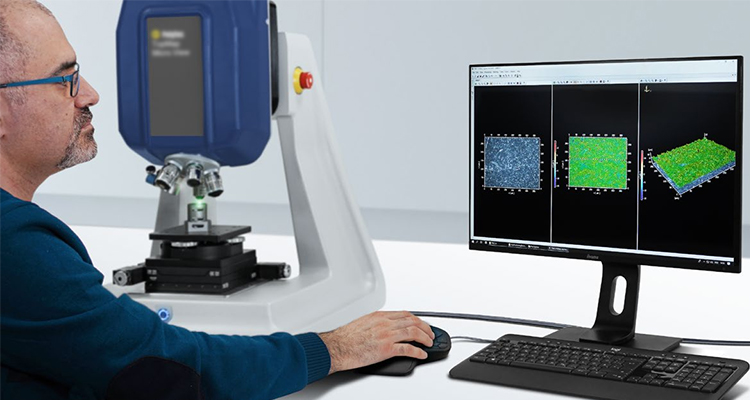

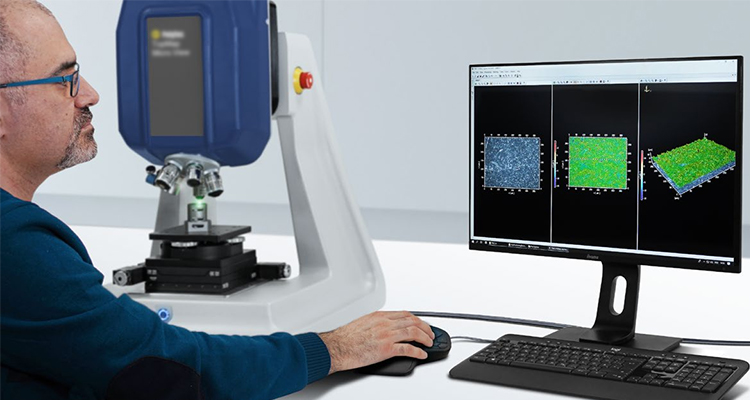

引言 晶圓光刻圖形是半導體制造中通過光刻工藝形成的微米至納米級三維結構(如光刻膠線條、接觸孔、柵極圖形等),其線寬、高度、邊緣粗糙度等參數直接決定后續蝕刻、沉積工藝的精度,進而影響器件性能。傳統

2025-09-03 09:25:20 648

648

InFO-R作為基礎架構,采用"芯片嵌入+RDL成型"的工藝路徑。芯片在晶圓級基板上完成精準定位后,通過光刻工藝直接在芯片表面構建多層銅重布線層(RDL),線寬/線距(L/S)可壓縮至2μm/2μm級別。

2025-09-01 16:10:58 2541

2541

在芯片制造領域的光刻工藝中,光刻膠旋涂是不可或缺的基石環節,而保障光刻膠旋涂的厚度是電路圖案精度的前提。優可測薄膜厚度測量儀AF系列憑借高精度、高速度的特點,為光刻膠厚度監測提供了可靠解決方案。

2025-08-22 17:52:46 1542

1542

電子發燒友網綜合報道 隨著集成電路工藝的不斷突破, 當制程節點持續向7nm及以下邁進,傳統的光刻技術已難以滿足高精度、高密度的制造需求,此時,波長13.5nm的極紫外(EUV)光刻技術逐漸成為支撐

2025-08-17 00:03:00 4218

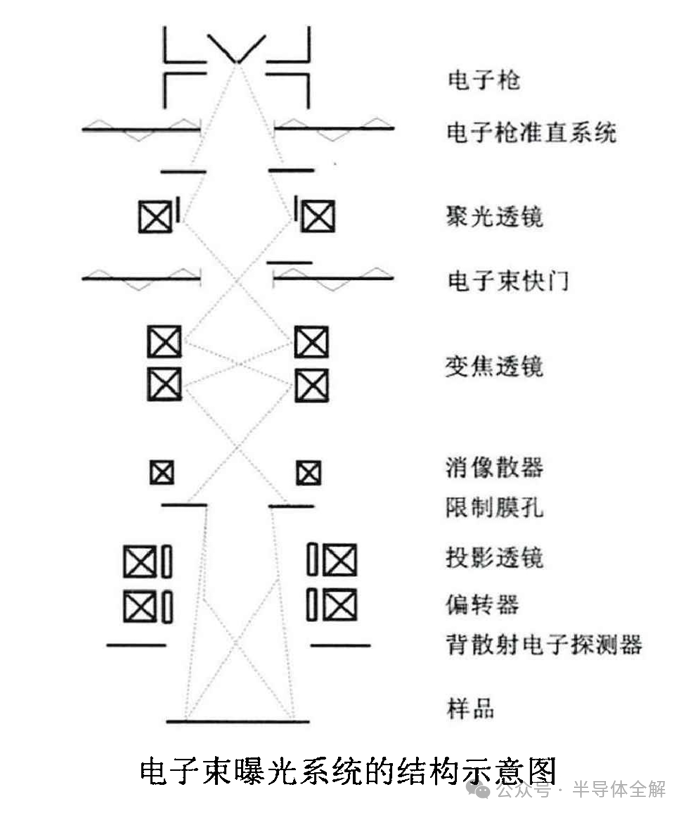

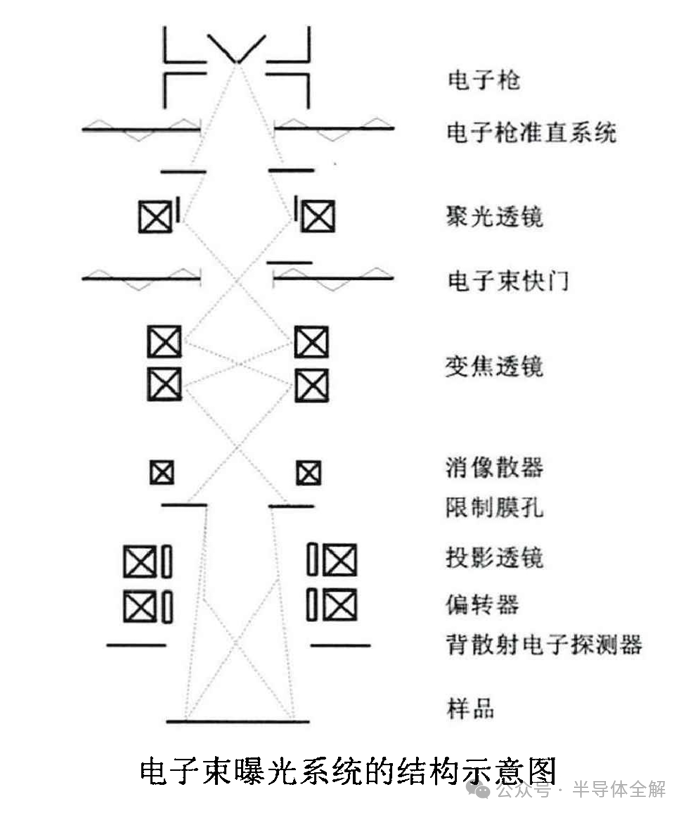

4218 澤攸科技ZEL304G電子束光刻機(EBL)是一款高性能、高精度的光刻設備,專為半導體晶圓的高速、高分辨率光刻需求設計。該系統采用先進的場發射電子槍,結合一體化的高速圖形發生系統,確保光刻質量優異且

2025-08-15 15:14:01

澤攸科技ZML10A是一款創新的桌面級無掩膜光刻設備,專為高效、精準的微納加工需求設計。該設備采用高功率、高均勻度的LED光源,并結合先進的DLP技術,實現了黃光或綠光引導曝光功能,真正做到

2025-08-15 15:11:55

制造工藝的深刻理解,將濕法蝕刻這一關鍵技術與我們自主研發的高精度檢測系統相結合,為行業提供從工藝開發到量產管控的完整解決方案。濕法蝕刻工藝:高精度制造的核心技術M

2025-08-11 14:27:12 1257

1257

光刻工藝是芯片制造的關鍵步驟,其精度直接決定集成電路的性能與良率。隨著制程邁向3nm及以下,光刻膠圖案三維結構和層間對準精度的控制要求達納米級,傳統檢測手段難滿足需求。光子灣3D共聚焦顯微鏡憑借非

2025-08-05 17:46:43 941

941

光阻去除(即去膠工藝)屬于半導體制造中的光刻制程環節,是光刻技術流程中不可或缺的關鍵步驟。以下是其在整個制程中的定位和作用:1.在光刻工藝鏈中的位置典型光刻流程為:涂膠→軟烘→曝光→硬烘→顯影→后烘

2025-07-30 13:33:02 1120

1120

光阻去除工藝(即去膠工藝)是半導體制造中的關鍵步驟,旨在清除曝光后的光刻膠而不損傷底層材料。以下是主流的技術方案及其特點:一、濕法去膠技術1.有機溶劑溶解法原理:利用丙酮、NMP(N-甲基吡咯烷酮

2025-07-30 13:25:43 916

916

這一篇文章介紹幾種芯片加工工藝,在Fab里常見的加工工藝有四種類型,分別是圖形化技術(光刻)?摻雜技術?鍍膜技術和刻蝕技術。

2025-07-16 13:52:55 3321

3321

晶圓蝕刻與擴散是半導體制造中兩個關鍵工藝步驟,分別用于圖形化蝕刻和雜質摻雜。以下是兩者的工藝流程、原理及技術要點的詳細介紹:一、晶圓蝕刻工藝流程1.蝕刻的目的圖形化轉移:將光刻膠圖案轉移到晶圓表面

2025-07-15 15:00:22 1224

1224

厚膠量產到ArF浸沒式膠驗證,從樹脂國產化到EUV原料突破,一場靜默卻浩蕩的技術突圍戰已進入深水區。 ? 例如在248nm波長的KrF光刻膠武漢太紫微的T150A膠以120nm分辨率和93.7%的良率通過中芯國際28nm產線驗證,開創了國內半導體光刻制造的新

2025-07-13 07:22:00 6080

6080 面對近來全球大廠陸續停產LPDDR4/4X以及DDR4內存顆粒所帶來的巨大供應短缺,芯動科技憑借行業首屈一指的內存接口開發能力,服務客戶痛點,率先在全球多個主流28nm和22nm工藝節點上,系統布局

2025-07-08 14:41:10 1158

1158 一、涂膠顯影設備:光刻工藝的“幕后守護者” 在半導體制造的光刻環節里,涂膠顯影設備與光刻機需協同作業,共同實現精密的光刻工藝。曝光工序前,涂膠機會在晶圓表面均勻涂覆光刻膠;曝光完成后,顯影設備則對晶

2025-07-03 09:14:54 770

770

引言 在半導體制造與微納加工領域,光刻圖形線寬變化直接影響器件性能與集成度。精確控制光刻圖形線寬是保障工藝精度的關鍵。本文將介紹改善光刻圖形線寬變化的方法,并探討白光干涉儀在光刻圖形測量中

2025-06-30 15:24:55 736

736

引言 在半導體制造與微納加工領域,光刻圖形的垂直度對器件的電學性能、集成密度以及可靠性有著重要影響。精準控制光刻圖形垂直度是保障先進制程工藝精度的關鍵。本文將系統介紹改善光刻圖形垂直度的方法,并

2025-06-30 09:59:13 489

489

電子發燒友網綜合報道,日前,ASML 技術高級副總裁 Jos Benschop 表示,ASML 已攜手光學組件獨家合作伙伴蔡司,啟動了 5nm 分辨率的 Hyper NA 光刻機開發。這一舉措標志著

2025-06-29 06:39:00 1916

1916 、蝕刻、薄膜沉積等工序,每個環節均需準確溫控。以下以典型場景為例,闡述半導體直冷機Chiller的技術需求與解決方案:1、光刻工藝中的溫度穩定性保障光刻膠涂布與曝

2025-06-26 15:39:09 820

820

引言 在晶圓上芯片制造工藝中,光刻膠剝離是承上啟下的關鍵環節,其效果直接影響芯片性能與良率。同時,光刻圖形的精確測量是保障工藝精度的重要手段。本文將介紹適用于晶圓芯片工藝的光刻膠剝離方法,并探討白光

2025-06-25 10:19:48 815

815

Cortex-M33處理器,處理效率較前代提升3倍;集成1MB閃存與192KB RAM,支持多協議并行運行; 采用22nm工藝,休眠電流低至0.3μA

無線性能?: 支持藍牙6.0完整功能集(含

2025-06-25 10:15:07

引言 在半導體及微納制造領域,光刻膠剝離工藝對金屬結構的保護至關重要。傳統剝離液易造成金屬過度蝕刻,影響器件性能。同時,光刻圖形的精確測量是保障工藝質量的關鍵。本文將介紹金屬低蝕刻率光刻膠剝離液組合

2025-06-24 10:58:22 565

565

在 MEMS(微機電系統)制造領域,光刻工藝是決定版圖中的圖案能否精確 “印刷” 到硅片上的核心環節。光刻 Overlay(套刻精度),則是衡量光刻機將不同層設計圖案對準精度的關鍵指標。光刻 Overlay 指的是芯片制造過程中,前后兩次光刻工藝形成的電路圖案之間的對準精度。

2025-06-18 11:30:49 1556

1556

引言 在顯示面板制造的 ARRAY 制程工藝中,光刻膠剝離是關鍵環節。銅布線在制程中廣泛應用,但傳統光刻膠剝離液易對銅產生腐蝕,影響器件性能。同時,光刻圖形的精準測量對確保 ARRAY 制程工藝精度

2025-06-18 09:56:08 693

693

ASR1606 采用先進的 22nm 制程工藝,將 CPU、Modem 通信單元、射頻模塊、Codec 音頻單元、PSRAM & Flash 存儲單元以及 PMU 電源管理模塊高度集成于單

2025-06-17 18:00:00 1383

1383

預清洗機(Pre-Cleaning System)是半導體制造前道工藝中的關鍵設備,用于在光刻、蝕刻、薄膜沉積等核心制程前,對晶圓、掩膜板、玻璃基板等精密部件進行表面污染物(顆粒、有機物、金屬殘留等

2025-06-17 13:27:16

一、產品概述全自動Mask掩膜板清洗機是半導體光刻工藝中用于清潔光罩(Reticle/Mask)表面的核心設備,主要去除光刻膠殘留、顆粒污染、金屬有機物沉積及蝕刻副產物。其技術覆蓋濕法化學清洗、兆

2025-06-17 11:06:03

測量對工藝優化和產品質量控制至關重要。本文將探討低含量 NMF 光刻膠剝離液及其制備方法,并介紹白光干涉儀在光刻圖形測量中的應用。 低含量 NMF 光刻膠剝離液及制備方法 配方組成 低含量 NMF 光刻膠剝離液主要由低濃度 NMF、助溶劑、堿性物質、緩蝕劑

2025-06-17 10:01:01 677

677

進入過無塵間光刻區的朋友,應該都知道光刻區里用的都是黃燈,這個看似很簡單的問題的背后卻蘊含了很多鮮為人知的道理,那為什么實驗室光刻要用黃光呢? 光刻是微流控芯片制造中的重要工藝之一。簡單來說,它是

2025-06-16 14:36:25 1069

1069 ? ? 引言 ? 在半導體制造領域,光刻膠剝離工藝是關鍵環節,但其可能對器件性能產生負面影響。同時,光刻圖形的精確測量對于保證芯片制造質量至關重要。本文將探討減少光刻膠剝離工藝影響的方法,并介紹白光

2025-06-14 09:42:56 736

736

一、光刻工藝概述 光刻工藝是半導體制造的核心技術,通過光刻膠在特殊波長光線或者電子束下發生化學變化,再經過曝光、顯影、刻蝕等工藝過程,將設計在掩膜上的圖形轉移到襯底上,是現代半導體、微電子、信息產業

2025-06-09 15:51:16 2127

2127 ,傳統組件制備中的激光劃刻工藝(尤其是P3頂電極隔離步驟)會引發鈣鈦礦材料熱降解,但機制不明。本文通過調控激光脈沖重疊度,結合美能鈣鈦礦在線PL測試機評估激光刻劃過程引起的材料缺陷和界面狀態

2025-06-06 09:02:54 925

925

,是指通過紫外光、深紫外光、電子束、離子束、X射線等光照或輻射,溶解度會發生變化的耐蝕刻薄膜材料,是光刻工藝中的關鍵材料。 從芯片生產的工藝流程上來說,光刻膠的應用處于芯片設計、制造、封測當中的制造環節,是芯片制造過程里光刻工

2025-06-04 13:22:51 986

986 與良品率,因此深入探究二者關系并優化測量方法意義重大。 影響機制 工藝應力引發變形 在金屬陽極像素制作時,諸如光刻、蝕刻、金屬沉積等步驟會引入工藝應力。光刻中,光刻膠的涂覆與曝光過程會因光刻膠固化收縮產生應力。蝕刻階段,蝕刻氣體或液體對晶圓表面的作用若不均

2025-05-29 09:43:43 588

588

引言 在半導體制造與微納加工領域,光刻膠剝離液是光刻膠剝離環節的核心材料,其性能優劣直接影響光刻膠去除效果與基片質量。同時,精準測量光刻圖形對把控工藝質量意義重大,白光干涉儀為此提供了有力的技術保障

2025-05-29 09:38:53 1103

1103

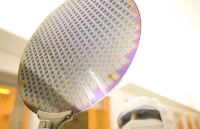

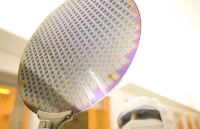

) 市場預計將在未來五年內實現大幅增長。傳感器是芯片制造中使用的先進光刻系統的核心。 制造復雜、高性能且越來越小的半導體芯片時,在很大程度上依賴于高精度、高靈敏度的光刻工藝,這些工藝有助于在硅晶圓和芯片制造中使用的其他基底上印制復雜的圖案。 先進光刻系統采用了極其精確和靈敏的技

2025-05-25 10:50:00 755

755

優勢,為光刻圖形測量提供了可靠手段。 ? Micro OLED 陽極像素定義層制備方法 ? 傳統光刻工藝 ? 傳統 Micro OLED 陽極像素定義層制備常采用光刻剝離工藝。首先在基板上沉積金屬層作為陽極材料,接著旋涂光刻膠,通過掩模版曝光使光刻膠發生光化學反應,隨后

2025-05-23 09:39:17 628

628

定向自組裝光刻技術通過材料科學與自組裝工藝的深度融合,正在重構納米制造的工藝組成。主要內容包含圖形結構外延法、化學外延法及圖形轉移技術。

2025-05-21 15:24:25 1945

1945

Ultra,小米首款SUV小米yu7 等。 雷軍還透露,小米玄戒O1,采用第二代3nm工藝制程,力爭躋身第一梯隊旗艦體驗。此次小米發布會的最大亮點之一肯定是小米自研手機SoC芯片「玄戒O1」,這標志著小米在芯片領域的自主研發能力邁入新階段。從澎湃S1到玄戒O1,小米11年造芯

2025-05-19 16:52:59 1155

1155 電子發燒友網報道(文/黃山明)在半導體行業邁向3nm及以下節點的今天,光刻工藝的精度與效率已成為決定芯片性能與成本的核心要素。光刻掩模作為光刻技術的“底片”,其設計質量直接決定了晶體管結構的精準度

2025-05-16 09:36:47 5598

5598

電子直寫光刻機駐極體圓筒聚焦電極

隨著科技進步,對電子顯微鏡的精度要求越來越高。電子直寫光刻機的精度與電子波長和電子束聚焦后的焦點直徑有關,電子波長可通過增加加速電極電壓來減小波長,而電子束聚焦后

2025-05-07 06:03:45

,或者MDP軟件。

現有可免費試用的光刻圖形轉化軟件,可實現最高1nm精度的大型圖形轉換,同時只需要的少量的電腦內存就可以運行。如需要請聯系我,謝謝!

2025-05-02 12:42:10

光刻膠類型及特性光刻膠(Photoresist),又稱光致抗蝕劑,是芯片制造中光刻工藝的核心材料。其性能直接影響芯片制造的精度、效率和可靠性。本文介紹了光刻膠類型和光刻膠特性。

2025-04-29 13:59:33 7820

7820

在半導體制造中,清洗工藝貫穿于光刻、刻蝕、沉積等關鍵流程,并在單晶硅片制備階段發揮著重要作用。隨著技術的發展,芯片制程已推進至28nm、14nm乃至更先進節點。

2025-04-24 14:27:32 715

715 強固型嵌入式計算平臺廠商Neousys宸曜科技發布了新的無風扇嵌入式計算平臺Nuvo-11000系列。Nuvo-11000系列搭載了新的英特爾酷睿Ultra200處理器,不僅采用了先進的3nm光刻工藝

2025-04-23 16:52:17 695

695

第9章 集成電路制造工藝概況 第10章 氧化 第11章 淀積 第12章 金屬化 第13章 光刻:氣相成底膜到軟烘 第14章 光刻:對準和曝光 第15章 光刻:光刻膠顯影和先進的光刻技術 第16章

2025-04-15 13:52:11

晶圓高溫清洗蝕刻工藝是半導體制造過程中的關鍵環節,對于確保芯片的性能和質量至關重要。為此,在目前市場需求的增長情況下,我們來給大家介紹一下詳情。 一、工藝原理 清洗原理 高溫清洗利用物理和化學的作用

2025-04-15 10:01:33 1096

1096 經常會有同行問:國產100K邏輯規模的器件是否已經成熟和穩定?當然,可以很負責任地說,目前幾家國產FPGA原廠都有28nm工藝節點(或同級別的22nm)器件,并且也已經在市場中大規模的使用,紫光同創

2025-04-14 09:53:47 1224

1224

進制程領域,曝光波長逐漸縮短至13.5nm,光刻技術逐步完善成熟。2024年光刻機市場的規模為230億美元。2025年光刻機市場的規模預計為252億美元。 【光刻機的發展機會主要體現在以下四方面】 一、技術突破與市場競爭 中科院成功研發了突破性的固態深

2025-04-07 09:24:27 1236

1236 。

光刻工藝、刻蝕工藝

在芯片制造過程中,光刻工藝和刻蝕工藝用于在某個半導體材料或介質材料層上,按照光掩膜版上的圖形,“刻制”出材料層的圖形。

首先準備好硅片和光掩膜版,然后再硅片表面上通過薄膜工藝生成一

2025-04-02 15:59:44

,三合一工藝平臺,CMOS圖像傳感器工藝平臺,微電機系統工藝平臺。 光掩模版:基板,不透光材料 光刻膠:感光樹脂,增感劑,溶劑。 正性和負性。 光刻工藝: 涂光刻膠。掩模版向下曝光。定影和后烘固化蝕刻工藝

2025-03-27 16:38:20

光刻工藝貫穿整個芯片制造流程的多次重復轉印環節,對于集成電路的微縮化和高性能起著決定性作用。隨著半導體制造工藝演進,對光刻分辨率、套準精度和可靠性的要求持續攀升,光刻技術也將不斷演化,支持更為先進的制程與更復雜的器件設計。

2025-03-27 09:21:33 3273

3273

在科技日新月異的今天,芯片作為數字時代的“心臟”,其制造過程復雜而精密,涉及眾多關鍵環節。提到芯片制造,人們往往首先想到的是光刻機這一高端設備,但實際上,芯片的成功制造遠不止依賴光刻機這一單一工具。本文將深入探討芯片制造的五大關鍵工藝,揭示這些工藝如何協同工作,共同鑄就了現代芯片的輝煌。

2025-03-24 11:27:42 3167

3167

電子發燒友網綜合報道?據多方消息來源推測,三星電子可能取消原計劃于?2027?年量產的?1.4nm(FS1.4)晶圓代工工藝。三星在?“Samsung?Foundry?Forum?2022”?上首

2025-03-23 11:17:40 1827

1827 電子發燒友網綜合報道 據多方消息來源推測,三星電子可能取消原計劃于 2027 年量產的 1.4nm(FS1.4)晶圓代工工藝。三星在 “Samsung Foundry Forum 2022” 上首

2025-03-22 00:02:00 2462

2462 體。在光刻工藝過程中,用作抗腐蝕涂層材料。半導體材料在表面加工時,若采用適當的有選擇性的光刻膠,可在表面上得到所需的圖像。光刻膠按其形成的圖像分類有正性、負性兩大類

2025-03-18 13:59:53 3004

3004

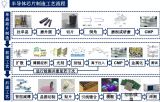

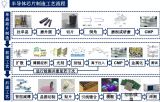

光刻是廣泛應用的芯片加工技術之一,下圖是常見的半導體加工工藝流程。

2025-03-04 17:07:04 2118

2118

工藝制程22nm低功耗工藝

主頻最高1.8GHz(動態頻率調節)

GPUARM Mali-G52 2EE GPU

NPU0.8TOPS算力(支持INT8/INT16)2. 核心性能亮點? 計算性能

2025-02-26 12:17:22

掩膜版作為微納加工技術中光刻工藝所使用的圖形母版,在IC、平版顯示器、印刷電路版、微機電系統等領域具有廣泛的應用。隨著信息技術和智能制造的快速發展,特別是智能手機、平板電腦、車載電子等市場的快速增長

2025-02-19 16:33:12 1047

1047 ? EUV光刻有多強?目前來看,沒有EUV光刻,業界就無法制造7nm制程以下的芯片。EUV光刻機也是歷史上最復雜、最昂貴的機器之一。 EUV光刻有哪些瓶頸? EUV光刻技術,存在很多難點。 1.1

2025-02-18 09:31:24 2256

2256

在芯片制造的復雜流程中,光刻工藝是決定晶體管圖案能否精確“印刷”到硅片上的核心環節。而光刻Overlay(套刻精度),則是衡量光刻機將不同層電路圖案對準精度的關鍵指標。簡單來說,它就像建造摩天大樓

2025-02-17 14:09:25 4462

4462

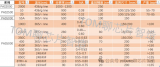

TechInsights與SemiWiki近日聯合發布了對英特爾Intel 18A(1.8nm級別)和臺積電N2(2nm級別)工藝的深度分析。結果顯示,兩者在關鍵性能指標上各有優勢。 據

2025-02-17 13:52:02 1086

1086 的工藝制程,猶如三把鑰匙,開啟著不同應用場景的大門。本文將深入解析這三種鋰電池封裝形狀背后的技術路線與工藝奧秘。 一、方形鋰電池:堅固方正背后的工藝匠心 (一)結構與設計優勢 方形鋰電池以其規整的外形示人,這種

2025-02-17 10:10:38 2226

2226

半導體設備安裝防震裝置主要有以下幾方面原因:一、高精度加工要求1,光刻工藝(1)光刻是半導體制造的關鍵步驟,其精度要求極高。例如,在芯片制造中,光刻設備需要將電路圖案精確地投射到硅片上。現代光刻技術

2025-02-05 16:48:03 874

874

光刻是芯片制造過程中至關重要的一步,它定義了芯片上的各種微細圖案,并且要求極高的精度。以下是光刻過程的詳細介紹,包括原理和具體步驟。?? 光刻原理?????? 光刻的核心工具包括光掩膜、光刻

2025-01-28 16:36:00 3577

3577

一站式 NVM 存儲 IP 供應商創飛芯(CFX)今日宣布,其反熔絲一次性可編程(OTP)技術繼 2021年在國內第一家代工廠實現量產后,2024 年在國內多家代工廠關于 90nm BCD 工藝上也

2025-01-20 17:27:47 1647

1647 數值孔徑,是影響分辨率(R),焦深(DOF)的重要參數,公式為: ? R=k1?λ/NA ? DOF=k2?λ/NA2 ? 其中,λ為波長,k1,k2均為工藝因子。從公式可以看出:提高NA可以提升光刻分辨率,增大NA會縮小景深。 ? ? ? 如何增大NA? ? 增大NA值的主要目標是提高分辨率。 ? NA的公式為: ?

2025-01-20 09:44:18 2475

2475

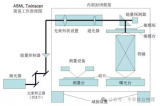

本文主要介紹光刻機的分類與原理。 ? 光刻機分類 光刻機的分類方式很多。按半導體制造工序分類,光刻設備有前道和后道之分。前道光刻機包括芯片光刻機和面板光刻機。面板光刻機的工作原理和芯片光刻機相似

2025-01-16 09:29:45 6353

6353

。這通常涉及到外延生長、光刻、離子注入、擴散等工藝步驟。 外延生長 :在襯底上生長出所需的半導體材料層。 光刻 :利用光刻技術在半導體材料上形成所需的圖案。 離子注入 :通過離子注入改變半導體材料的電學性質。 擴散 :通過高溫擴

2025-01-14 16:55:08 1780

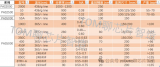

1780 。這一精密而復雜的流程主要包括以下幾個工藝過程:晶圓制造工藝、熱工藝、光刻工藝、刻蝕工藝、離子注入工藝、薄膜淀積工藝、化學機械拋光工藝。 ? ? ? 晶圓制造工藝 晶圓制造工藝包括單晶生長、晶片切割和晶圓清洗。 ? 半導

2025-01-08 11:48:34 4037

4037

光刻膠在這些物理或化學過程中具有更好的工藝穩定性和效果。 增強光刻膠與基片的粘附 烘膠有助于除去顯影后殘留于膠膜中的溶劑或水分,從而使膠膜與基片緊密粘附,防止膠層脫落。這一過程在微流控芯片的光刻工藝中是重要的一環,保障了

2025-01-07 15:18:06 823

823 某大型半導體制造企業專注于高端芯片的研發與生產,其電子束光刻設備在芯片制造的光刻工藝中起著關鍵作用。然而,企業所在園區周邊存在眾多工廠,日常生產活動產生復雜的振動源,包括重型機械運轉、車輛行駛以及建筑物內部的機電設備運行等,這些振動嚴重影響了電子束光刻設備的精度與穩定性。

2025-01-07 15:13:21 1320

1320

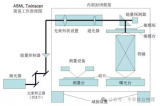

? 本文介紹了組成光刻機的各個分系統。 光刻技術作為制造集成電路芯片的重要步驟,其重要性不言而喻。光刻機是實現這一工藝的核心設備,它的工作原理類似于傳統攝影中的曝光過程,但精度要求極高,能夠達到

2025-01-07 10:02:30 4525

4525

電子發燒友App

電子發燒友App

評論