文章來(lái)源:學(xué)習(xí)那些事

原文作者:小陳婆婆

在先進(jìn)封裝技術(shù)演進(jìn)中,臺(tái)積電的InFO(Integrated Fan-Out)平臺(tái)通過(guò)扇出型重布線(xiàn)技術(shù)重新定義了芯片級(jí)集成的可能性。

InFO-R和 InFO-L

InFO-R作為基礎(chǔ)架構(gòu),采用"芯片嵌入+RDL成型"的工藝路徑。芯片在晶圓級(jí)基板上完成精準(zhǔn)定位后,通過(guò)光刻工藝直接在芯片表面構(gòu)建多層銅重布線(xiàn)層(RDL),線(xiàn)寬/線(xiàn)距(L/S)可壓縮至2μm/2μm級(jí)別。這種設(shè)計(jì)使單塊封裝即可集成多顆異質(zhì)芯片(如邏輯、存儲(chǔ)、射頻模塊),并通過(guò)扇出型走線(xiàn)實(shí)現(xiàn)芯片間橫向互連。蘋(píng)果M系列芯片的封裝即采用該技術(shù),在保持12英寸晶圓級(jí)尺寸的同時(shí),將APU與LPDDR5內(nèi)存的互連帶寬提升到200GB/s,較傳統(tǒng)FCBGA封裝提升3倍。值得注意的是,臺(tái)積電近期公布的InFO-R Gen3工藝已實(shí)現(xiàn)RDL層數(shù)突破至6層,支持1.6Tbps的SerDes通道集成,為5G基站和數(shù)據(jù)中心加速器提供了高密度互連解決方案。

針對(duì)局部高密度互連需求,InFO-L平臺(tái)通過(guò)嵌入式LSI(局部硅互連)芯片解決了傳統(tǒng)RDL的密度瓶頸。該技術(shù)將微型硅橋接片嵌入RDL層中,在特定區(qū)域?qū)崿F(xiàn)亞微米級(jí)互連(如0.8μm節(jié)距),同時(shí)保留扇出工藝的大面積布局優(yōu)勢(shì)。英特爾在Meteor Lake處理器中采用的Foveros技術(shù)即屬此類(lèi),其LSI芯片通過(guò)預(yù)先植入的深溝槽電容(DTC)有效抑制電源噪聲,使多芯片系統(tǒng)在150W功耗下仍能維持1.1V的核心電壓穩(wěn)定度。行業(yè)動(dòng)態(tài)顯示,AMD下一代Zen5架構(gòu)處理器將采用InFO-L與3D V-Cache技術(shù)的混合封裝,通過(guò)LSI芯片實(shí)現(xiàn)三級(jí)緩存與計(jì)算核心的垂直互連,預(yù)計(jì)帶寬密度將突破300GB/s/mm2。

從技術(shù)演進(jìn)路徑看,InFO平臺(tái)正通過(guò)材料創(chuàng)新與工藝解耦持續(xù)拓展邊界。玻璃基板的應(yīng)用研究已進(jìn)入實(shí)操階段,其高平整度與超薄化特性可支持更精密的TSV制造;而RDL層與LSI芯片的協(xié)同設(shè)計(jì),則推動(dòng)封裝從被動(dòng)互連向主動(dòng)功能集成轉(zhuǎn)型。

此外,InFO與SoIC技術(shù)的深度融合正在催生新一代3D系統(tǒng)級(jí)封裝——通過(guò)前道鍵合實(shí)現(xiàn)芯片垂直堆疊,再通過(guò)扇出型RDL完成橫向擴(kuò)展,這種"立體扇出"架構(gòu)已在臺(tái)積電的3DFabric技術(shù)路線(xiàn)圖中明確標(biāo)注為2026年量產(chǎn)目標(biāo)。這些進(jìn)展共同印證了先進(jìn)封裝技術(shù)正在從"連接載體"演變?yōu)?系統(tǒng)賦能者",為摩爾定律的延續(xù)提供關(guān)鍵支撐。

超高密度互連的InFO封裝

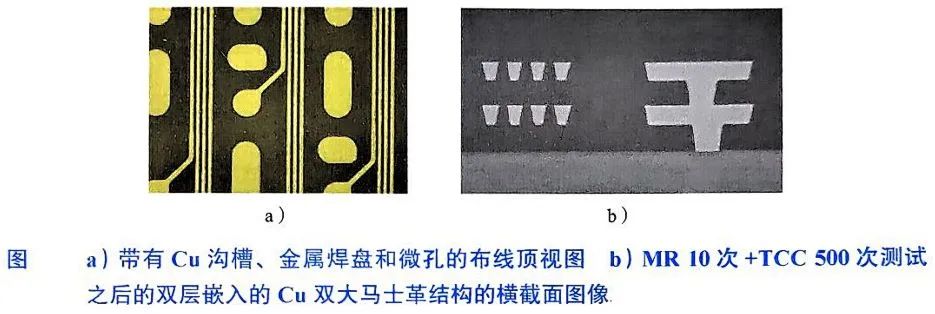

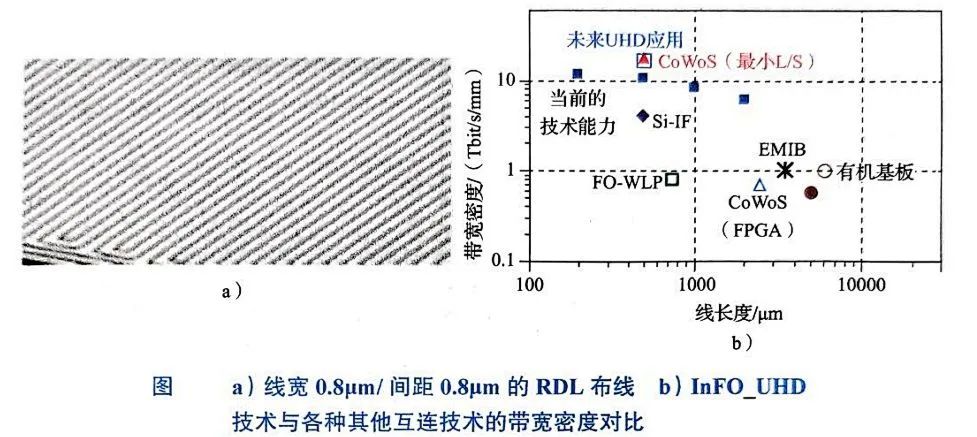

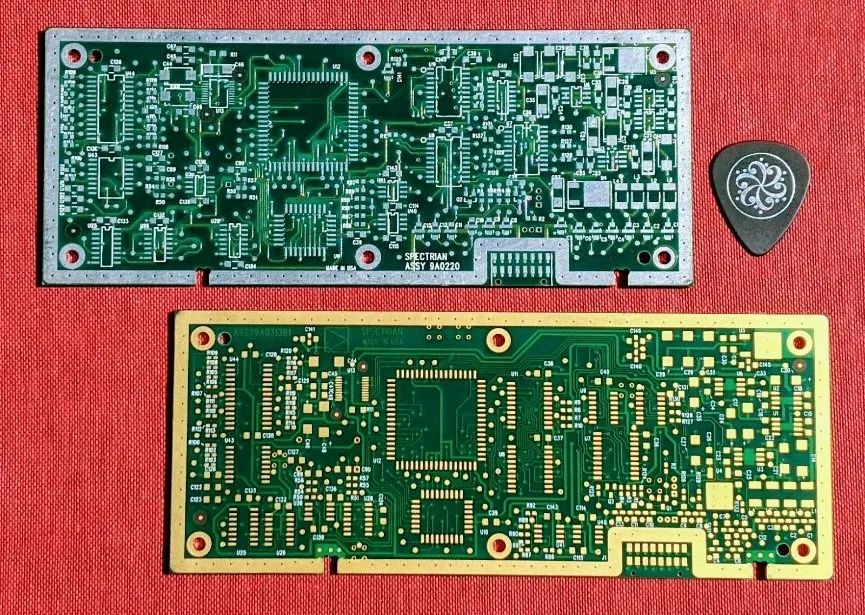

在先進(jìn)封裝技術(shù)向亞微米級(jí)互連密度突破的進(jìn)程中,臺(tái)積電的InFO-UHD(超高密度互連扇出型封裝)技術(shù)通過(guò)工藝創(chuàng)新重新定義了晶圓級(jí)封裝的性能邊界。作為InFO平臺(tái)的延伸,該技術(shù)采用銅雙大馬士革工藝與液態(tài)光敏介質(zhì)膜結(jié)合,在300mm晶圓上實(shí)現(xiàn)了線(xiàn)寬/間距(L/S)低至0.8μm/0.8μm的精細(xì)布線(xiàn),單層RDL通過(guò)5μm級(jí)微孔與2μm/1μm逃逸布線(xiàn)構(gòu)建多層互連網(wǎng)絡(luò)。其核心突破在于通過(guò)化學(xué)機(jī)械拋光(CMP)工藝實(shí)現(xiàn)銅覆蓋層與種子層的精準(zhǔn)平坦化,不僅解決了傳統(tǒng)半加成工藝(SAP)中銅布線(xiàn)鉆蝕與附著力不足的問(wèn)題,更將介質(zhì)層厚度均勻性控制在±0.5μm以?xún)?nèi),為高頻信號(hào)傳輸提供了超低損耗的傳輸通道。

可靠性驗(yàn)證顯示,經(jīng)10次回流焊+500次溫度循環(huán)(65~150℃)及96小時(shí)無(wú)偏壓HAST測(cè)試后,Cu-介質(zhì)層界面未出現(xiàn)分層,微孔與焊盤(pán)內(nèi)部亦無(wú)裂紋,印證了該工藝在極端環(huán)境下的穩(wěn)定性。信號(hào)完整性方面,InFO-UHD通過(guò)優(yōu)化RDL表面粗糙度(低至0.5nm),將50GHz頻段下的歸一化傳輸損耗(NTL)控制在傳統(tǒng)SAP工藝的70%以下,尤其在差分對(duì)設(shè)計(jì)(GSSG鏈路)中,通過(guò)線(xiàn)寬/間距/高度(L/S/H)的精確調(diào)優(yōu),有效抑制了電容效應(yīng)對(duì)阻抗匹配的影響。

性能對(duì)比數(shù)據(jù)凸顯其技術(shù)優(yōu)勢(shì):在邏輯-邏輯集成場(chǎng)景中,雙層RDL結(jié)構(gòu)可實(shí)現(xiàn)10Tbit/s/mm的帶寬密度,較CoWoS平臺(tái)提升2.5倍;能量效率方面,500μm線(xiàn)長(zhǎng)下達(dá)到0.061pJ/bit,與硅轉(zhuǎn)接板技術(shù)(Si-IF)持平,但線(xiàn)寬僅為后者的40%,且在HBM2存儲(chǔ)接口中以0.62pJ/bit的能效超越硅轉(zhuǎn)接板的0.83pJ/bit。值得關(guān)注的是,該技術(shù)無(wú)需依賴(lài)半導(dǎo)體晶圓廠(chǎng)的前道制程設(shè)備,可基于現(xiàn)有InFO產(chǎn)線(xiàn)升級(jí),顯著降低了高端封裝的準(zhǔn)入門(mén)檻。

-

芯片

+關(guān)注

關(guān)注

463文章

54304瀏覽量

468395 -

晶圓

+關(guān)注

關(guān)注

53文章

5441瀏覽量

132638 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

557瀏覽量

1053

原文標(biāo)題:InFO芯片先置集成技術(shù)及其封裝

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

PCB技術(shù)詳解:HDI技術(shù)實(shí)現(xiàn)高密度互連板

器件高密度BGA封裝設(shè)計(jì)

探討高密度小間距LED屏工藝

高密度封裝技術(shù)推動(dòng)測(cè)試技術(shù)發(fā)展

高密度互連PCB有什么不同的地方

為什么要使用高密度互連?

PCB技術(shù)詳解:HDI技術(shù)實(shí)現(xiàn)高密度互連板資料下載

高密度互連印刷電路板如何實(shí)現(xiàn)高密度互連HDIne ?

高密度互連,引爆后摩爾技術(shù)革命

高密度封裝失效分析關(guān)鍵技術(shù)和方法

詳解超高密度互連的InFO封裝技術(shù)

詳解超高密度互連的InFO封裝技術(shù)

評(píng)論