【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

在半導體行業,光刻(Photo)工藝技術就像一位技藝高超的藝術家,負責將復雜的電路圖案從掩模轉印到光滑的半導體晶圓上。作為制造過程中不可或缺的一步,光刻技術的精準與否直接關系到芯片的性能、成本和生產效率。這一工藝的重要性,讓許多業內人士稱其為半導體的靈魂。所以,本章節主要跟大家分享的就是半導體光刻(Photo)工藝技術的核心原理和未來挑戰。

一、光刻(Photo)工藝技術的起源與發展

光刻是半導體工業的核心工藝技術。自1960年Fairchild Semiconductor的羅伯特·諾伊斯發明單片集成電路以來,光刻一直是主要的光刻工藝技術。

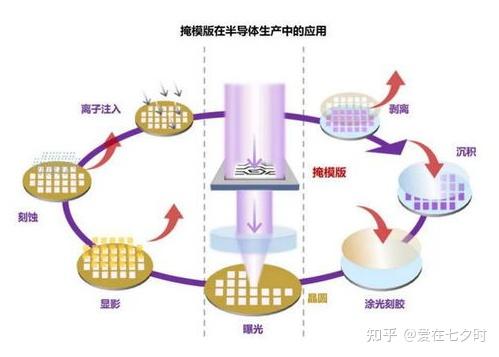

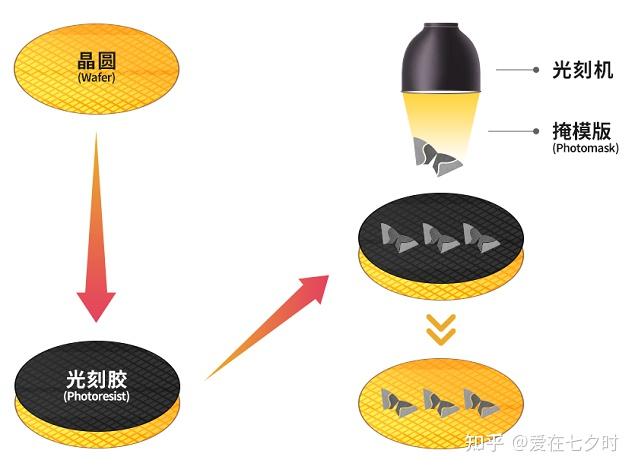

光刻(Photo)工藝技術本質上是,掩膜版用于對光刻膠進行圖案化,從而實現圖案化沉積和蝕刻工藝。光刻工藝的最終分辨率由所用光源的波長決定。

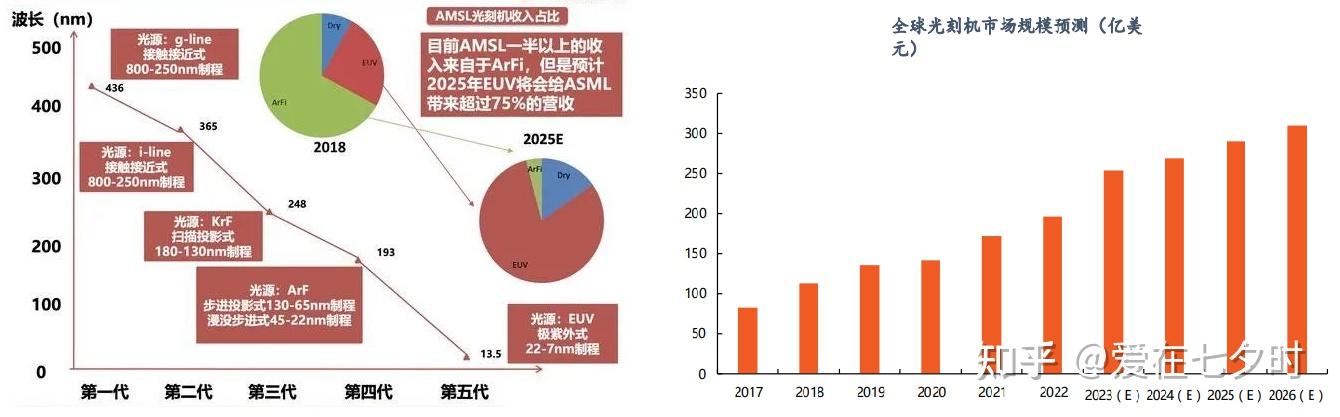

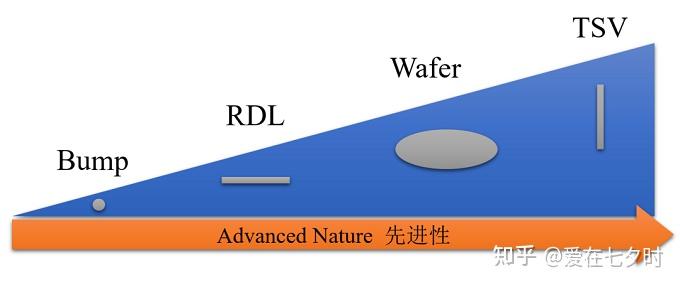

在短波長光刻源的開發方面取得的進展,使得以摩爾定律為特征的電路密度不斷增加。在過去光刻所需光源是Mercury discharged lamps,例如365nm時期采用的i-Line,但最近KrF為248nm或ArF為193nm的準分子激光器成為了首選光源。采用浸潤式光刻技術,需要將透鏡和芯片浸沒在折射率比空氣高的水中,由此ArF激光器獲得的最終分辨率約為50nm。

過去二十年,193nm波長的光刻技術得到了發展。雖然使用F2準分子激光的157nm光刻技術取得了一些突破,但人們主要關注的還是使用13.5nm軟X射線作為光源的極紫外(EUV)光刻技術。

荷蘭ASML在EUV技術的研發中發揮了主導作用,目前其EUV設備主要被包括英特爾、三星和臺積電在內的先進CMOS代工廠用于生產。

EUV光刻使用波長僅為13.5納米的極紫外光,這種短波長的光源能夠實現更小的特征尺寸(約10納米甚至更小)。然而,EUV光刻的實現面臨著一系列挑戰,如光源功率、掩膜制造、光學系統的精度等。經過多年的研究和投資,ASML公司在2010年代率先實現了EUV光刻的商業化應用,使得芯片制造跨入了5納米以下的工藝節點。

隨著光刻技術接近物理極限,學術界和工業界正在探索新的技術,如多光子光刻、電子束光刻、納米壓印光刻等。這些新技術可能會在未來的“后摩爾時代”起到關鍵作用。此外,量子計算和其他新型計算架構的出現,也為光刻技術的發展提供了新的機遇與挑戰。

二、光刻(Photo)工藝技術的介紹

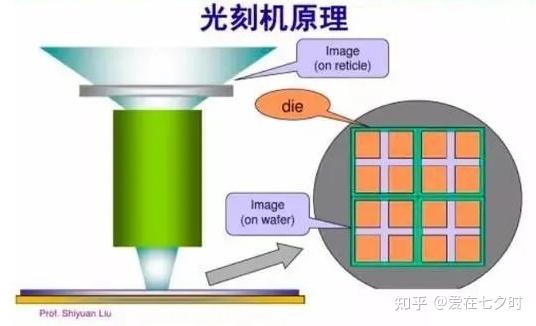

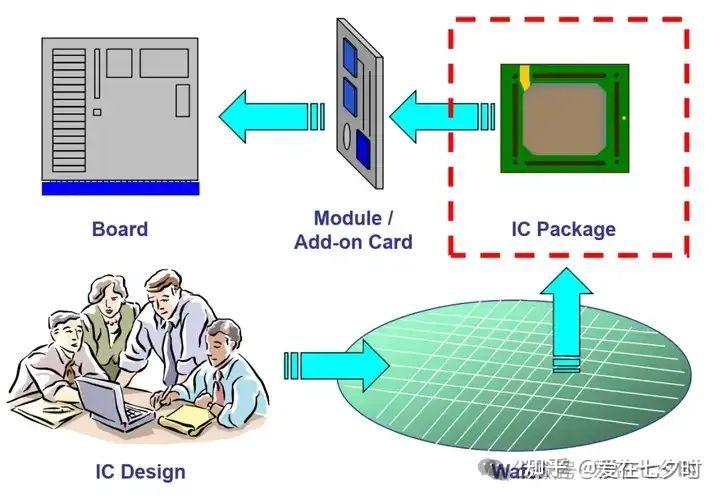

光刻,英文全稱:Photolithography,簡稱為“Photo”。光刻工藝因通過將圖形掩模暴露在光線下將電路設計轉移到晶圓上而得名。在晶圓上制作復制品就像在感光紙上洗印黑白底片一樣。

因為光刻工藝是半導體制造中最為重要的工藝步驟之一。主要作用是將掩膜板上的圖形復制到硅片上,為下一步進行刻蝕或者離子注入工序做好準備。光刻的成本約為整個硅片制造工藝的1/3,耗費時間約占整個硅片工藝的40~60%。

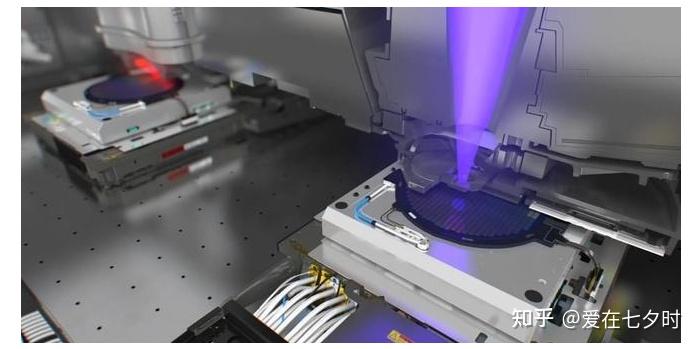

光刻機是生產線上最貴的機臺,5~15百萬美元/臺。主要是貴在成像系統(由15~20個直 徑為200~300mm的透鏡組成)和定位系統(定位精度小于10nm)。其折舊速度非常快,大約3~9萬人民幣/天,所以也稱之為印鈔機。光刻部分的主 要機臺包括兩部分:軌道機(Tracker),用于涂膠顯影;掃描曝光機(Scanning )。

而隨著電路圖形變得越來越密集,芯片元件也需要使用高精度納米級工藝來縮小。制作這些更精細的電路圖形完全取決于光刻工藝,因此,隨著芯片變小,高精度和先進的光刻工藝技術是必不可少的。

三、光刻(Photo)工藝技術的基本原理

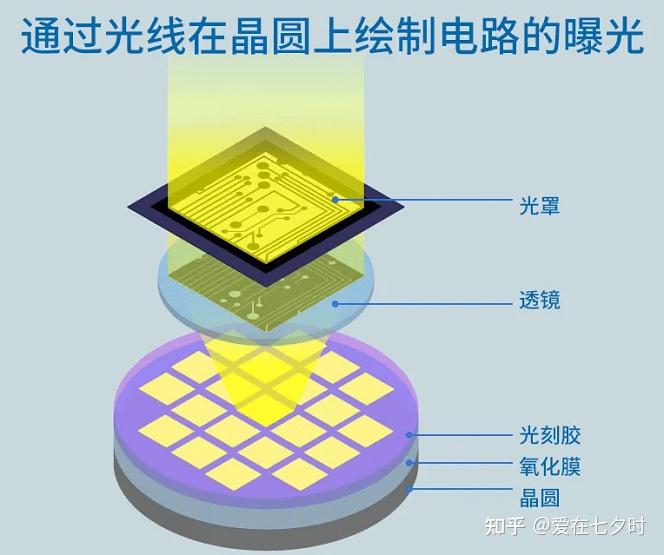

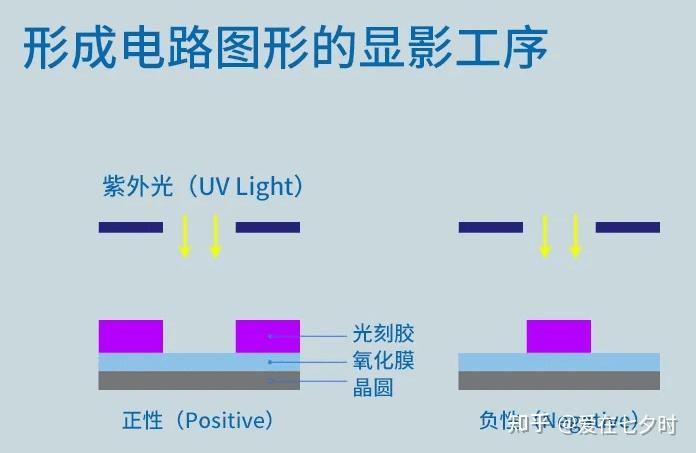

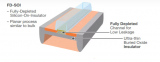

半導體光刻(Photo)工藝技術是通過光學成像和光化學反應實現電路圖案的微縮化轉移,其原理是運用光的特性,將復雜的電路圖案從掩膜版轉移至基片上。具體而言,該過程依賴于光學-化學反應,光源照射使光敏材料發生化學或物理變化,最終通過顯影得到所需圖案。常見的光敏材料有正性光刻膠和負性光刻膠,分別在感光與顯影過程中展現不同的去除特性,其核心原理分如下兩個方面:

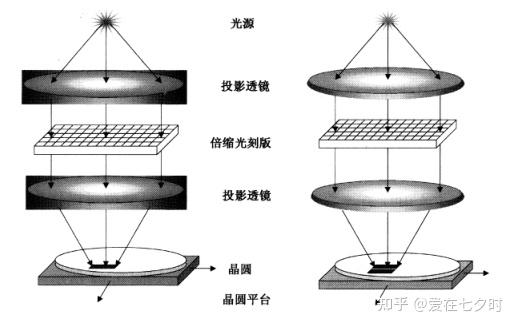

1、光學投影系統?

光刻機利用紫外光或極紫外光作為光源,通過掩模版(光罩)攜帶電路圖形信息,經復雜光學系統將圖案按比例縮小并投影至涂有光刻膠的硅片表面。此過程類似照相技術,但精度要求達到納米級。

?2、光化學反應?

光刻膠(光致抗蝕劑)是關鍵材料,分為正膠和負膠兩種類型。正膠在曝光后溶解度增加,顯影時被溶解;負膠則相反,未曝光區域被溶解。這一特性使得掩模版圖案能在硅片上形成對應抗蝕結構。

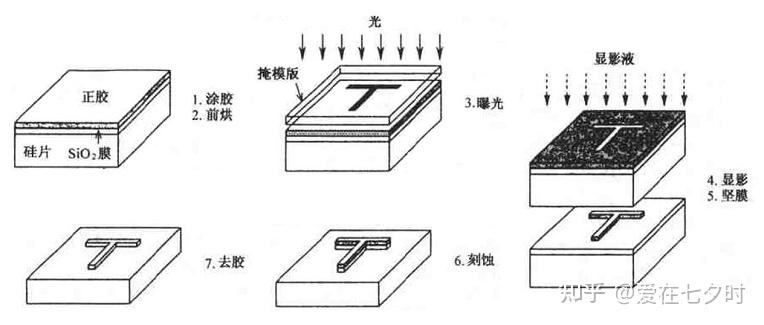

四、光刻(Photo)工藝技術的過程

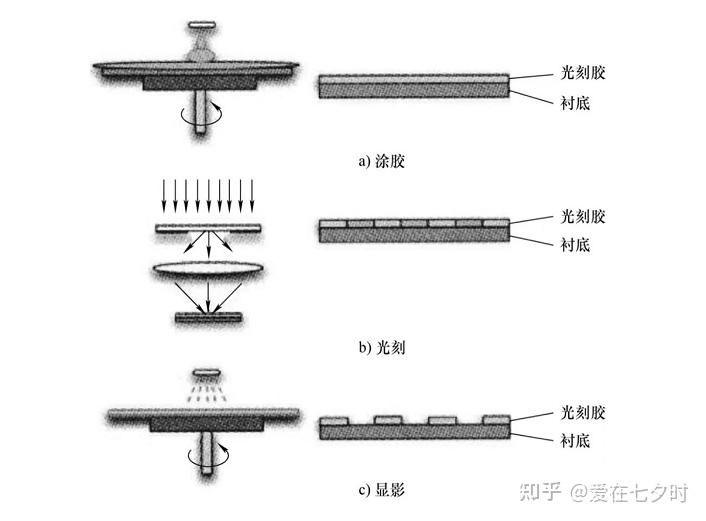

一般的光刻工藝要經歷硅片表面清洗烘干、涂底、旋涂光刻膠、軟烘、對準曝光、后烘、顯影、硬烘、刻蝕、檢測等工序,以下就是詳細工藝流程:

1、硅片清洗烘干(Cleaning and Pre-Baking)

(1)方法

濕法清洗+去離子水沖洗+脫水烘焙(熱板150~2500C,1~2分鐘,氮氣保護)

(2)目的

a、除去表面的污染物(顆粒、有機物、工藝殘余、可動離子);

b、除去水蒸氣,是基底表面由親水性變為憎水性,增強表面的黏附性(對光刻膠或者是HMDS-〉六甲基二硅胺烷)。

2、涂底(Priming)

(1)方法

a、氣相成底膜的熱板涂底。HMDS蒸氣淀積,200~2500C,30秒鐘;優點:涂底均勻、避免顆粒污染;

b、旋轉涂底。缺點:顆粒污染、涂底不均勻、HMDS用量大。

(2)目的

使表面具有疏水性,增強基底表面與光刻膠的黏附性。

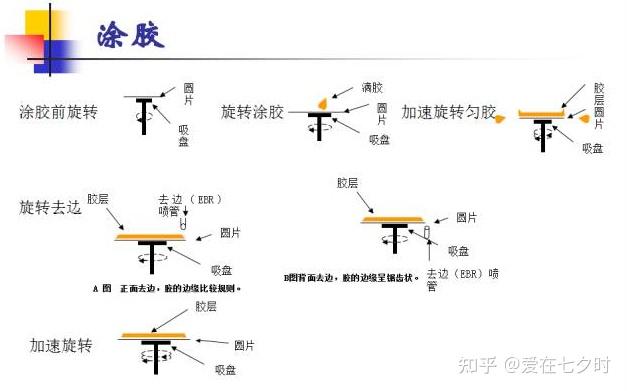

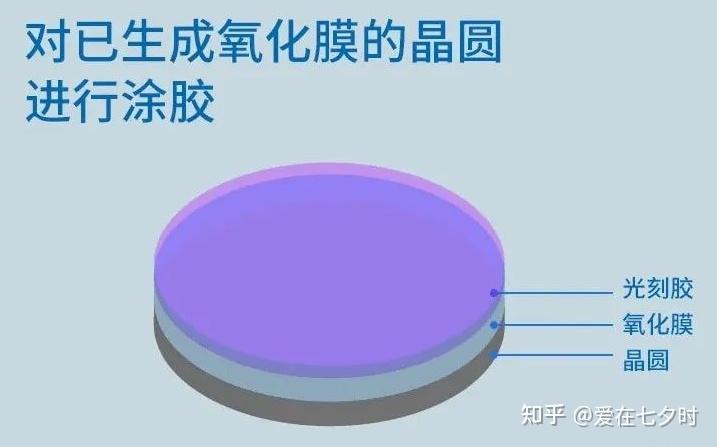

3、旋轉涂膠(Spin-on PR Coating)

(1)方法

a、靜態涂膠(Static)。硅片靜止時,滴膠、加速旋轉、甩膠、揮發溶劑(原光刻膠的溶劑約占65~85%,旋涂后約占10~20%);

b、動態(Dynamic)。低速旋轉(500rpm_rotation per minute)、滴膠、加速旋轉(3000rpm)、甩膠、揮發溶劑。

決定光刻膠涂膠厚度的關鍵參數:光刻膠的黏度(Viscosity),黏度越低,光刻膠的厚度越薄;旋轉速度,速度越快,厚度越薄;

(2)影響光刻膠厚度均運性的參數

旋轉加速度,加速越快越均勻;與旋轉加速的時間點有關。

一般旋涂光刻膠的厚度與曝光的光源波長有關(因為不同級別的曝光波長對應不同的光刻膠種類和分辨率):

I-line最厚,約0.7~3μm;KrF的厚度約0.4~0.9μm;ArF的厚度約0.2~0.5μm。

4、軟烘(Soft Baking)

(1)方法

真空熱板,85~120℃,30~60秒;

(2)目的

除去溶劑(4~7%);增強黏附性;釋放光刻膠膜內的應力;防止光刻膠玷污設備;

5、邊緣光刻膠的去除(EBR,Edge Bead Removal)

光刻膠涂覆后,在硅片邊緣的正反兩面都會有光刻膠的堆積。邊緣的光刻膠一般涂布不均勻,不能得到很好的圖形,而且容易發生剝離(Peeling)而影響其它部分的圖形。所以需要去除。

(1)方法

a、化學的方法(Chemical EBR)

軟烘后,用PGMEA或EGMEA去邊溶劑,噴出少量在正反面邊緣處,并小心控制不要到達光刻膠有效區域;

b、光學方法(Optical EBR)

即硅片邊緣曝光(WEE,Wafer Edge Exposure)。在完成圖形的曝光后,用激光曝光硅片邊緣,然后在顯影或特殊溶劑中溶解

6、對準并曝光(Alignment and Exposure)

(1)對準方法

a、預對準,通過硅片上的notch或者flat進行激光自動對準;

b、通過對準標志(Align Mark),位于切割槽(Scribe Line)上。另外層間對準,即套刻精度(Overlay),保證圖形與硅片上已經存在的圖形之間的對準。

曝光中最重要的兩個參數是:曝光能量(Energy)和焦距(Focus)。如果能量和焦距調整不好,就不能得到要求的分辨率和大小的圖形。表現為圖形的關鍵尺寸超出要求的范圍。

(2)曝光方法

a、接觸式曝光(Contact Printing)

掩膜板直接與光刻膠層接觸。曝光出來的圖形與掩膜板上的圖形分辨率相當,設備簡單。

缺點:光刻膠污染掩膜板;掩膜板的磨損,壽命很低(只能使用5~25次);1970前使用,分辨率〉0.5μm。

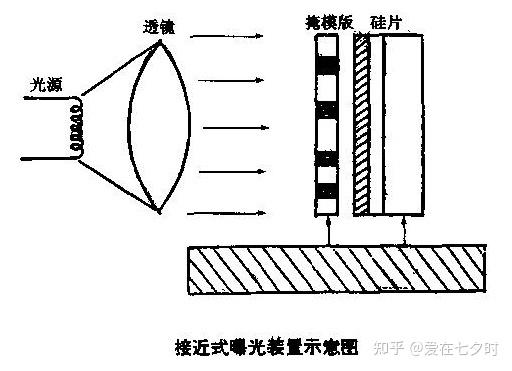

b、接近式曝光(Proximity Printing)

掩膜板與光刻膠層的略微分開,大約為10~50μm。可以避免與光刻膠直接接觸而引起的掩膜板損傷。但是同時引入了衍射效應,降低了分辨率。1970后適用,但是其最大分辨率僅為2~4μm。

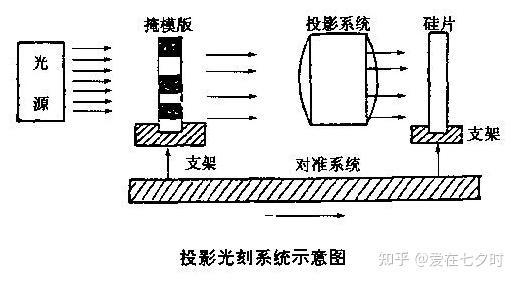

c、投影式曝光(Projection Printing)

在掩膜板與光刻膠之間使用透鏡聚集光實現曝光。一般掩膜板的尺寸會以需要轉移圖形的4倍制作。

優點:提高了分辨率;掩膜板的制作更加容易;掩膜板上的缺陷影響減小。

(3)投影式曝光分類

掃描投影曝光(Scanning Project Printing)。70年代末~80年代初,〉1μm工藝;掩膜板1:1,全尺寸;

a、步進重復投影曝光(Stepping-repeating Project Printing或稱作Stepper)。

80年代末~90年代,0.35μm(I line)~0.25μm(DUV)。掩膜板縮小比例(4:1),曝光區域(Exposure Field)22×22mm(一次曝光所能覆蓋的區域)。增加了棱鏡系統的制作難度。

b、掃描步進投影曝光(Scanning-Stepping Project Printing)

90年代末~至今,用于≤0.18μm工藝。采用6英寸的掩膜板按照4:1的比例曝光,曝光區域(Exposure Field)26×33mm。

優點:增大了每次曝光的視場;提供硅片表面不平整的補償;提高整個硅片的尺寸均勻性。但是,同時因為需要反向運動,增加了機 械系統的精度要求。

在曝光過程中,需要對不同的參數和可能缺陷進行跟蹤和控制,會用到檢測控制芯片/控片 (Monitor Chip)。根據不同的檢測控制對象,可以分為以下幾種:

a、顆粒控片(Particle MC)

用于芯片上微小顆粒的監控,使用前其顆粒數應小于10顆;

b、卡盤顆粒控片(Chuck Particle MC)

測試光刻機上的卡盤平坦度的專用芯片,其平坦度要求非常高;

c、焦距控片(Focus MC)

作為光刻機監控焦距監控;

d、關鍵尺寸控片(Critical Dimension MC)

用于光刻區關鍵尺寸穩定性的監控;

e、光刻膠厚度控制(PhotoResist Thickness MC)

光刻膠厚度測量;

f、光刻缺陷控片(PDM,Photo Defect Monitor)

光刻膠缺陷監控。

舉例:0.18μm的CMOS掃描步進光刻工藝。

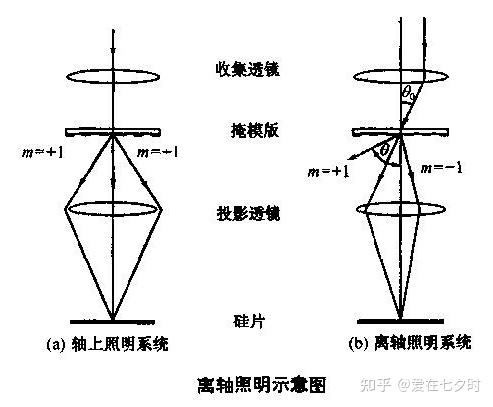

光源:KrF氟化氪DUV光源(248nm) ;數值孔徑NA:0.6~0.7;焦深DOF:0.7μm

分辨率Resolution:0.18~0.25μm

(一般采用了偏軸照明OAI_Off- Axis Illumination和相移掩膜板技術PSM_Phase Shift Mask增強);

套刻精度Overlay:65nm;產能Throughput:30~60wafers/hour(200mm);視場尺寸Field Size:25×32mm;

7、后烘(PEB,Post Exposure Baking)

(1)方法

熱板,110~1300C,1分鐘。

(2)目的

a、減少駐波效應;

b、激發化學增強光刻膠的PAG產生的酸與光刻膠上的保護基團發生反應并移除基團使之能溶解于顯影液。

8、顯影(Development)

(1)方法

a、整盒硅片浸沒式顯影(Batch Development)。

缺點:顯影液消耗很大;顯影的均勻性差;

b、連續噴霧顯影(Continuous Spray Development)/自動旋轉顯影(Auto-rotation Development)。一個或多個噴嘴噴灑顯影液在硅片表面,同時硅片低速旋轉(100~500rpm)。噴嘴噴霧模式和硅片旋轉速度是實現硅片間溶 解率和均勻性的可重復性的關鍵調節參數。

c、水坑(旋覆浸沒)式顯影(Puddle Development)。噴覆足夠(不能太多,最小化背面濕度)的顯影液到硅片表面,并形成水坑形狀(顯影液的流動保持較低,以減少邊緣顯影速率的變 化)。硅片固定或慢慢旋轉。一般采用多次旋覆顯影液:第一次涂覆、保持10~30秒、去除;第二次涂覆、保持、去除。然后用去離子水沖洗(去除硅片兩面的 所有化學品)并旋轉甩干。

優點:顯影液用量少;硅片顯影均勻;最小化了溫度梯度。

(2)顯影液

a、正性光刻膠的顯影液。正膠的顯影液位堿性水溶液。KOH和NaOH因為會帶來可 動離子污染(MIC,Movable Ion Contamination),所以在IC制造中一般不用。最普通的正膠顯影液是四甲基氫氧化銨(TMAH)(標準當量濃度為0.26,溫度 15~250C)。在I線光刻膠曝光中會生成羧酸,TMAH顯影液中的堿與酸中和使曝光的光刻膠溶解于顯影液,而未曝光的光刻膠沒有影響;在化學放大光刻 膠(CAR,Chemical Amplified Resist)中包含的酚醛樹脂以PHS形式存在。CAR中的PAG產生的酸會去除PHS中的保護基團(t-BOC),從而使PHS快速溶解于TMAH顯 影液中。整個顯影過程中,TMAH沒有同PHS發生反應。

b、負性光刻膠的顯影液。二甲苯。清洗液為乙酸丁脂或乙醇、三氯乙烯。

(3)顯影中的常見問題

a、顯影不完全(Incomplete Development)。表面還殘留有光刻膠。顯影液不足造成;

b、顯影不夠(Under Development)。顯影的側壁不垂直,由顯影時間不足造成;

c、過度顯影(Over Development)。靠近表面的光刻膠被顯影液過度溶解,形成臺階。顯影時間太長。

9、硬烘(Hard Baking)

(1)方法

熱板,100~1300C(略高于玻璃化溫度Tg),1~2分鐘。

(2)目的

a、完全蒸發掉光刻膠里面的溶劑(以免在污染后續的離子注入環境,例如DNQ酚醛樹脂 光刻膠中的氮會引起光刻膠局部爆裂);

b、堅膜,以提高光刻膠在離子注入或刻蝕中保護下表面的能力;

c、進一步增強光刻膠與硅片表面之間的黏附性;

d、進 一步減少駐波效應(Standing Wave Effect)。

(3)常見問題

a、烘烤不足(Underbake)。減弱光刻膠的強度(抗刻蝕能力和離子注入中 的阻擋能力);降低針孔填充能力(Gapfill Capability for the needle hole);降低與基底的黏附能力。

b、烘烤過度(Overbake)。引起光刻膠的流動,使圖形精度降低,分辨率變差。

另外還可以用深紫外線(DUV,Deep Ultra-Violet)堅膜。使正性光刻膠樹脂發生交聯形成一層薄的表面硬殼,增加光刻膠的熱穩定性。在后面的等離子刻蝕和離子注入(125~2000C)工藝中減少因光刻膠高溫流動而引起分辨率的降低。

五、光刻(Photo)工藝的技術要點

由于光刻作為半導體制造的核心環節,其技術演進(如EUV光刻、多重曝光)持續推動芯片制程向更小節點突破,所以此工藝也有自己的技術要點:

1、多層光刻膠應用?

通過組合不同性質的光刻膠層,可提升陡直度、減少線寬誤差(CD白邊)和底部殘留,增強后續刻蝕效果。

?2、精度控制?

光刻膠厚度、曝光劑量、光學系統校準等參數共同決定最終圖案的分辨率和保真度,直接影響芯片集成度與性能。

六、光刻(Photo)工藝技術的分類

1、接觸式光刻與接近式光刻

接觸式光刻是指光刻膠與掩模直接接觸進行曝光的光刻技術。在這種方法中,掩模上的圖案直接轉移到光刻膠上,實現高精度的圖案復制。由于接觸式光刻中掩模與光刻膠緊密接觸,因此可以獲得較高的分辨率。然而,這種方法也存在一些缺點,如掩模與光刻膠之間的摩擦可能導致掩模和光刻膠的損傷,從而影響圖案的質量。

接近式光刻則是通過光學系統將掩模與光刻膠表面保持一定距離進行曝光的光刻技術。這種技術避免了掩模與光刻膠的直接接觸,從而減少了掩模和光刻膠的損傷。然而,由于存在衍射效應,接近式光刻的分辨率通常低于接觸式光刻。此外,為了保持一定的曝光均勻性,接近式光刻通常需要使用更復雜的光學系統。

2、投影式光刻技術的進展

投影式光刻技術作為半導體制造中的核心技術之一,近年來取得了諸多進展,這些進展不僅推動了半導體工藝的不斷進步,也為電子產品性能的提升奠定了堅實基礎。

(1)技術原理與分類

投影式光刻技術利用光學-化學反應原理,將設計好的微圖形結構通過投影方式轉移到覆有感光材料的晶圓等基材表面上。根據使用光源和操作方式的不同,投影式光刻機可分為多種類型,如激光光刻機、極紫外(EUV)光刻機等。

(2)技術進展

a. 分辨率提升

隨著半導體工藝節點的不斷縮小,投影式光刻機的分辨率也在持續提升。目前,先進的EUV光刻機已經能夠實現5納米甚至更小線寬的制造,這對于提高芯片性能和功耗比具有重要意義。

b. 光源技術革新

EUV光刻技術的引入是投影式光刻機的一大突破。EUV光源能夠穿透傳統光刻技術難以達到的深紫外波段,從而顯著提高光刻效率和精度。此外,隨著LED等新型光源技術的發展,基于UV-LED的顯微鏡投影光刻(MPP)等低成本、高分辨率的制造技術也開始嶄露頭角。

c. 投影物鏡優化

投影物鏡是光刻機的核心部件之一,其性能直接影響光刻精度和效率。近年來,通過改進物鏡的設計和制造工藝,如采用更先進的材料和工藝、優化物鏡的像差校正等,投影式光刻機的成像質量得到了顯著提升。

d. 自動化與智能化升級

隨著人工智能和機器學習技術的發展,投影式光刻機逐漸實現了更高級別的自動化和智能化。通過引入先進的控制系統和算法,光刻機能夠自動調整工藝參數、優化光刻過程,從而提高生產效率和產品質量。

e. 成本降低與廣泛應用

隨著技術的不斷成熟和市場競爭的加劇,投影式光刻機的成本逐漸降低,使其在更廣泛的領域得到應用。除了傳統的芯片制造領域外,投影式光刻技術還開始應用于微機電系統(MEMS)、光電子器件等新興領域。

七、光刻(Photo)工藝技術的挑戰與解決方案

1、線寬控制與分辨率的挑戰

a. 線寬調整

線條寬度的調整直接影響圖形的視覺效果和精確度。在復雜圖形中,精確控制線寬是一項挑戰,需要算法的支持和硬件的協助。

b. 分辨率優化

提高分辨率可以增強圖像的清晰度,但高分辨率的圖像在處理和存儲時都會帶來更大的挑戰。特別是在線寬控制方面,高分辨率圖像可能需要更精細的處理。

c. 軟件算法

為了實現在線寬調整和分辨率優化過程中的實時處理,軟件算法的研究和優化是必不可少的。這包括圖像處理算法、圖形渲染算法等。

d. 硬件支持

硬件性能的提升對于處理高分辨率圖像和精確控制線寬至關重要。高效的處理器、充足的內存和快速的存儲設備都是必要的。

e. 應用場景

不同的應用場景,如打印、顯示、出版等,對圖形的線寬和分辨率有不同的要求。因此,需要根據具體應用場景制定相應的線寬控制與分辨率優化策略。

f. 跨平臺兼容性

確保線寬控制與分辨率優化在不同操作系統和設備上的兼容性是一項挑戰。需要開發適用于多種平臺和設備的解決方案。

g. 用戶交互

提供直觀易用的界面,方便用戶進行線寬和分辨率的調整,同時確保用戶能夠理解和控制這些參數對圖形質量的影響

h. 性價比

在保證圖形質量的前提下,降低成本、提高產品性價比是另一個需要考慮的挑戰。這包括優化算法以減少計算資源消耗、使用更經濟的硬件等。

2、光刻設備的精度、性能與穩定性提升

光刻設備在半導體制造中扮演著至關重要的角色。隨著技術的不斷進步,光刻設備的精度、性能已經提升至納米級別,這意味著它能夠在微小的芯片表面上精確地雕刻出復雜的電路圖案。

同時,光刻設備的穩定性也得到了顯著增強,確保了在長時間、高強度的生產過程中,光刻過程的高效性和穩定性。

這種精度、性能與穩定性的提升,得益于先進的制造工藝和精密的控制系統。光刻設備采用了高精度的激光器和光學系統,能夠確保光線的精確聚焦和定位。此外,通過先進的控制系統和算法,光刻設備能夠實時監測和調整工藝參數,從而確保每一片芯片都達到最佳的質量標準。

八、光刻(Photo)工藝技術的未來發展方向

1、極紫外光刻(EUV)

EUV技術在高成本與復雜技術間找尋平衡,持續開拓其應用領域。

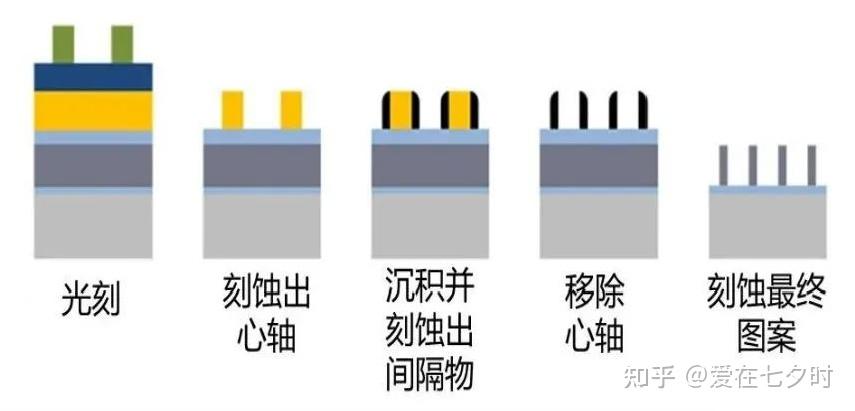

2、多重曝光

為了打破目前光刻分辨率的桎梏,多重曝光工藝逐步被引入,成為提升圖案精度的研究熱點。

3、新型光刻膠

開發高性能光刻膠以提升整個工藝的精度和穩定性。

4、環保措施

光刻所需材料及其生產對環境的影響不容忽視,因此開發環保材料與工藝變得日益重要。

九、寫在最后面的話

隨著科技的不斷進步,光刻(Photo)工藝技術也在不斷 evolución。如準分子光刻技術(MLA)和極紫外光刻技術(EUV)正逐步應用于半導體制造,極大提升了分辨率和特征尺寸,推動了芯片技術的進步。

光刻(Photo)工藝技術的創新不僅限于設備的提升,更體現在與新興技術的結合,譬如人工智能助力芯片設計與制造的智能化。AI能夠通過算法優化圖案設計,提高整體制造效率,進一步推動光刻(Photo)工藝技術的進展。

在實用層面,光刻(Photo)工藝技術的應用廣泛,不僅限于個人電子設備,如智能手機、平板電腦,還廣泛應用于汽車電子、物聯網設備等多個領域,成為現代科技的基石之一。

然而,隨著對更高技術要求的不斷演進,光刻(Photo)工藝技術也面臨著材料和成本上的挑戰。如何在保證制造精度的同時降低生產成本,成為行業內亟待解決的問題。

總而言之,光刻(Photo)工藝技術作為半導體制造的核心工藝,其背后的原理和不斷進化的方法不僅影響著電子產品的發展,同時也在推動科技的前行。對這一技術的深入研究與應用探索,勢必將對未來半導體行業產生深遠影響。所以,光刻(Photo)工藝技術依然是半導體領域一顆璀璨的明珠!

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

半導體

+關注

關注

339文章

30992瀏覽量

265451 -

光刻

+關注

關注

8文章

367瀏覽量

31368

發布評論請先 登錄

半導體制造中刻蝕工藝技術介紹

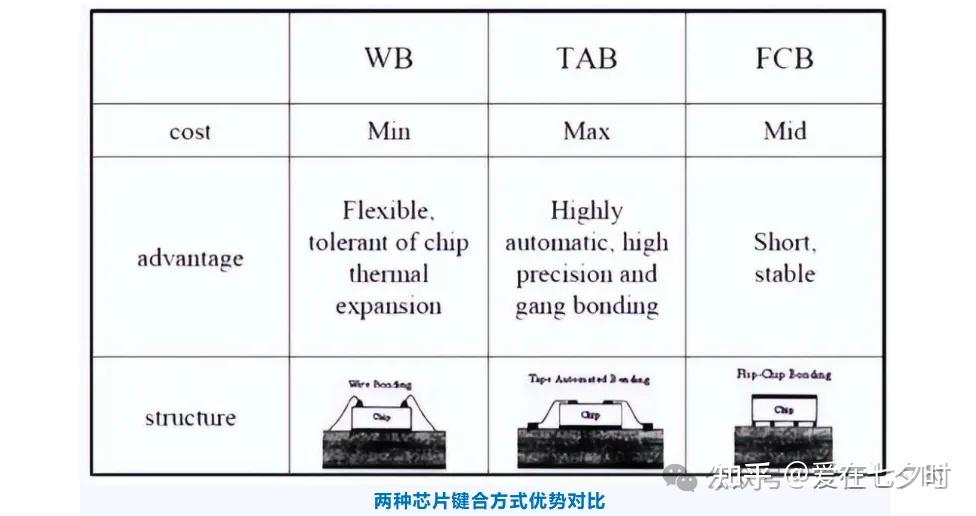

半導體芯片制造技術——“芯片鍵合”工藝技術的詳解;

熱壓鍵合工藝的技術原理和流程詳解

半導體封裝Wire Bonding (引線鍵合)工藝技術的詳解;

半導體芯片封裝“CoWoS工藝技術”的詳解;

半導體“封裝過程”工藝技術的詳解;

半導體“刻蝕(Etch)”工藝技術的詳解;

半導體先進封裝“Bumping(凸點)”工藝技術的詳解;

SOI工藝技術介紹

半導體后道制程“芯片鍵合(Die Bonding)”工藝技術的詳解;

半導體“光刻(Photo)”工藝技術的詳解;

半導體“光刻(Photo)”工藝技術的詳解;

評論