電子發燒友網報道(文/黃晶晶)前段時間,三星、SK海力士、美光等DRAM大廠已計劃陸續退出部分DDR4市場,將產能轉向DDR5、LPDDR5和HBM。由此引發DDR4供應鏈波動,同時在供給不足的擔憂

2025-06-19 00:54:00 10155

10155

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器緩沖器 在DDR2內存模塊的設計中,擁有高性能且穩定的寄存器緩沖器至關重要。Renesas的IDT74SSTUBF32866B就是

2025-12-24 16:30:09 124

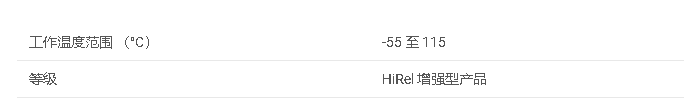

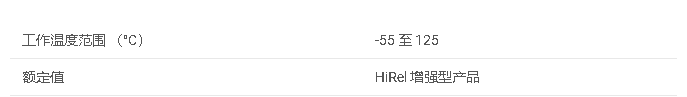

124 愛普生33.33MHz車規晶振X1E0003410500憑借±20ppm高穩、1ps低抖動及-40℃~125℃寬溫,為FPGA時鐘樹提供AEC-Q100認證基準時鐘。其6ms快啟與抗振特性保障高速SerDes與DDR4接口信號完整性,滿足ADAS與工業控制系統的嚴苛時序需求。

2025-12-18 10:15:00 222

222

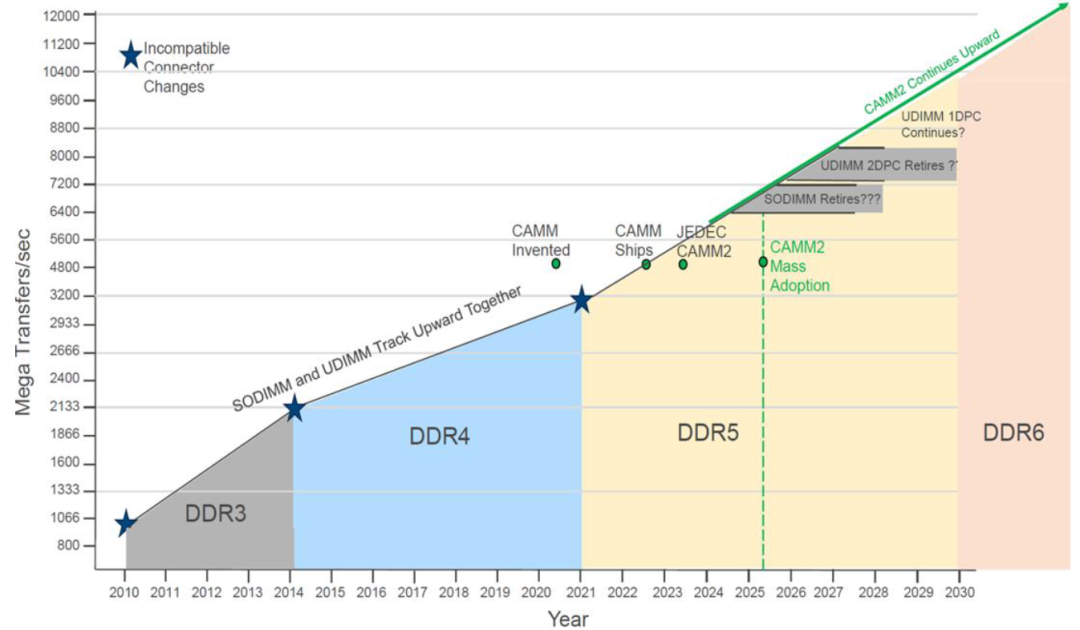

在計算機和電子設備中,存儲器扮演著數據臨時存放與快速交換的關鍵角色。其中,DDR SDRAM(雙數據速率同步動態隨機存取存儲器)已成為現代內存的主流技術之一。它不僅在速度上顯著超越前代產品,更憑借其高效傳輸機制,廣泛應用于電腦、服務器、移動設備及各類嵌入式系統中。

2025-12-08 15:20:44 293

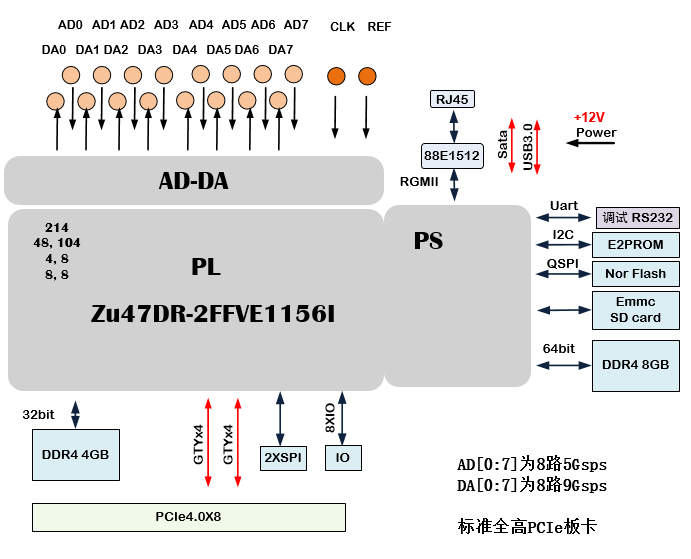

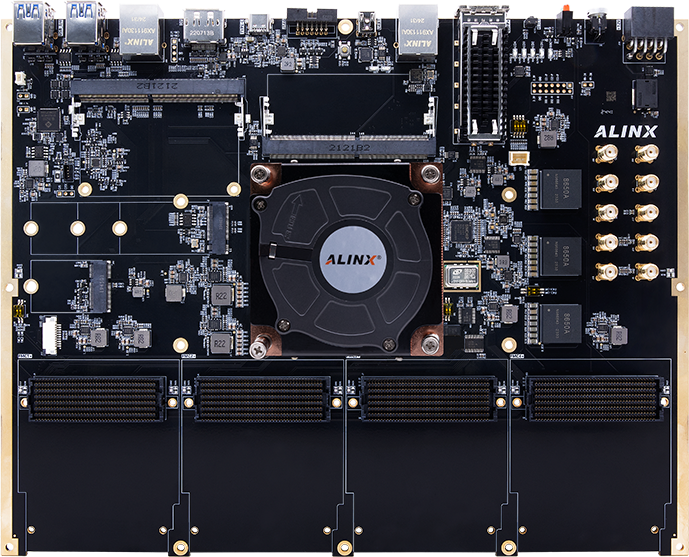

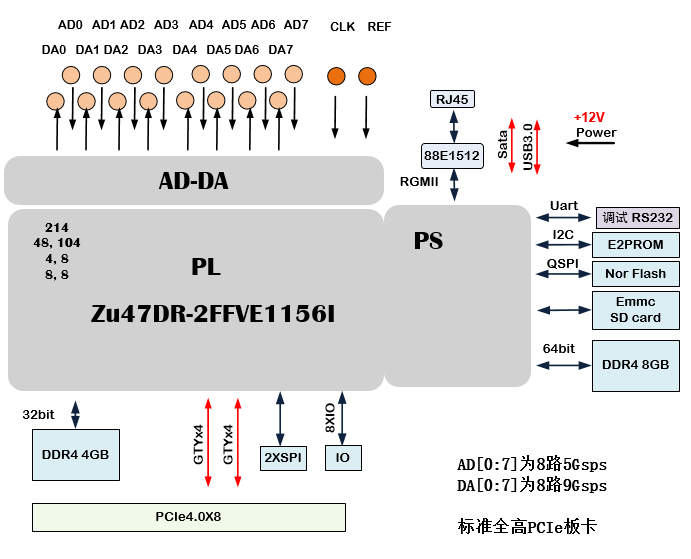

293 主處理器,完成復雜的數據采集、回放以及數據預處理。采用1片ZYNQSOC來完成信號處理算法。該平臺的主處理器VU13P外掛兩組72位DDR4SDRAM,來實現超大容量數

2025-12-04 16:02:34 287

287

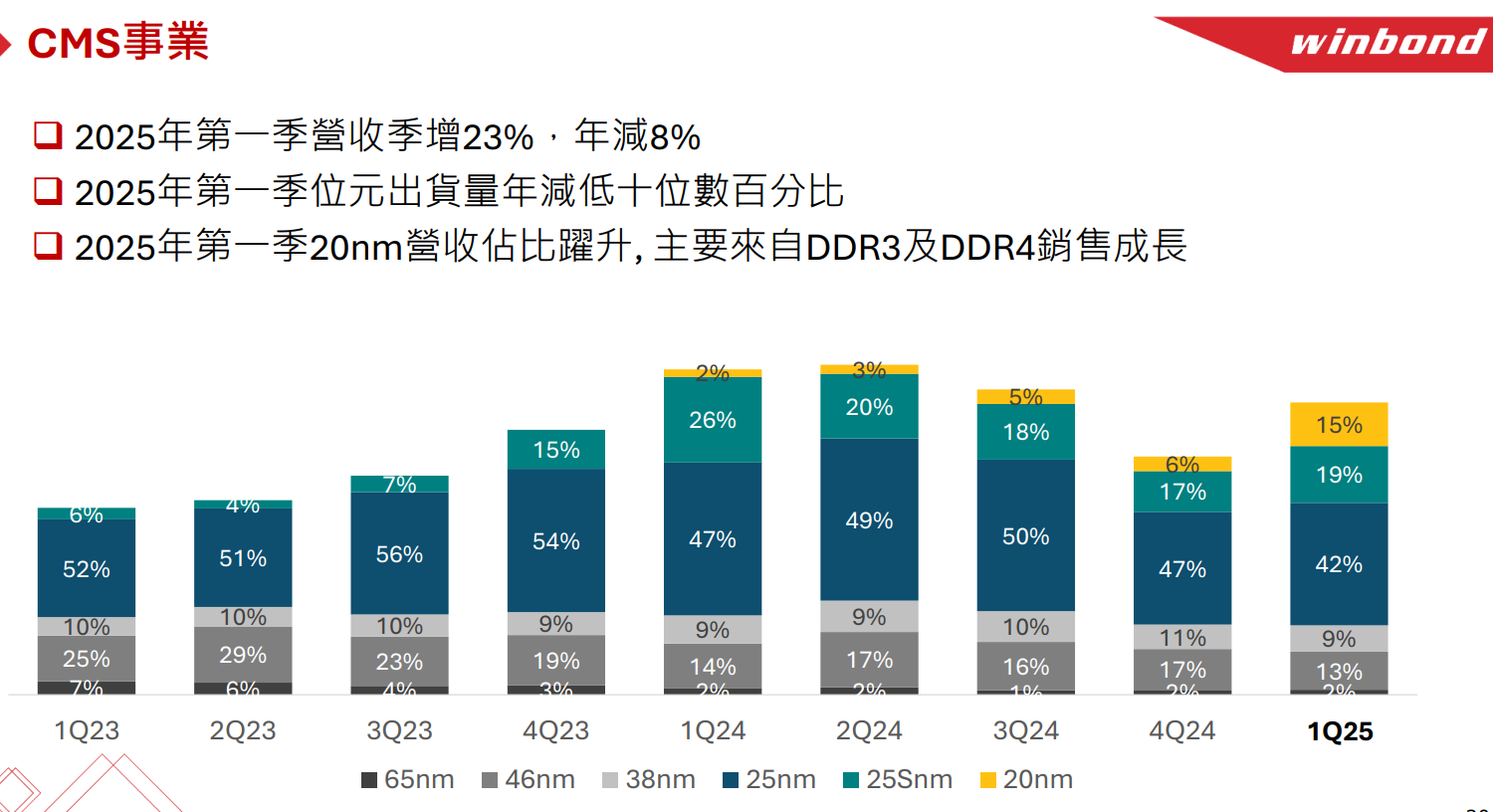

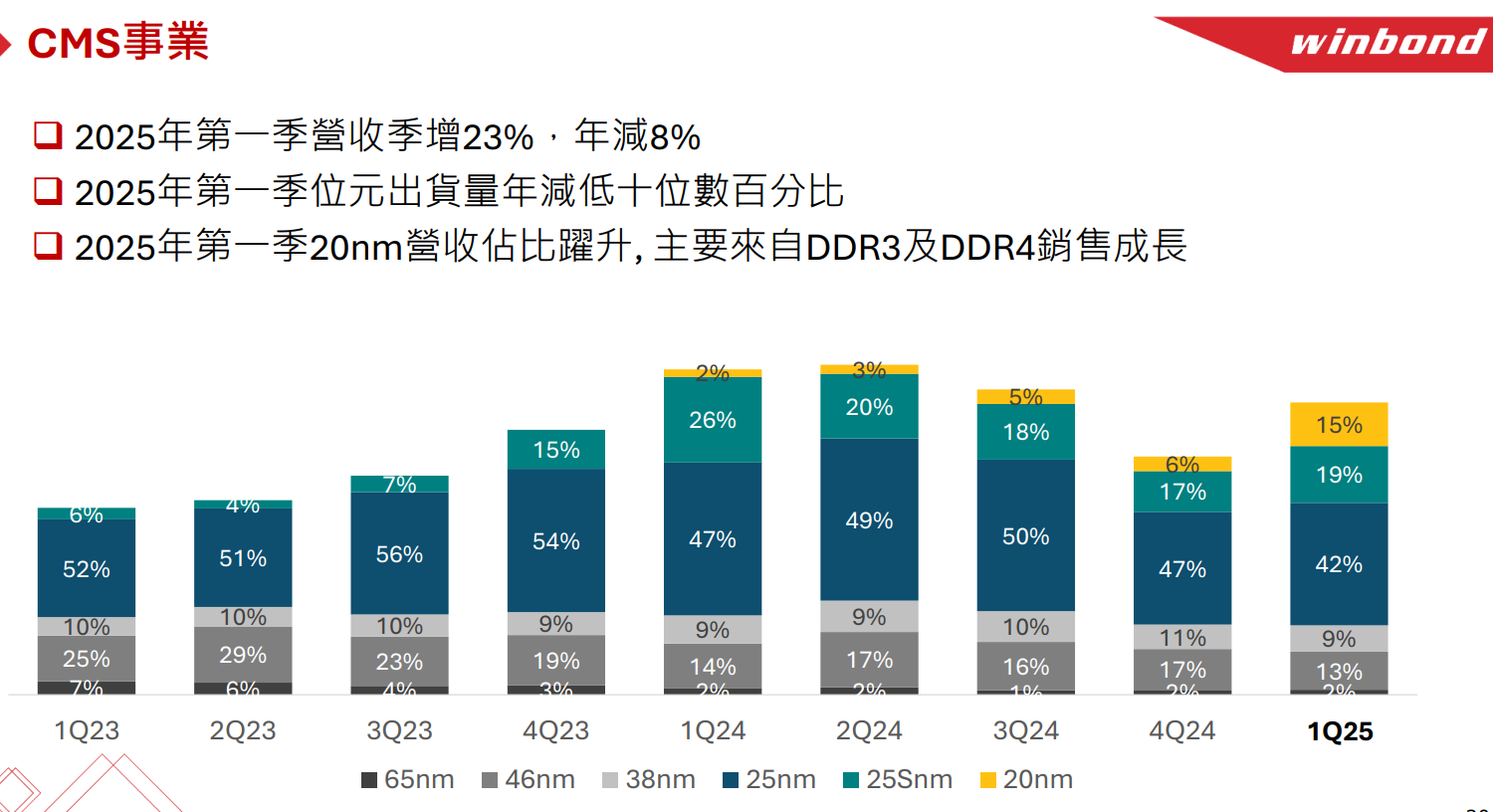

2025 年 12 月 3日,中國蘇州 — 全球半導體存儲解決方案領導廠商華邦電子今日宣布推出全新 8Gb DDR4 DRAM,該產品采用華邦自有先進 16nm 制程技術,提供更高速度、更低

2025-12-03 16:44:28 709

709

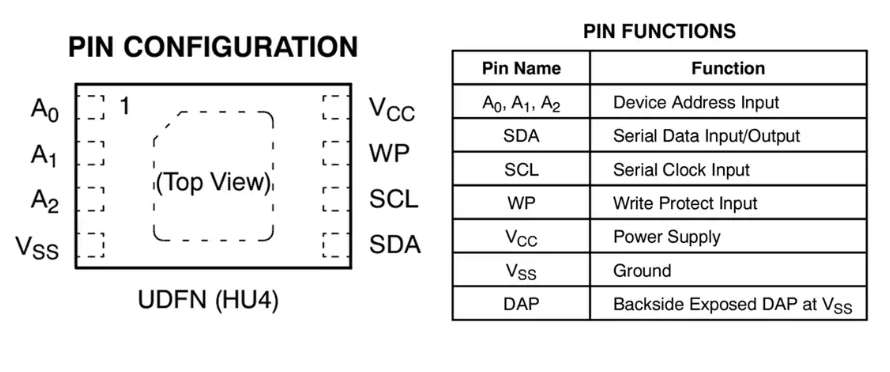

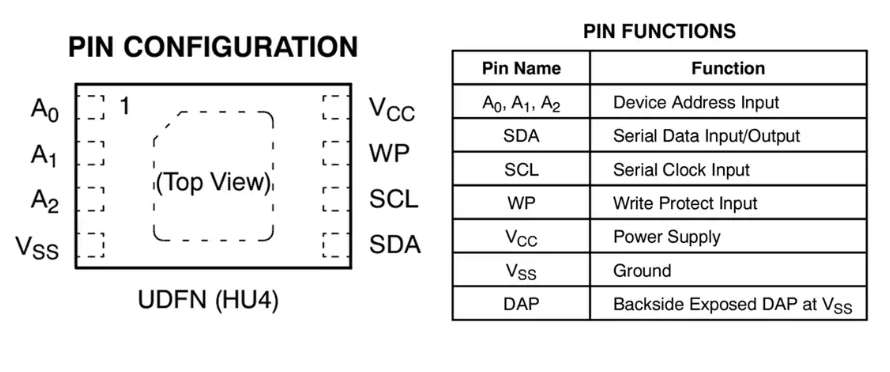

在電子設計領域,對于DDR4 DIMM的設計,EEPROM的選擇至關重要。N34C04作為一款專門為DDR4 DIMM設計的EEPROM Serial 4 - Kb器件,實現了JEDEC

2025-11-27 14:42:12 306

306

本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3467

3467

TPS650061RUKR進行電源設計。電源輸出1.2v,1.8v,3.3v均正常。

由于板子未掛載SDRAM或DDR,將程序的下載地址改為L2RAM(0x11800000)位置也沒辦法正確load,并通過JTAG調試

2025-11-19 19:53:00

(Shinshu University)研究團隊的最新設計中,一個專為 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了僅 11 個 LUT + 2 個 CARRY4 塊,關鍵路徑延遲達到 2.75 ns。這是一次令人印象深刻的工藝優化實踐。

2025-11-17 09:49:40 3274

3274

Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設計。本文深入分析了Aurora、PCI Express和Serial RapidIO這三種在Xilinx系統設計中關鍵的串行通信協議。介紹了它們的特性、優勢和應用場景,以及如何在不同需求下選擇合適的協議。

2025-11-14 15:02:11 2357

2357

下面是HummingBird EV Kit給的版圖,其中DDR3_D0對應的應該是板子上的FPGA的C2引腳:?

不過我在配置MIG的時候,通過讀入ucf文件的方式配置DDR3 SDRAM的引腳

2025-11-06 07:57:09

電子發燒友網站提供《DDR3 SDRAM參考設計手冊.pdf》資料免費下載

2025-11-05 17:04:01 4

4 在有些情況下,我們想要把代碼放到SDRAM運行。下面介紹在APM32的MCU中,如何把代碼重定位到SDRAM運行。對于不同APM32系列的MCU,方法都是一樣的。

2025-11-04 09:14:18 4981

4981

識別。該板卡的PS端支持1組72位DDR4 SDRAM,PL端支持1組32位DDR4 SDRAM,支持1片32GB EMMC存儲單元,支持2片QSPI FLASH

2025-11-03 16:35:26

:

http://www.digilent.com.cn/products/product-nexys-4-ddr-artix-7-fpga-trainer-board.html

NexysVideo

2025-10-31 07:26:13

由于FPGA內部存儲資源有限,很多時候不能滿足需求,因此可以利用DDR對系統進行存儲擴展。由于DDR3內部控制十分復雜,因此可以基于AXI總線,利用Vivado提供的MIG IP對DDR3進行控制

2025-10-29 07:16:34

SD卡和OV5640的數據搬運進DDR中。

Setting

Value

Memory Type

DDR3 SDRAM

Max. clock period

3000ps

Clock ratio

4

2025-10-28 07:24:01

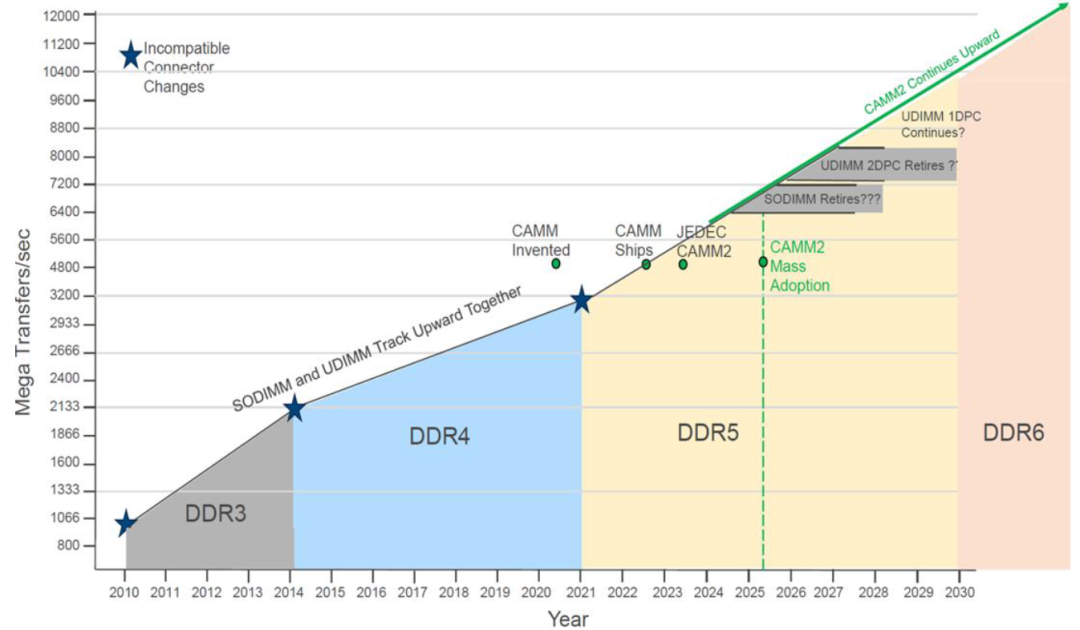

DDR 的比較以及 DDR5 與 LPDDR5 的差異以及 DDR5 的拓撲結構。 什么是 DDR5? 先來看一下什么是 DDR 。 DDR(Double Data Rate)屬于SDRAM

2025-10-27 19:28:16 7360

7360

電子發燒友網綜合報道 “早知道就多囤幾根內存條了!”——這是2025年10月電商促銷季里,無數DIY玩家與渠道商發出的共同感嘆。如今,DDR4 16GB內存價格突破500元,一年內漲幅超兩倍,賺錢

2025-10-22 09:19:37 10310

10310

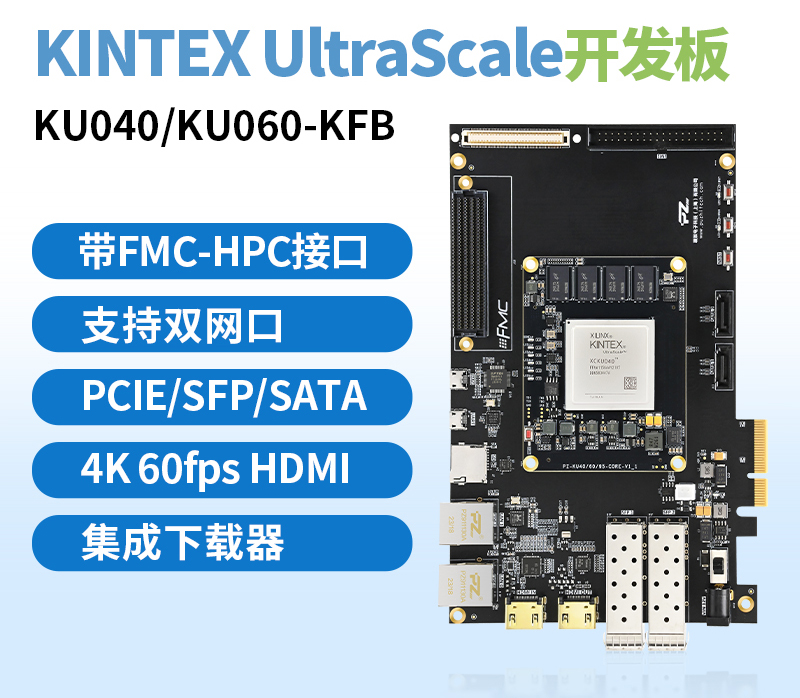

該平臺的PL端具有1個FMC(HPC)接口,1路PCIe x4主機接口,支持1組64位DDR3 SDRAM大容量緩存、支持1路1000BASE-T千兆以太網接口、支持1路3G SDI輸入接口、支持1路3G SDI輸出接口,支持1路HDMI輸入接口、支持1路HDMI輸出接口。

2025-10-21 18:47:47 496

496

DDR控制協議

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源

2025-10-21 14:30:16

蜂鳥DDR200T中DDR3的ip配置案列,提供DDR3引腳配置。具體參數可更具項目實際更改。

這里選用的axi接口

在賽靈思的IP配置中沒有MT41K28M6JT-125K內存的信息,因此選用

2025-10-21 11:19:08

,DDR SDRAM的最大特點是雙邊沿觸發,即在時鐘的上升沿和下降沿都能進行數據采集的發送,同樣的工作時鐘,DDR SDRAM的讀寫速度可以比傳統的SDRAM快一倍。

DDR3讀寫控制器可以在Xilinx

2025-10-21 10:40:28

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源難以實現大量圖像數據

2025-10-21 08:43:39

在 FPGA 中測試 DDR 帶寬時,帶寬無法跑滿是常見問題。下面我將從架構、時序、訪問模式、工具限制等多個維度,系統梳理導致 DDR 帶寬跑不滿的常見原因及分析方法。

2025-10-15 10:17:41 735

735 三星近期已向全球 OEM 客戶發出正式函件,明確旗下 DDR4 模組將于 2025 年底進入產品壽命結束(EOL)階段,最后訂購日期定于 6 月上旬,最后出貨日期則為 12 月 10 日。此次停產

2025-10-14 17:11:37 1033

1033 10月10日,以“碳硅共生 合創AI+時代”為主題的2025中國移動全球合作伙伴大會上,芯盛智能科技(湖南)有限公司攜手中國移動通信集團終端有限公司聯合發布基于1Xnm工藝制程的全國產DDR4內存產品,這一成果彰顯了數字基建自主可控又邁出了關鍵一步,為數字中國建設提供了更安全可靠的硬件支撐。

2025-10-13 14:28:55 1423

1423 回收DDR2,回收DDR3,收購DDR2,收購DDR3 DDR4 DDR5長期現金高價回收DDR,回收三星DDR,回收海力士DDR,回收南亞DDR,回收爾必達DDR,回收美光DDR,回收DDR

2025-10-09 14:15:34

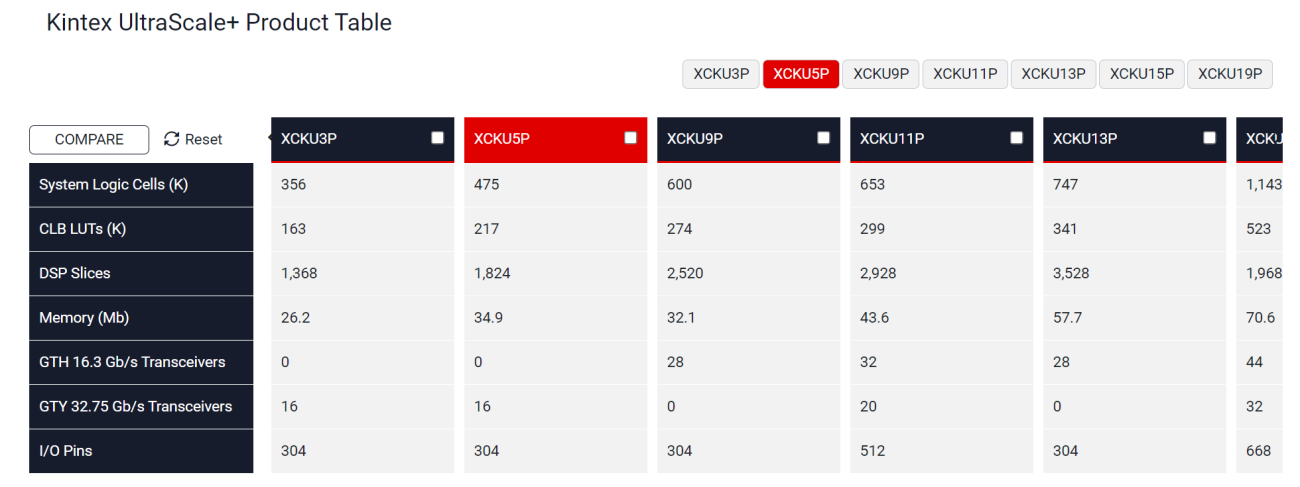

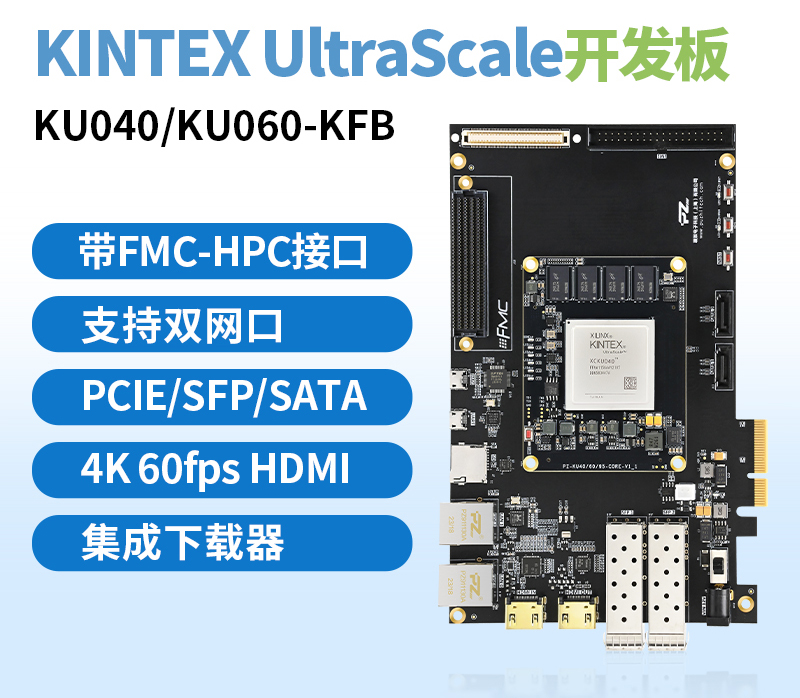

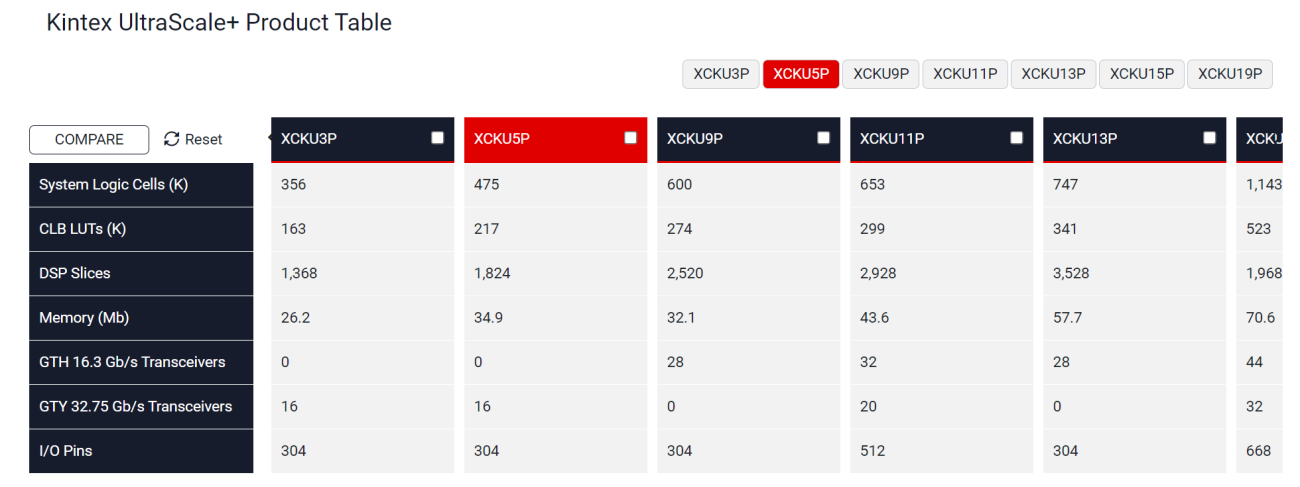

的Kintex UltraScale+開發板采用核心板+底板結構,核心板提供KU3P/KU5P兩種型號,配備2GB DDR4、256Mb QSPI Flash等資源,通過240P高速連接器與底板連接。底板集成了千兆以太網、QSFP28、MIPI、FMC、PCIe等豐富接口,并內置USB-JTAG調試器

2025-09-26 10:46:19 782

782

1組72位DDR4 SDRAM,PL端支持1組32位DDR4 SDRAM,支持1片32GB EMMC存儲單元,支持2片QSPI FLASH用于FPGA的加載,支持

2025-09-15 14:37:00

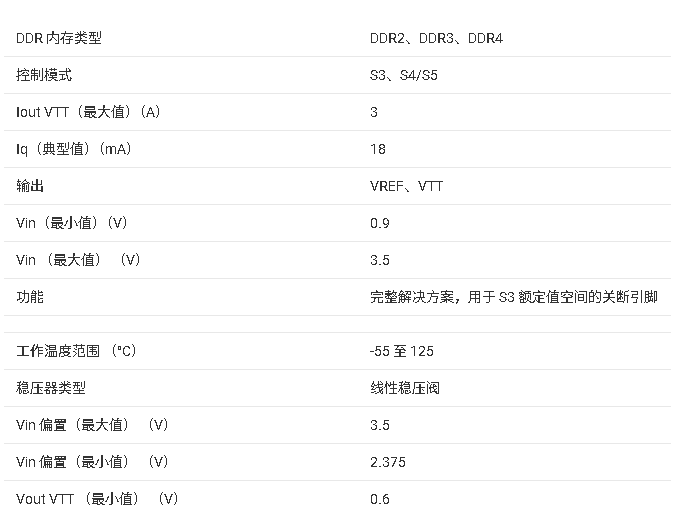

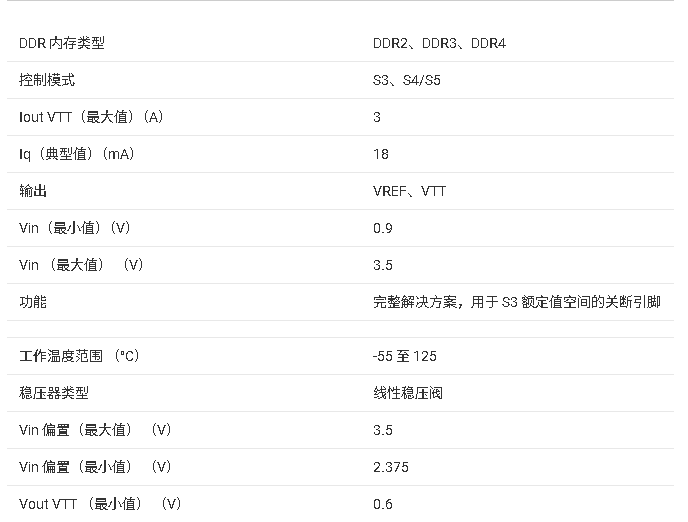

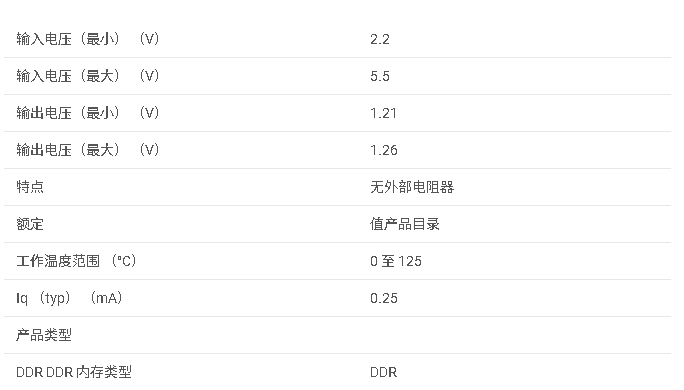

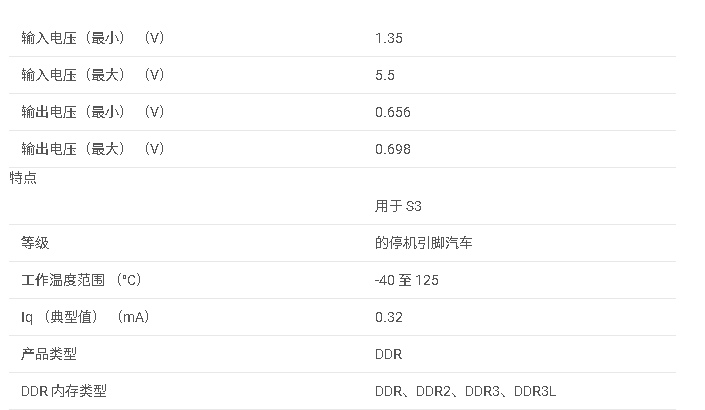

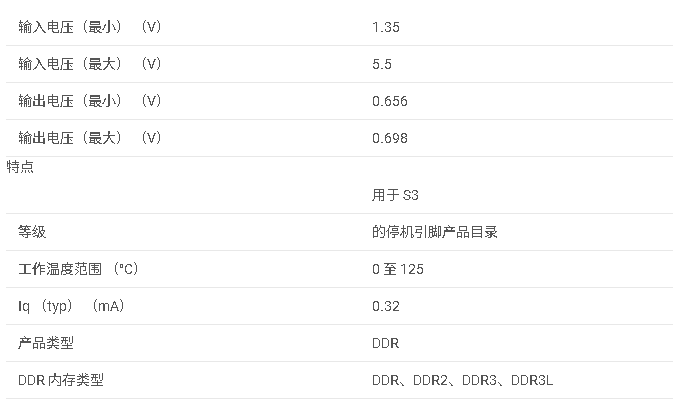

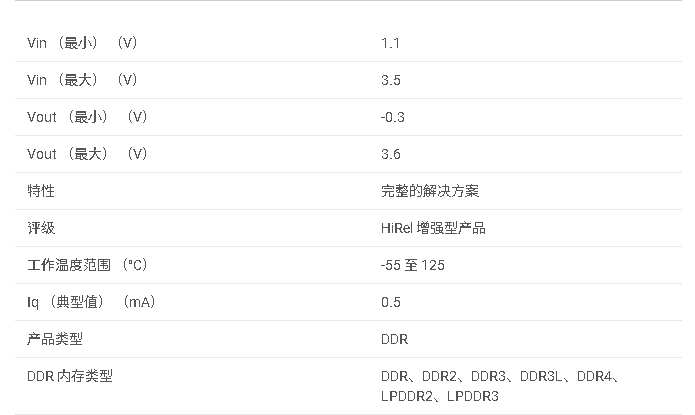

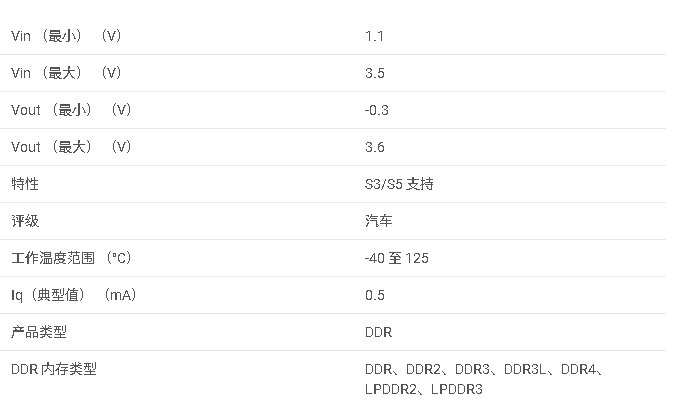

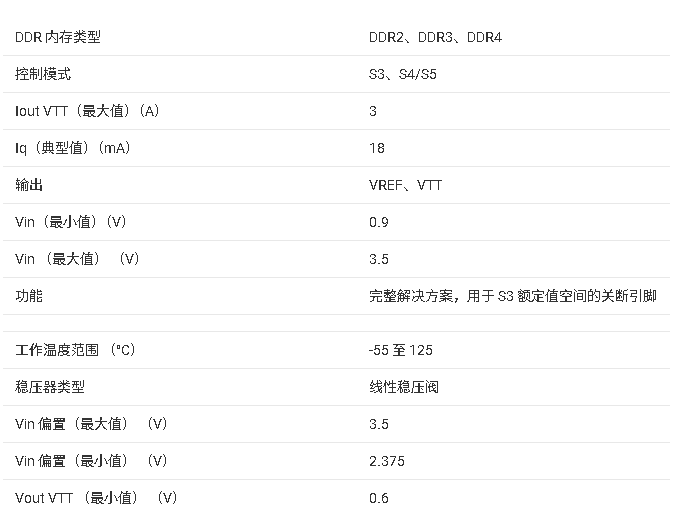

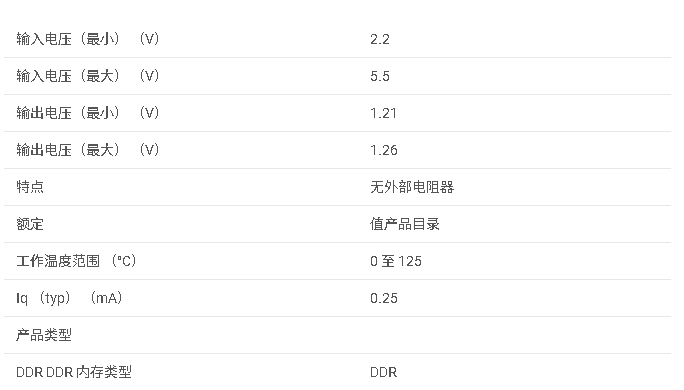

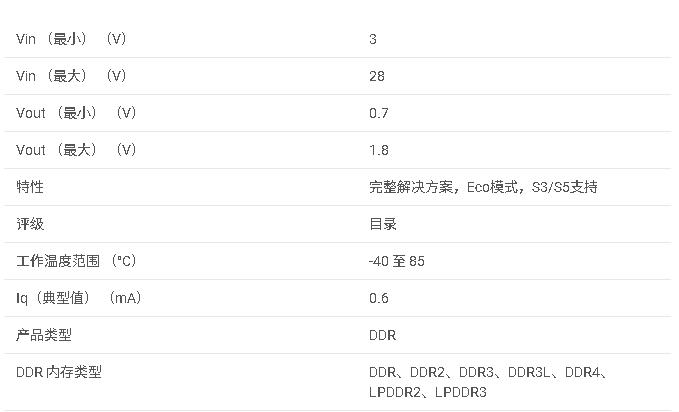

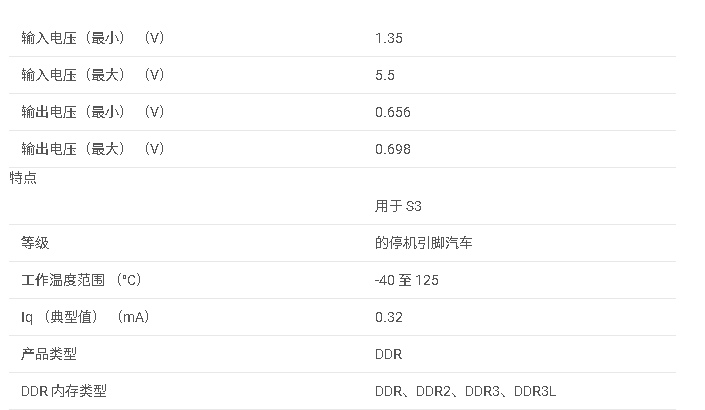

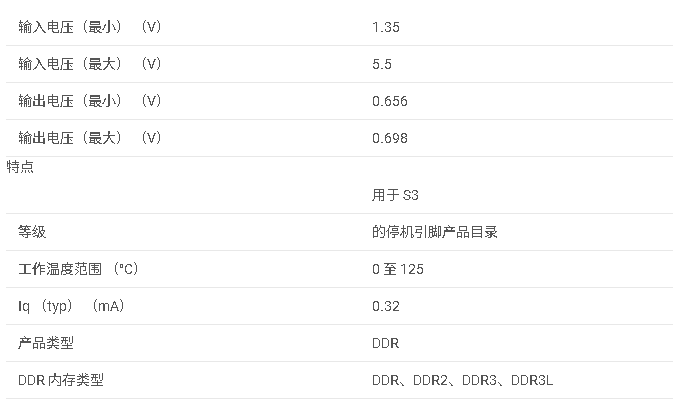

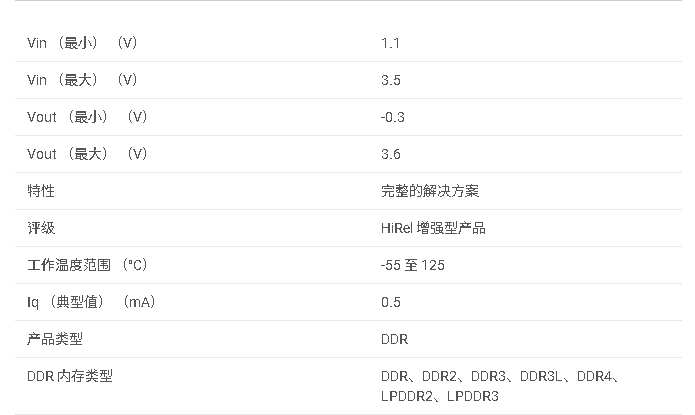

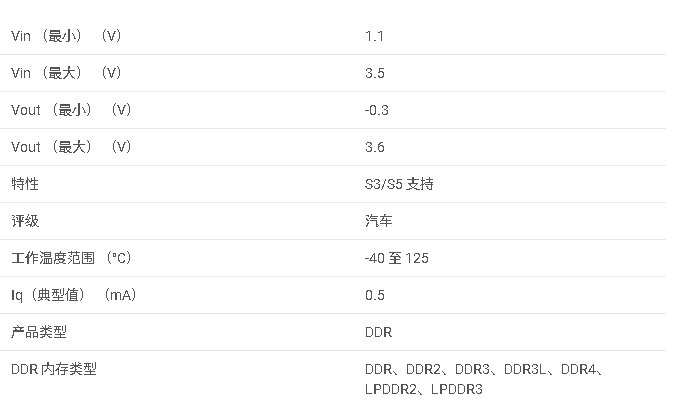

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接應用。TPS7H3301-SP VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源。在

2025-09-09 14:45:15 719

719

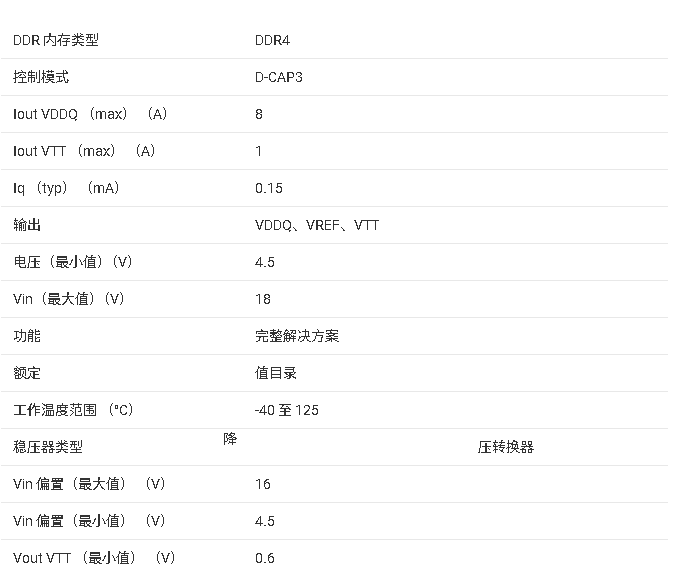

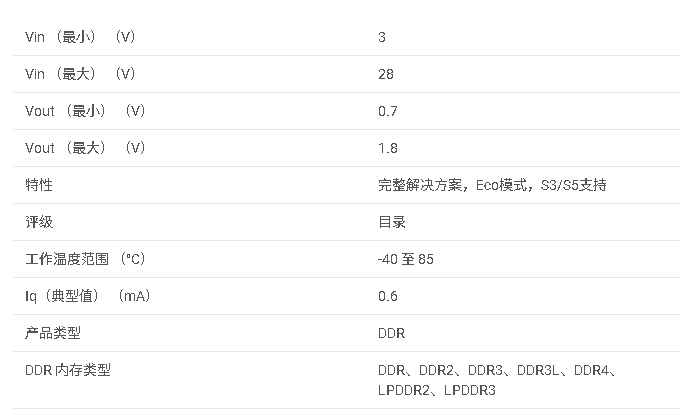

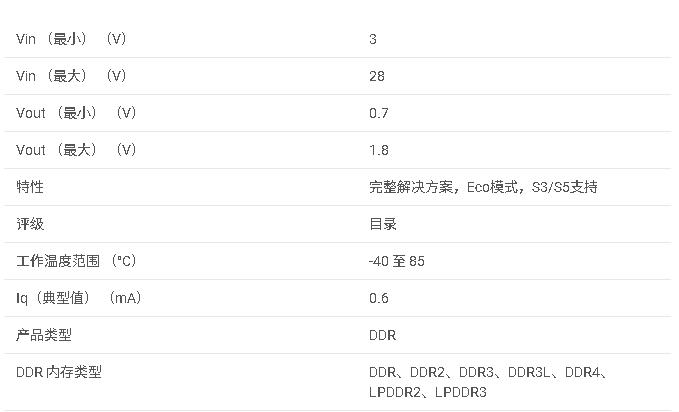

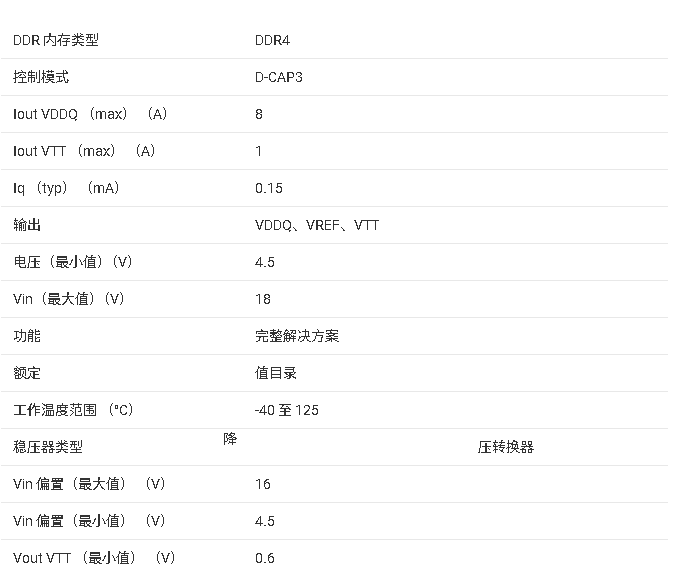

TPS65295器件以最低的總成本和最小的空間為 DDR4 內存系統提供完整的電源解決方案。它符合 DDR4 上電和斷電序列要求的 JEDEC 標準。該TPS65295集成了兩個同步降壓轉換器

2025-09-09 14:16:04 1732

1732

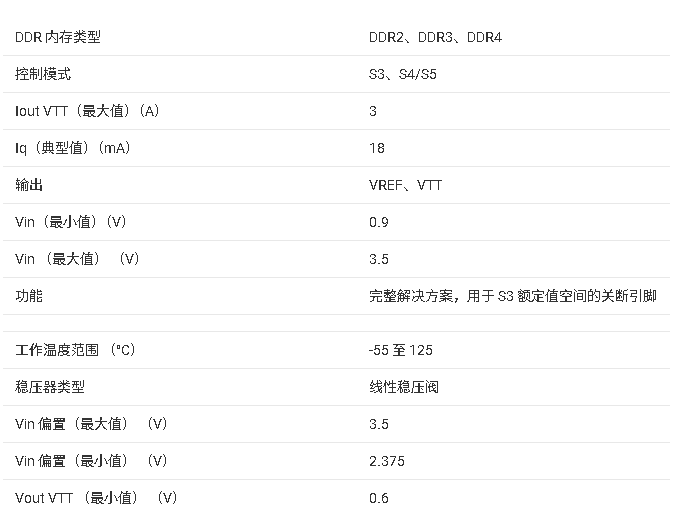

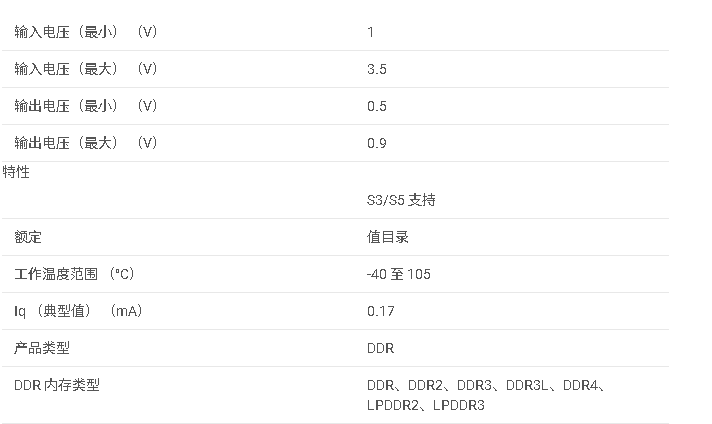

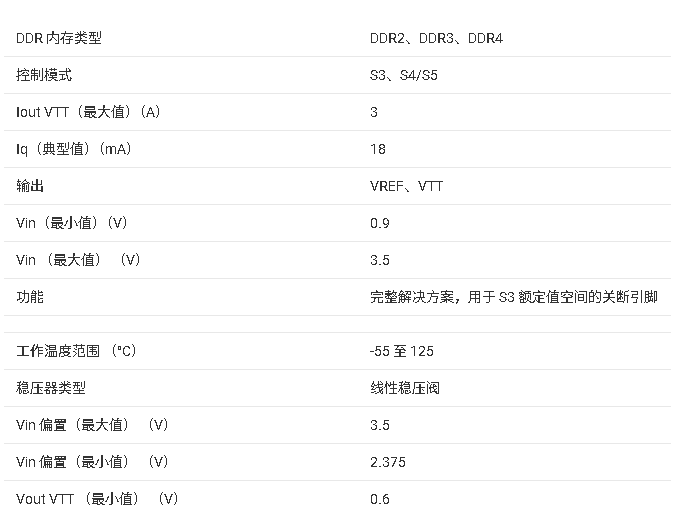

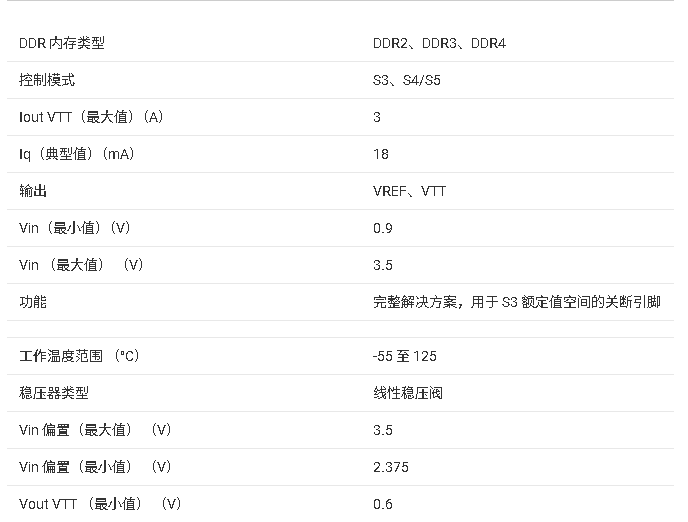

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應用。TPS7H3302 VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源

2025-09-09 13:53:22 688

688

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應用。TPS7H3302 VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源

2025-09-09 13:48:37 756

756

的技術支持和行業化的應用方案,貞光科技正在幫助更多客戶在供應鏈安全與性能需求之間找到平衡。全系列產品覆蓋:從SDR到DDR4紫光國芯在DRAM領域的技術積累超過十年,產品

2025-09-03 16:22:46 1511

1511

本文旨在通過講解不同模式的原理圖連接方式,進而配置用到引腳的含義(手冊上相關引腳含義有四、五頁,通過本文理解基本上能夠記住所有引腳含義以及使用場景),熟悉xilinx 7系列配置流程,以及設計原理圖時需要注意的一些事項,比如flash與FPGA的上電時序。

2025-08-30 14:35:28 9291

9291

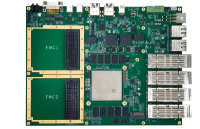

作為主處理器,FPGA 外掛兩組 72 位 DDR4 SDRAM,用來實現超大容量數據緩存,DDR4 的最高數據緩存帶寬可以達到2400MHz,DDR4 的緩存

2025-08-29 15:57:37 398

398

:XCKU115-2FLVF1924I 作為主處理器,FPGA 外掛兩組 72 位 DDR4 SDRAM,用來實現超大容量數據緩存,DDR4 的最高數據緩存帶寬可以達到 2400M

2025-08-29 15:49:41

DDR4SDRAM,用來實現超大容量數據緩存,FPGA的PS端外掛1組72位的DDR4SDRAM的高速數據緩存,用來支持操作系統的運行。該平臺支持2個FMC+接口,每個F

2025-08-29 15:29:49 1292

1292

DDR4 SDRAM,用來實現超大容量數據緩存,FPGA的PS端外掛1組72位的DDR4 SDRAM的高速數據緩存,用來支持操作系統的運行。該平臺支持2個FMC+接口,

2025-08-29 15:28:59

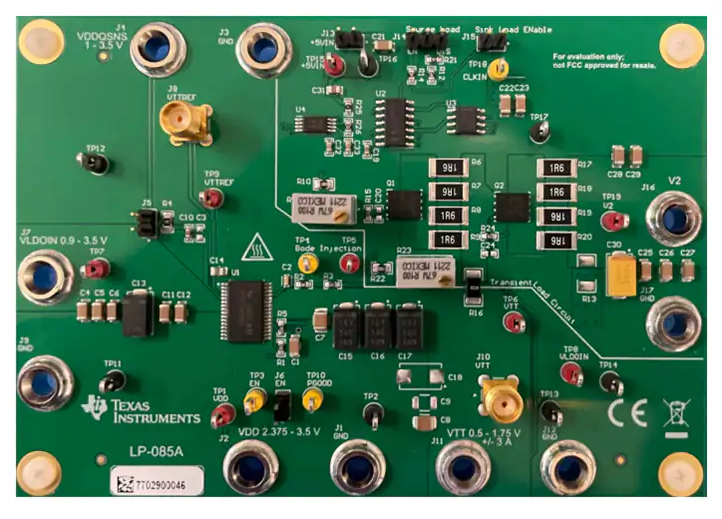

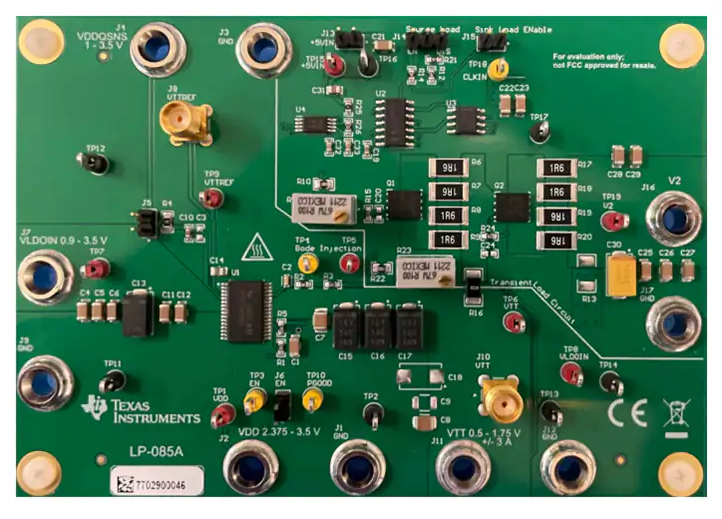

3A,支持測試DDR、DDR2、 DDR3、DDR3L和DDR4。該評估模塊配有方便的測試點和跳線,用于評估TPS7H3302-SEP DDR端子。TPS7H3302EVM評估模塊非常適合用于抗輻射DDR電源應用以及用于DDR、DDR2、DDR3和DDR4的存儲器終端穩壓器。

2025-08-27 16:14:21 831

831

璞致電子PZ-KU060-KFB開發板采用Xilinx Kintex UltraScale KU060芯片,提供高密度并行計算能力,配備4GB DDR4內存、20對GTH高速收發器和多種擴展接口

2025-08-18 13:28:10 581

581

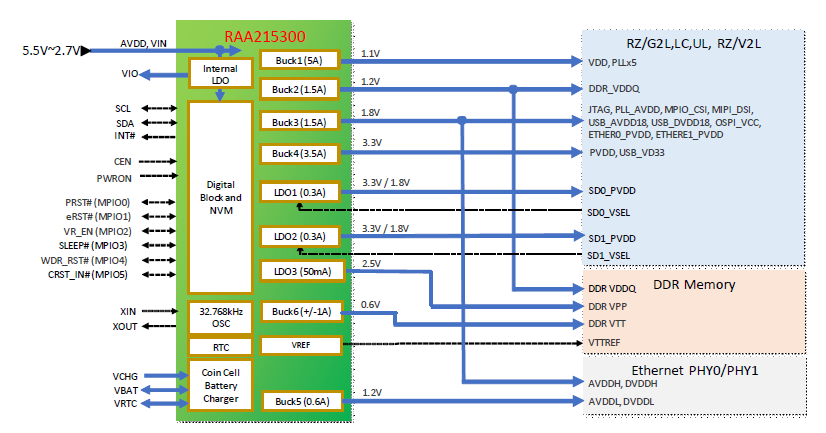

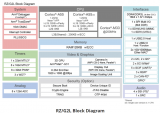

RZ/G2L微處理器配備Cortex-A55(1.2GHz)CPU、16位DDR3L/DDR4接口、帶Arm Mali-G31的3D圖形加速引擎以及視頻編解碼器(H.264)。此外,這款微處理器還

2025-08-04 13:40:03 3085

3085

關于 AMD/Xilinx 7系列FPGA存儲器接口解決方案(UG586) 的用戶指南,其主要內容和技術要點可概括如下:1. 文檔定位與核心內容定位:該文檔是7系列FPGA中存儲接口控制器的官方

2025-07-28 16:17:45 3

3 超高速信號處理與光通信。其核心特性包括:16GB DDR4存儲、PCIe3.0x8高速接口以及豐富的開發工具鏈支持。該產品適用于100G光通信、多通道雷達處理、超高速數據采集等尖端場景,為科研與工業應用提供高性能解決方案。璞致電子憑借十余年FPGA領域經驗,致力于為全球客戶提供可靠信號處理方案。

2025-07-24 09:05:19 773

773

及747K邏輯單元FPGA,形成"通用計算+實時控制+定制加速"架構。產品具備8GB DDR4/64GB eMMC存儲、8×16.3Gb/s高速接口,支持-40~85℃寬溫工作,適用于機器視覺、工業控制、醫療設備等領域。

2025-07-22 09:47:56 835

835

方式比較靈活,采用軟核實現 DDR memory 的控制,有如下特點:

支持 DDR3

支持 x8、x16 Memory Device

最大位寬支持 32 bit

支持精簡的 AXI4 總線協議

一個

2025-07-10 10:46:48

DRAM內存市場“代際交接”關鍵時刻2025年PC及服務器市場中,DDR4的滲透率約為20%-30%,而DDR5的滲透率約為70%-80%(TrendForce集邦咨詢)。在AI算力爆發和先進

2025-07-09 11:11:24 1702

1702

北京貞光科技有限公司作為紫光國芯的核心代理商,貞光科技在車規級存儲和工業控制領域深耕多年,憑借專業的技術服務能力為汽車電子、ADAS系統等高可靠性應用提供穩定供應保障。近期DDR4內存價格出現大幅

2025-06-27 09:45:11 4125

4125

,近期同樣規格的16Gb產品中,DDR4 16Gb(1GX16)與DDR5 16G(2Gx8)的價格差距已達到1倍。 ? CFM閃存市場表示,去年三

2025-06-27 00:27:00 4539

4539 DDR內存占據主導地位。全球DDR內存市場正經歷一場前所未有的價格風暴。由于原廠加速退出DDR3/DDR4市場,轉向DDR5和HBM(高帶寬內存)生產,DDR3和DDR4市場呈現供不應求、供需失衡、漲勢延續的局面。未來,DDR5滲透率將呈現快速提升,市場份額增長的趨勢。

2025-06-25 11:21:15 2010

2010

隨著計算密集型任務的日益增長,DDR4內存的性能瓶頸已逐步顯現。DDR5的出現雖解燃眉之急,但真正推動內存發揮極致性能的背后“功臣”——正是 DDR5 SPD(Serial Presence Detect)芯片。

2025-06-11 10:07:30 1913

1913

電子發燒友網站提供《XILINX XCZU67DR FPGA完整原理圖.pdf》資料免費下載

2025-05-30 15:29:38 4

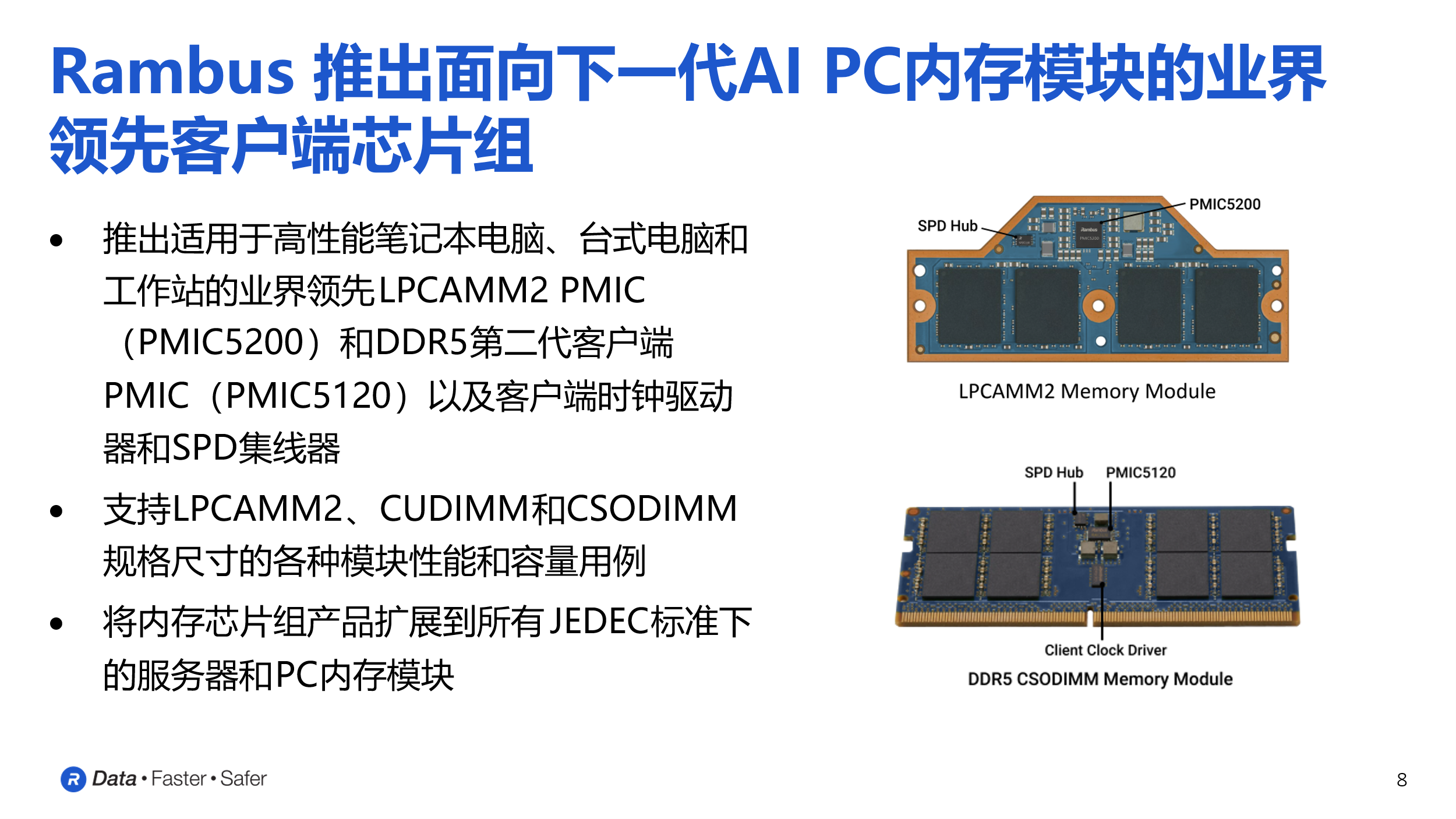

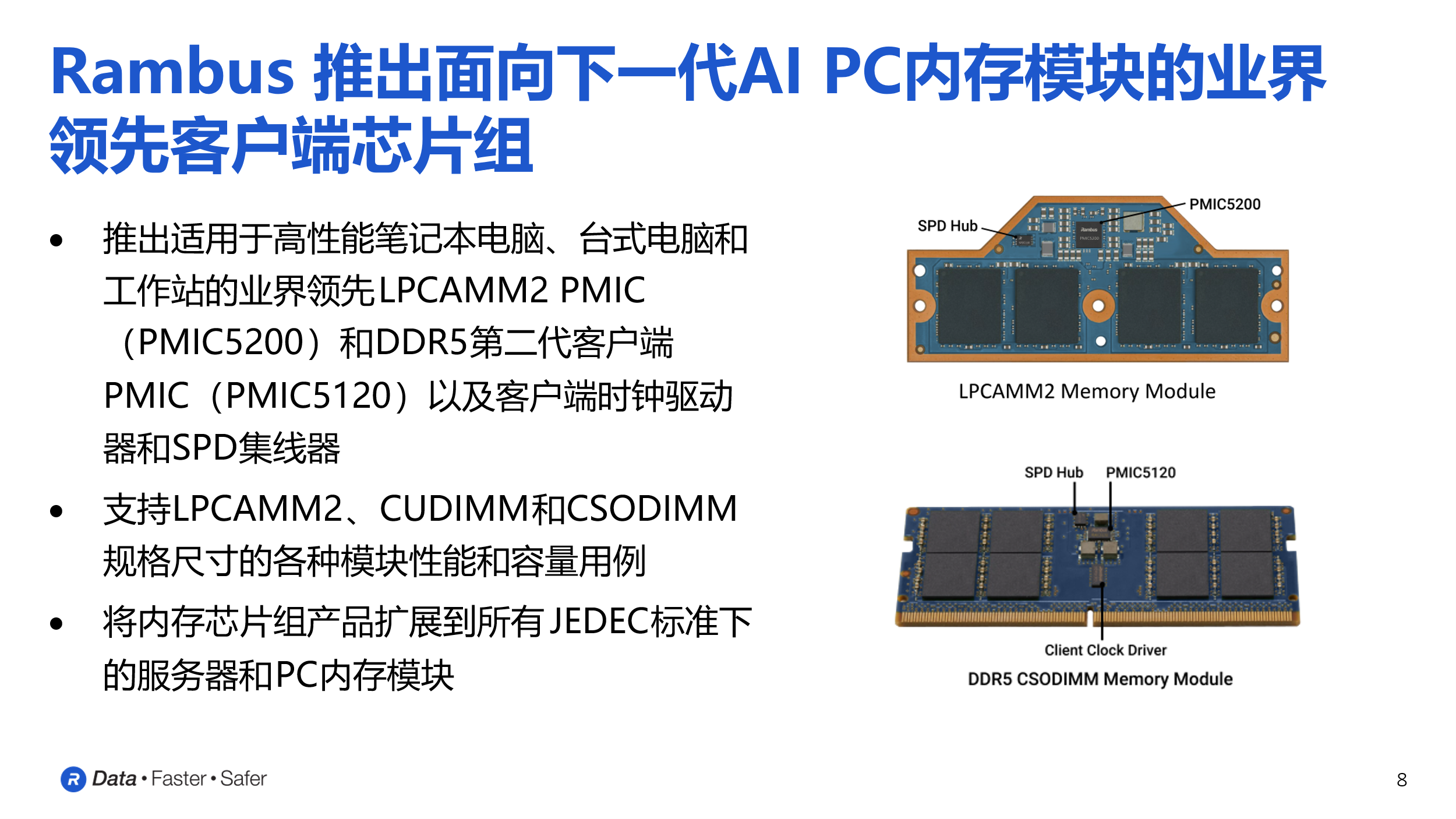

4 PC處理器對DDR5的支持,DDR5內存將更快滲透普及。相較于DDR4,所有電壓由主板供給,DDR5中內存模組搭載PMIC,PMIC是實現高效供電的關鍵,能夠為先進的計算應用提供突破性的性能表現。Rambus最近推出面向下一代AI PC內存模塊的完整客戶端芯片組,包含兩款用于客戶端計算的全新電源

2025-05-29 09:11:20 8127

8127

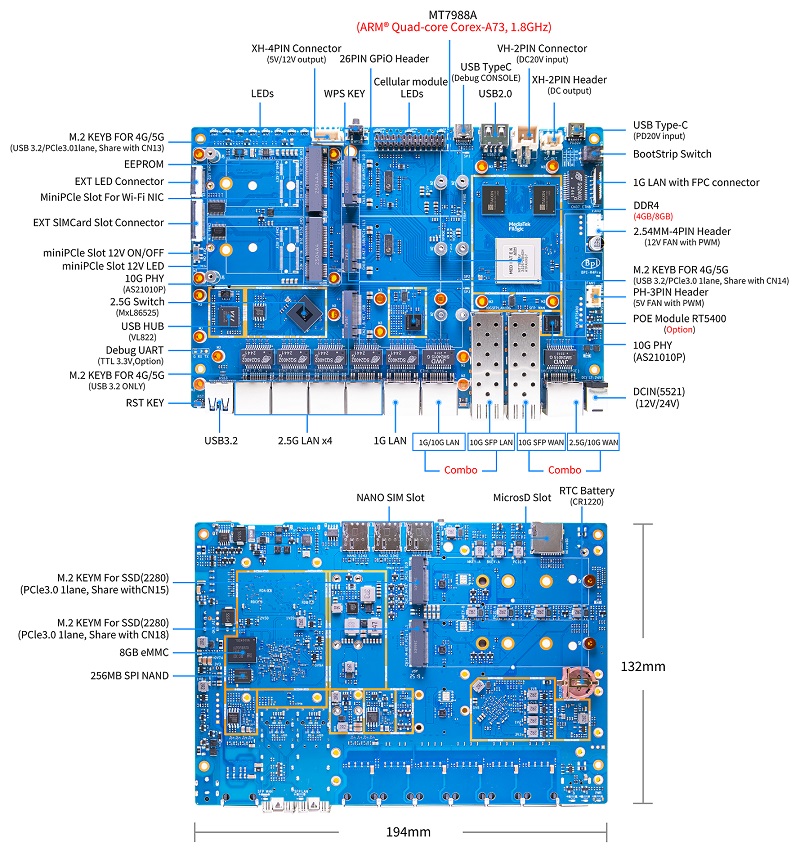

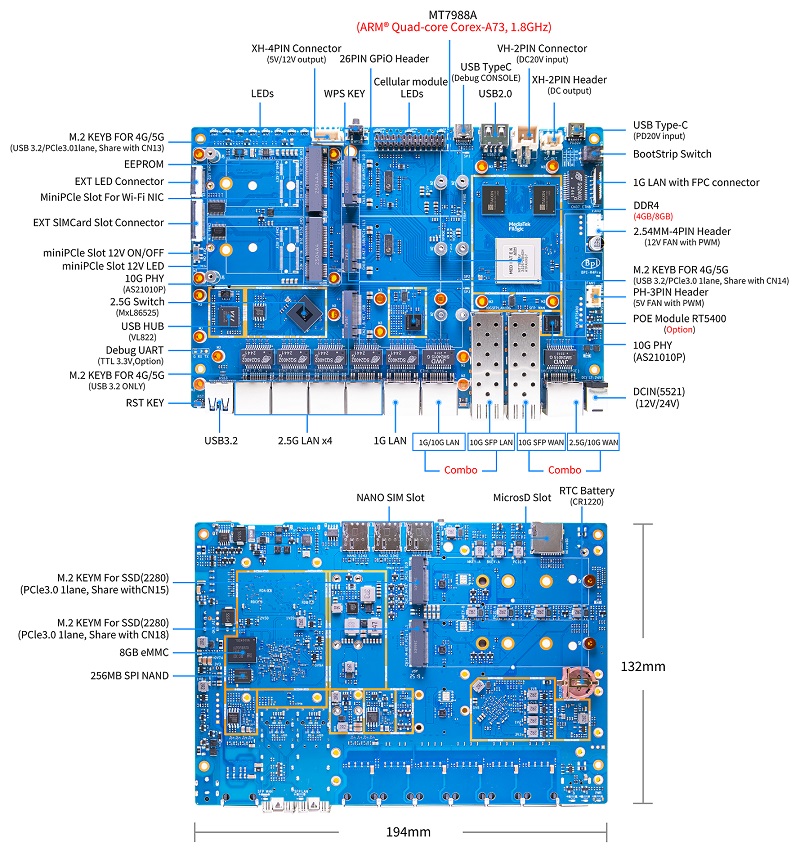

Banana Pi BPI-R4 Pro 路由器板采用聯發科 MT7988A(Filogic 880)四核 ARM Corex-A73 設計,板載 4GB/8GB DDR4 RAM、8GB eMMC

2025-05-28 16:33:08 1793

1793

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個 LogiCORE IP 核,用于在 FPGA 中實現高效的移位寄存器(Shift Register)。該 IP 核利用

2025-05-14 09:36:22 912

912 給大家帶來一些業界資訊: 三星DDR4內存漲價20%? 存儲器價格跌勢結束,在2025年一季度和第二季度,價格開始企穩反彈。 據TrendForce報道稱,三星公司DDR4內存開始漲價,在本月

2025-05-13 15:20:11 1205

1205 最新消息,三星電子本月初與主要客戶就提高DRAM芯片售價達成一致。DDR4 DRAM價格平均上漲兩位數百分比;DDR5價格上漲個位數百分比。據稱 DDR4 上調 20%,DDR5 上調約 5

2025-05-13 01:09:00 6843

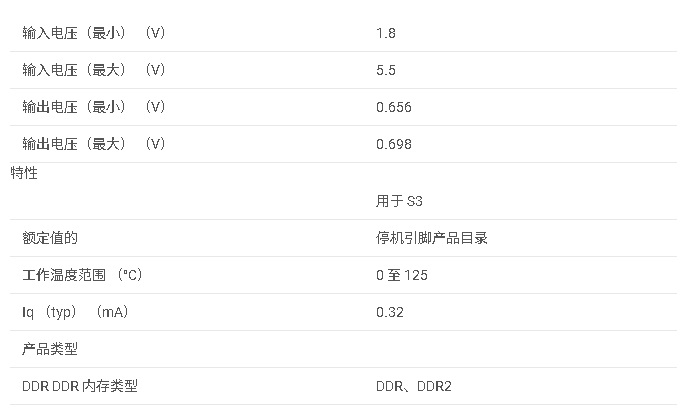

6843 LP2995 線性穩壓器旨在滿足 JEDEC SSTL-2 和 SSTL-3 標準 DDR-SDRAM 終止規范。該器件包含一個高速運算放大器 對負載瞬變提供出色的響應。輸出級可防止擊穿,同時

2025-05-06 09:33:38 715

715

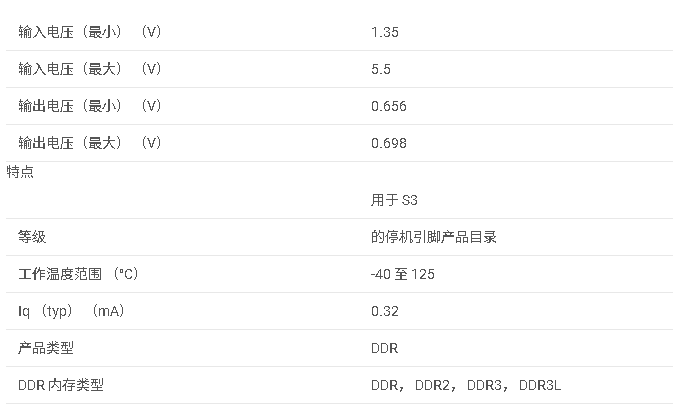

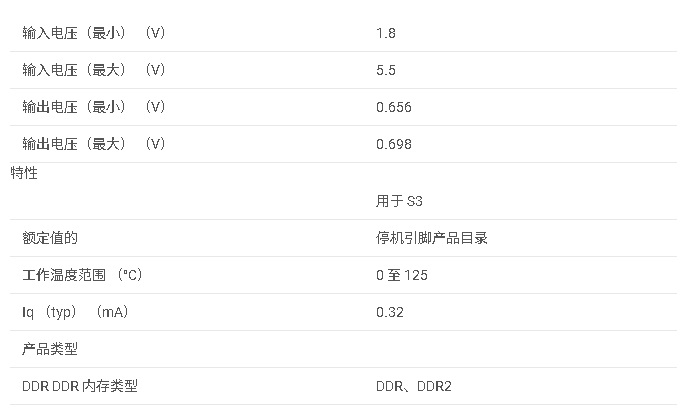

LP2996-N 和 LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 標準 DDR-SDRAM 終止規范。該器件還支持 DDR2,而 LP2996A 支持 DDR3 和 DDR

2025-04-29 18:11:05 834

834

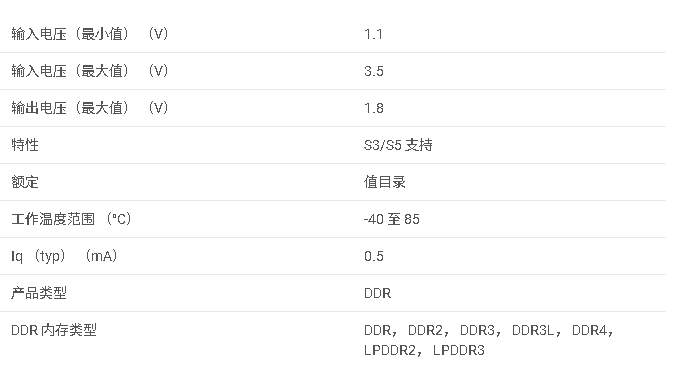

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 內存系統提供完整的電源。它將同步降壓控制器與 3A 灌電流/拉

2025-04-29 16:38:02 1031

1031

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

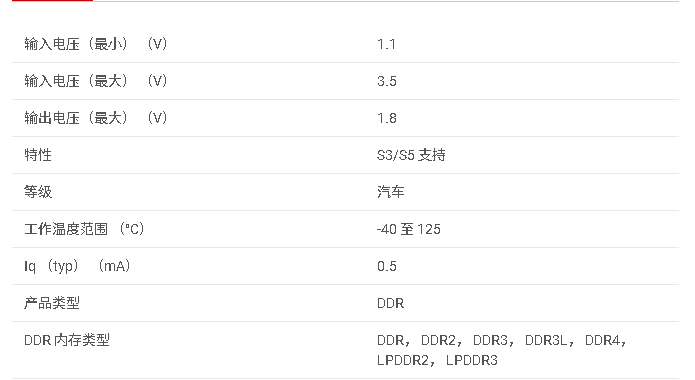

僅為 20 μF。該TPS51200支持遠程感應功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-29 09:59:25 1345

1345

只需要 20 μF 的最小輸出電容。TPS51200-Q1 器件支持遠程感應功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-28 16:21:07 852

852

TPS51916 器件以最低的總成本和最小的空間為 DDR2、DDR3、DDR3L 和 DDR4 內存系統提供完整的電源。它集成了同步降壓穩壓控制器 (VDDQ),具有 2A 灌電流和 2A 源跟蹤 LDO (VTT) 和緩沖低噪聲基準 (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬態響應,并且只需要 1 × 10μF 的陶瓷輸出電容。該器件支持遠程感應功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 總線的所有電源要求。VTT 電流

2025-04-28 10:04:48 685

685

TPS51716為 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的電源 以最低的總成本和最小空間實現內存系統。它集成了一個同步降壓 具有 2A 灌電流/拉電流跟蹤 LDO

2025-04-27 11:36:05 763

763

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

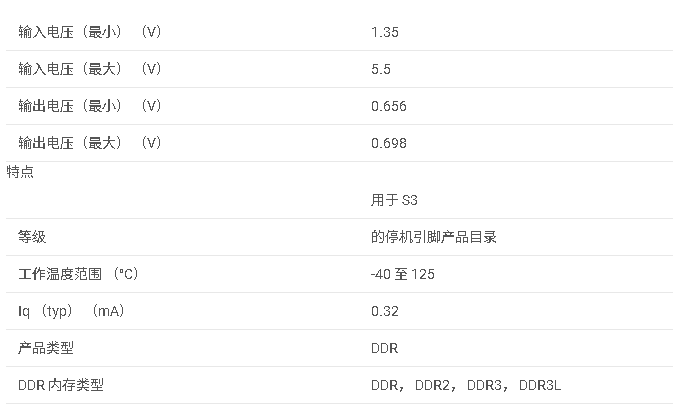

LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 規范 DDR-SDRAM 終止。該器件還支持 DDR2、DDR3 和 DDR3L VTT 總線端接,帶 V~DDQ~最小為 1.35V

2025-04-26 15:02:50 746

746

只需要最小輸出 電容為 20 μF。TPS51200-EP 支持遙感功能和所有功率要求 用于 DDR、DDR2、DDR3、低功耗 DDR3 和 DDR4 VTT 總線終端。

2025-04-26 10:26:35 1335

1335

的最小輸出電容。該器件支持遠程感應功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-25 10:07:15 1053

1053

位流驗證,對于芯片研發是一個非常重要的測試手段,對于純軟件開發人員,最難理解的就是位流驗證。在FPGA芯片研發中,位流驗證是在做什么,在哪些階段需要做位流驗證,如何做?都是問題。

2025-04-25 09:42:51 2202

2202

推動電腦邁入新一輪升級周期。相比服役多年的DDR4,DDR5不僅帶來更快的速度,還能提升游戲幀率、加快視頻渲染效率,甚至延長設備續航時間。(主板上的內存插槽位置)問

2025-04-18 10:34:13 71

71

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

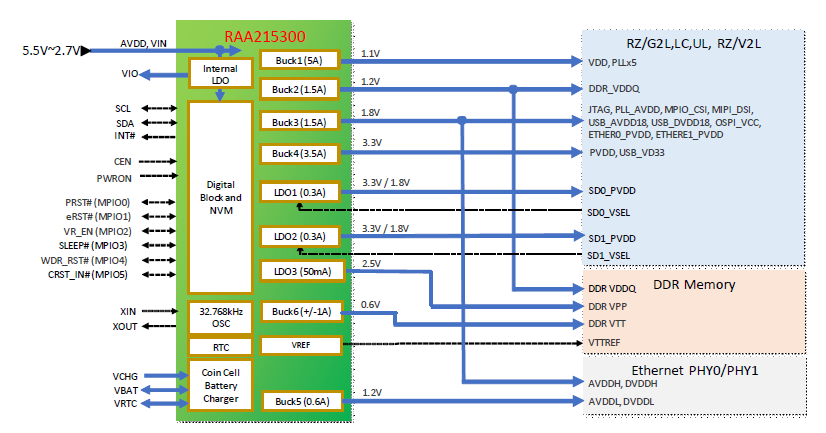

RAA215300 是一款高性能、低成本的 9 通道 PMIC,專為 32 位和 64 位 MCU 和 MPU 應用而設計。 該 PMIC 支持DDR3、DDR3L、DDR4 和 LPDDR4 內存

2025-04-09 15:31:25 657

657

的DAC; ?● ?支持外部時鐘輸入1路, 外觸發,外同步各1路; ?● ?PL 1組64 bit 2400M DDR4,支持PL部分高速存儲和處理。 單組4GB字節容量,PL部分8GB字節容量。 ?● ?支

2025-04-08 10:34:02 1023

1023

注意:DDR PMU 固件 vision-0x1001 (vA-2019.04)

注意:DDR4 UDIMM,帶 2 位 64 位總線 (x8)

注意:32 GB DDR4,64 位,CL=22,ECC

2025-04-04 08:17:54

RT1176 與 DDR SDRAM 兼容嗎?

2025-04-04 06:09:26

具有閃存 以及一個串行接口,以支持可配置性、監控和管理。

支持多種電壓識別 (VID) 模式,包括 4 位并行 接口、一個 6 位接口和一個 8 位串行接口。

2025-03-25 17:18:55 785

785

,UCD9244 具有閃存和串行接口,以支持可配置性、監控和管理。

支持多種電壓識別 (VID) 模式,包括 4 位并行接口、6 位接口和 8 位串行接口。

2025-03-25 15:20:12 726

726

3, DDR3L, DDR4和LPDDR3, LPDDR4協議,數據傳輸速率最高可達2667Mbps,并支持X16/X32/X64等多種數據位寬應用。

2025-03-21 16:20:03 984

984 DDR內存控制器是一個高度集成的組件,支持多種DDR內存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設計的架構來優化內存訪問效率。

2025-03-05 13:47:40 3573

3573

前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

為了加深讀者對 FPGA 端控制架構的印象,在數據讀取的控制部分,首先我們可以將SDRAM 想作是一個自來水廠,清水得先送至用戶樓上的水塔中存放,在家里轉開水龍頭要用水時,才能及時供應,相同

2025-02-26 15:27:09 1813

1813

電子發燒友網綜合報道,日前,日媒報道由于DRAM內存芯片價格持續下滑,全球三大原廠三星、SK海力士和美光計劃在2025年停產DDR4內存芯片。 ? 數據顯示,2025年1月,DDR4 8Gb顆粒

2025-02-21 00:10:00 2806

2806 ,DDR5內存已成為市場主流,并逐步取代DDR4內存。值得注意的是,消費級平臺已不再支持DDR4,這使得DDR4內存開始加速向DDR3目前所占據的利基市場轉移。 若三大內存原廠真的決定停產DDR3和DDR4,這無疑將對內存市場產生深遠影響。一方面,這將促使現有DDR3和DDR4內存庫存

2025-02-19 11:11:51 3465

3465

在查閱了論壇中的相關帖子后,發現為了達到該DMD允許的最大投影幀率,需要:

在硬件上需要使用Xilinx Platform cable將FPGA代碼燒錄到該EVM的APPSFPGA中,同時需要

2025-02-19 07:04:51

UltraScale+ XCVU13P(16nm工藝)FPGA 芯片,但從原先最大支持 16G DDR4 SODIMM 內存條插槽升級為最大支持 32G ,并且支持多達 4 個 FMC+ 擴展接口,接入

2025-02-13 17:56:44 1020

1020

;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM內存模塊,專為滿足現代計算需求而設計。該產品以其高帶寬和低功耗的特性,廣泛應用于個人電腦、服務器和嵌入式系統中,成為市場上備

2025-02-10 20:10:39

如需了解價格貨期等具體信息,歡迎在首頁找到聯系方式鏈接我。不要留言,留言會被吞,收不到留言。 8GB DDR4 ECC UDIMM 產品概述 8GB DDR4 ECC UDIMM

2025-02-10 20:07:47

如需了解價格貨期等具體信息,歡迎在首頁找到聯系方式鏈接我。不要留言,留言會被吞,收不到留言。 16GB DDR4 ECC UDIMM 產品概述 16GB DDR4 ECC

2025-02-10 20:05:15

M471A2G43AB2-CWE 是一款高性能的 DDR4 SO-DIMM 內存模塊,具有 16GB 的容量,專為滿足現代移動計算需求而設計。這款內存條采用了 Samsung 的先進技術,適用于各種

2025-02-10 07:49:49

M471A1G44CB0-CWE 是一款高性能的 DDR4 SO-DIMM 內存模塊,具有 8GB 的容量,專為滿足現代移動計算需求而設計。這款內存條采用了 Samsung 的先進技術,適用于各類

2025-02-10 07:48:41

更高的帶寬和更低的功耗,適用于各種筆記本電腦和小型計算設備。產品技術資料型號:M425R1GB4PB0-CWM內存類型:DDR5 SDRAM容量:8GB工作頻率:5

2025-02-10 07:47:57

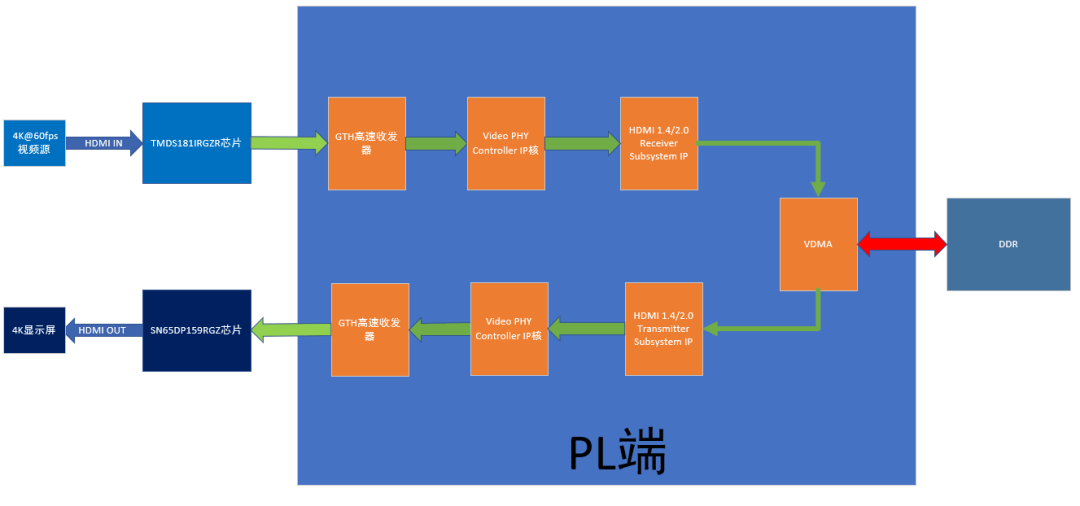

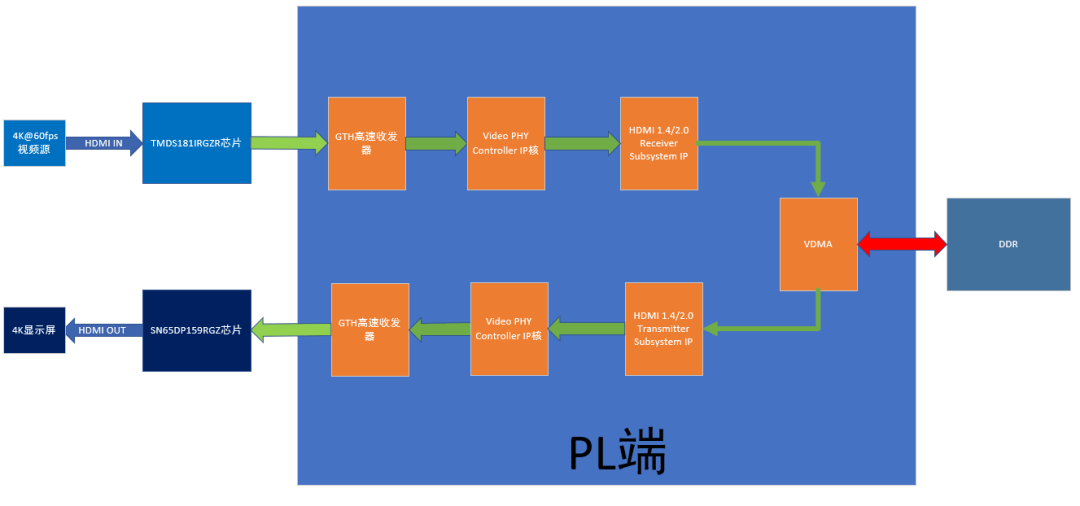

執行信號的解串操作(串轉并),并解碼出視頻流數據,隨后通過VDMA IP緩存至DDR中,利用Xilinx官方的IP對視頻流數據進行重新編碼

2025-01-24 10:27:05 979

979

xilinx FPGA IOB約束使用以及注意事項 一、什么是IOB約束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距離IO最近的寄存器,同時位置固定。當你輸入或者輸出

2025-01-16 11:02:01 1655

1655

AMD Versal 自適應 SoC 器件上 DDR4 硬核控制器 DDRMC 跑仿真時,按照 IP 的默認設置,在 IP wizard 中使能了“Internal Responder”,就可以

2025-01-10 13:33:34 1481

1481

硬件:

一Xilinx XC7A100T FPGA開發板

二12V電源適配器

三下載器

四 win10筆記本

軟件:

一Vivado (指導手冊有詳細的安裝下載流程)

二官方按鍵示例工程

按鍵示例

2025-01-09 16:08:51

電子發燒友App

電子發燒友App

評論