“本文將詳細介紹 DDR5、LPDDR5 的技術細節以及 Layout 的規范要求。然后比較 CAMM2 模組與 SODIMM 的差別。”

本文將介紹什么是 DDR5,DDR5 和之前 DDR 的比較以及 DDR5 與 LPDDR5 的差異以及 DDR5 的拓撲結構。什么是 DDR5?先來看一下什么是 DDR。DDR(Double Data Rate)屬于SDRAM(Synchronous Dynamic Random Access Memory)的一種。DDR 的主要特點是數據傳輸速率更高。DDR 內存采用了一種稱為“雙倍數據速率”的技術,它可以在一個時鐘周期內傳輸兩次數據,即在時鐘信號的上升沿和下降沿都能進行數據傳輸。而普通的 SDRAM 在一個時鐘周期內只能在上升沿或者下降沿傳輸一次數據。

DDR5 是第五代 DDR 技術,核心技術參數如下:

-

發布年份:2020

-

數據速率:4800-6400 MT/s (未來有潛力達到更高速度)

-

帶寬:38.4-51.2 GB/s

-

電壓:1.1V (更低功耗)

-

密度:每顆 IC 高達 64 Gb

-

通道配置:每 DIMM 雙通道 (有效將可用通道數加倍)

-

預取緩沖區:16n (DDR4 的兩倍)

-

延遲:低于 DDR4

-

提升的通道效率:雙通道帶來更高效的數據傳輸

-

更佳的電源管理:芯片內置 ECC (錯誤修正碼) 提升可靠性與性能

-

改善的信號完整性:新功能如決策反饋均衡 (DFE)

總結一下 DDR5 的特點:

-

速度與帶寬:DDR5 提供比 DDR4 高出許多的數據速率與帶寬。

-

電源效率:DDR5 運作電壓更低,從而降低功耗。

-

密度與容量:DDR5 支持更高密度,允許更大的內存容量。

-

通道配置:DDR5 的每 DIMM 雙通道設計提升了通道效率。

-

先進功能:DDR5 包含芯片內置 ECC 和改善的信號完整性機制等先進功能。

LPDDR5(Low Power Double Data Rate 5)是一種專門為移動設備和功耗敏感型設備(如智能手機、平板電腦、輕薄本)設計的內存標準。

它的核心特性是“低功耗”。它通過使用更低的工作電壓(例如 1.05V 核心電壓和 0.5V I/O 電壓)和更先進的電源管理功能,來實現極高的能效,從而最大限度地延長設備的電池續航時間。

雖然兩者都是“DDR5”家族的成員,但它們在設計理念、物理形態和性能側重上有根本的不同。

| 特性 | LPDDR5 (Low Power DDR5) | DDR5 (Standard DDR5) |

| 主要應用 | 智能手機、平板電腦、輕薄筆記本電腦、車載系統 | 臺式機、服務器、工作站、高性能游戲本 |

| 設計目標 | 低功耗、延長電池續航、小體積 | 高性能、高帶寬、高容量 |

| 物理形態 | 焊接在主板上(BGA 封裝),呈小方塊芯片狀 | 插槽式內存條,可更換和升級 |

| 功耗與電壓 | 極低。工作電壓更低且通常是動態可變的(例如 1.05V / 0.5V) | 較低(相比 DDR4)。標稱電壓通常為 1.1V |

| 通道架構 | 通常為 16 位或 32 位通道,但可配置多通道以實現高帶寬 | 單個內存條 (DIMM) 包含兩個 32 位的獨立通道(共 64 位) |

| 性能 | 速率很高(例如 5500 MT/s, 6400 MT/s 或更高),但可能為換取低功耗而在延遲(Latency)上有所妥協 | 起始速率較高(例如 4800 MT/s),可超頻至極高頻率,通常在同等頻率下具有更低的延遲和更強的綜合性能 |

DDR5 與之前版本 DDR 對比

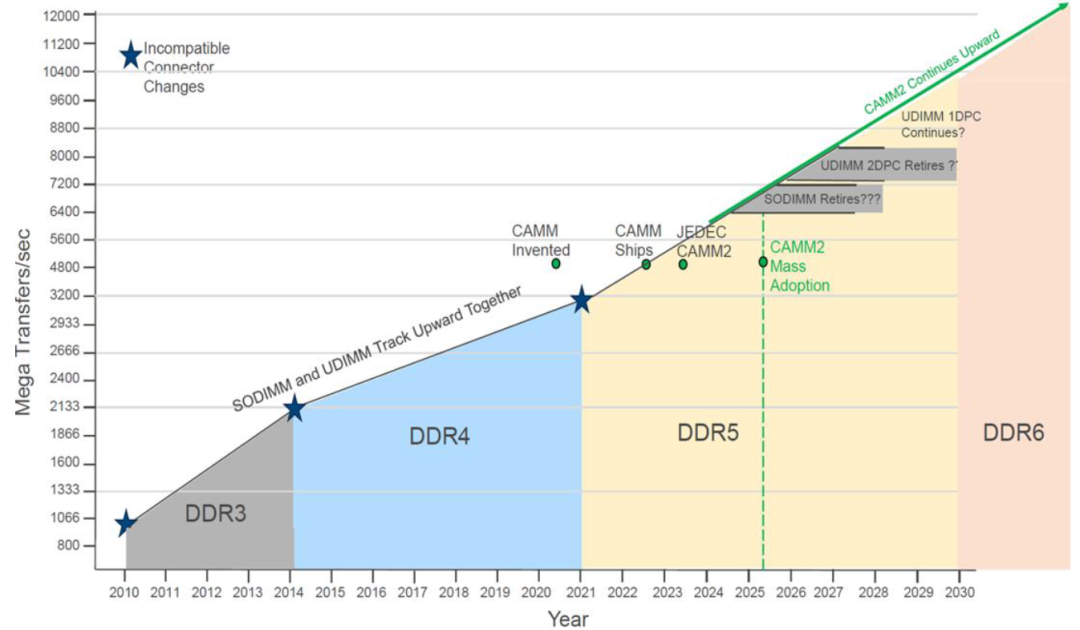

下圖是 DDR 進化的圖表:

可以看到,JEDEC 在 2021 年的時候發布了 CAMM2 模組,嘗試解決 SODIMM 的系統級問題,CAMM2 從性能、尺寸、布線難度、可替換性、EMC 噪聲等多方面進行了改進,后續章節會詳細介紹。

下表是 DDR5 和之前 DDR 版本的一個比較:

| DDR 版本 | DDR1 | DDR2 | DDR3 | DDR4 | DDR5 |

| 電壓 | 2.5V | 1.8V | 1.5V | 1.2V | 1.1V |

| 預取緩存區 | 2 | 4 | 8 | 8 | 16 |

| 芯片密度 | 128Mb-1Gb | 128Mb-4Gb | 512Mb-8Gb | 2Gb-16Gb | 8Gb-64Gb |

| 數據速率(MT/s) | 200-400 | 400-800 | 800-2133 | 1600-3200 | 3200-6400 |

| Bank 組 | 0 | 0 | 0 | 4 | 8 |

| ODT | On Board | ODT Enabled | Normal, Dynamic Modes | Park Modes | Nominal Er/Rd |

| IO 時鐘 MHz | 100-200 | 200-533 | 533-1200 | 1066-2400 | 2133-3200 |

我們來回顧一下 DDR 的發展歷史:

-

由 IBM 于 1980 年代發明

-

1990 年在國際固態電路研討會上發表

-

三星于 1998 年 6 月發布首款商用 DDR SDRAM 芯片 (64 Mbit)

-

JEDEC 于 2000 年 6 月敲定規格 (JESD79)

-

首款使用 DDR SDRAM 的零售 PC 主板于 2000 年 8 月發布

-

DDR1 (2000): 在時鐘的上升沿和下降沿皆傳輸數據,速率加倍

-

DDR2 (2003): 改善的 I/O 總線信號,雙通道模式

-

DDR3 (2007): 增加的帶寬,降低的功耗

-

DDR4 (2014): 四點時鐘周期數據傳輸,高效的 DRAM Bank 組

-

DDR5 (2022): 更佳的電源管理,提升的通道效率,更強的性能

-

CAMM2 模組(2024)

- LPDDR5 CAMM2(2024):低功耗DDR5

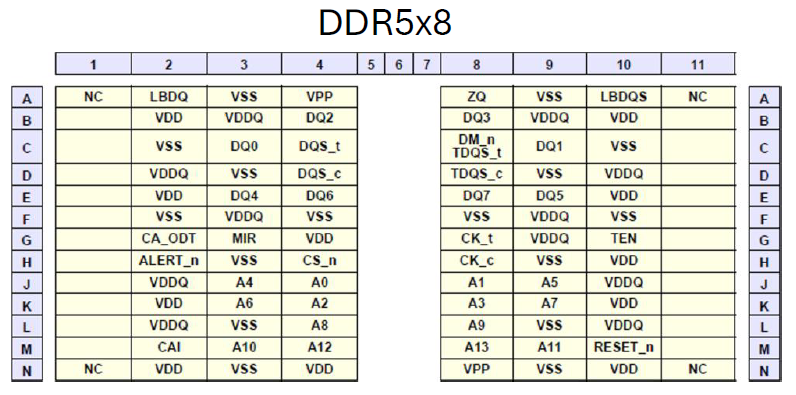

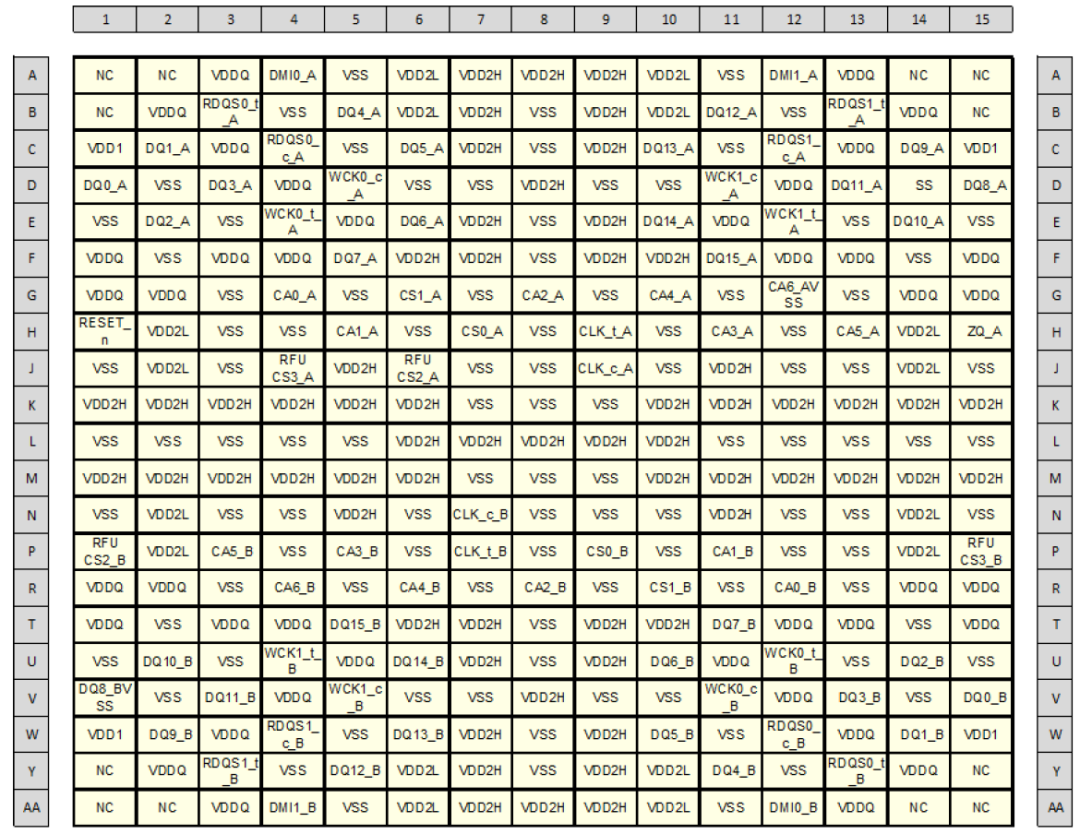

DDR5 DRAM 引腳

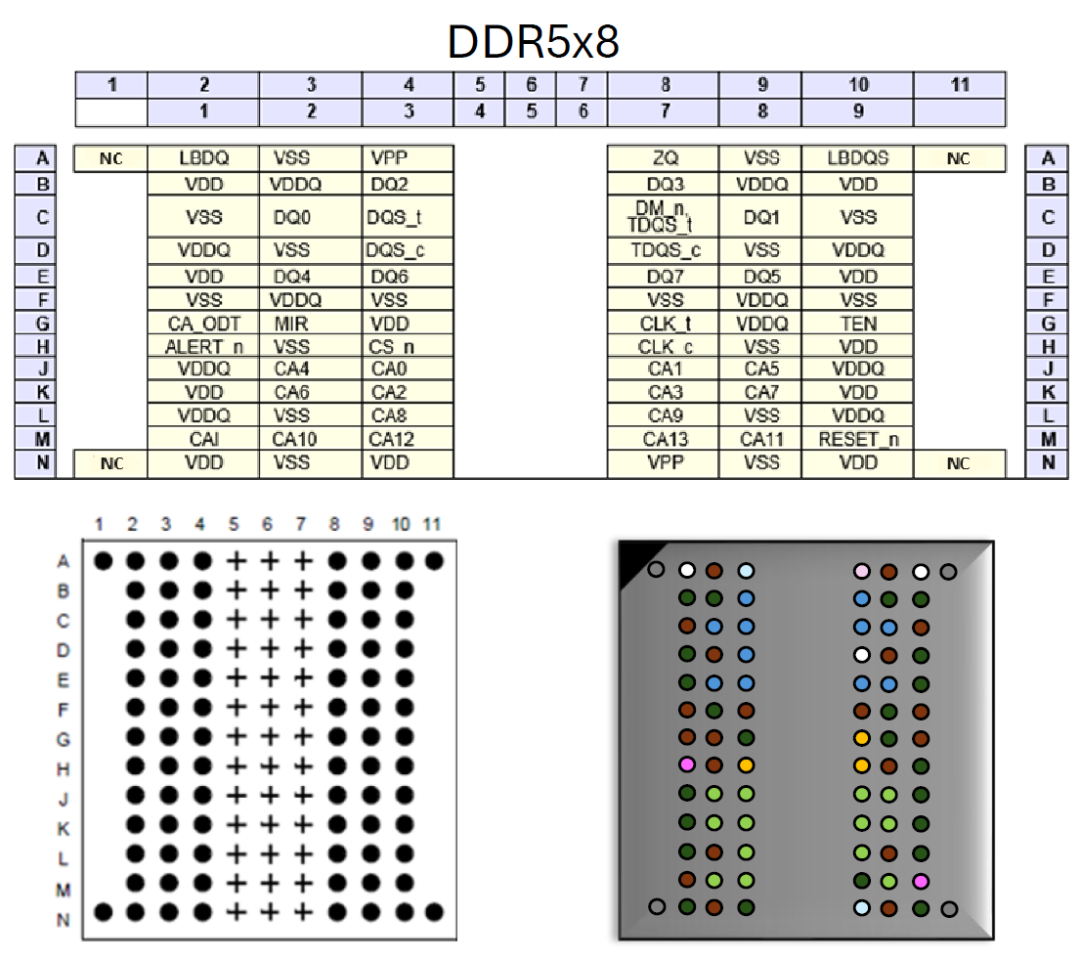

8位數據位寬的封裝由 82 個 ball 組成,尺寸最大為 10mm x 11mm x 1 mm。上圖右下為頂視圖(右圖為從定向下穿透視角)。做下中“+”表示沒有 Ball。

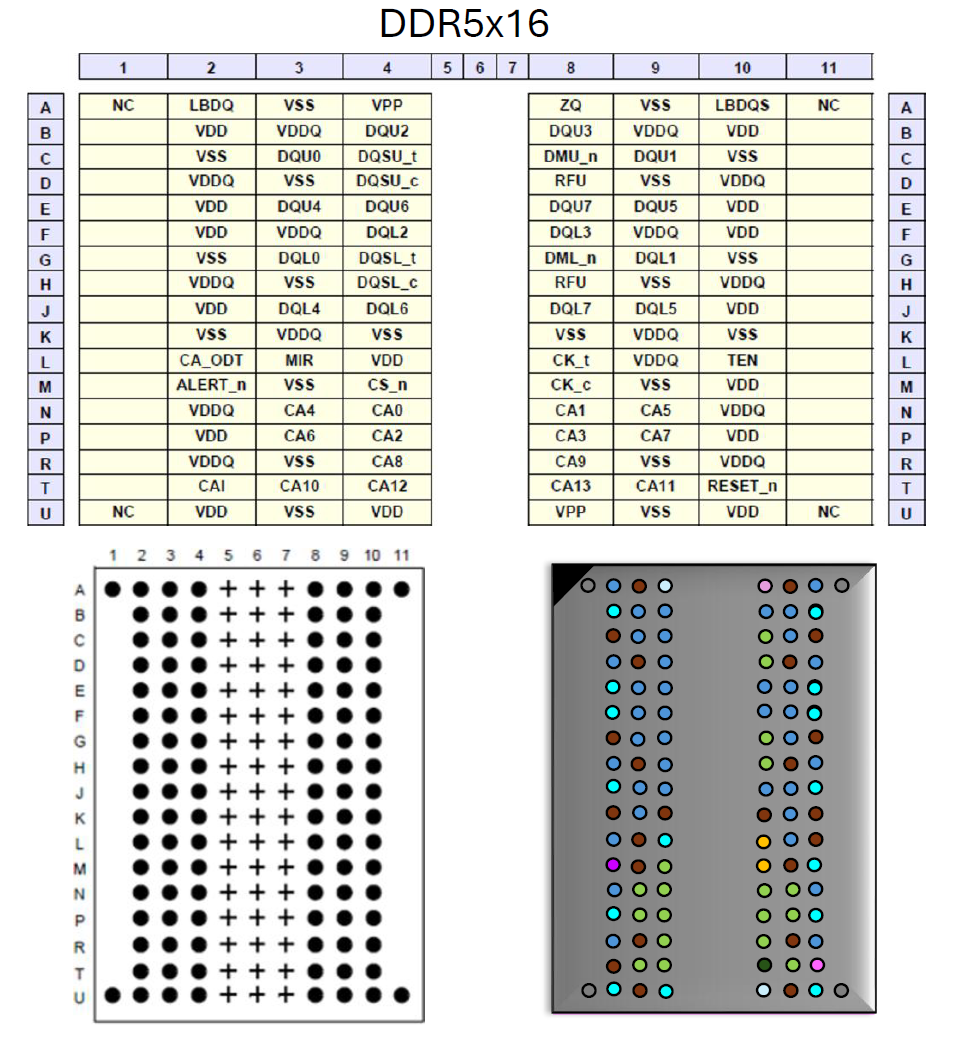

16位數據位寬的封裝由 106 個 ball 組成,尺寸最大為 10mm x 14mm x 1mm。

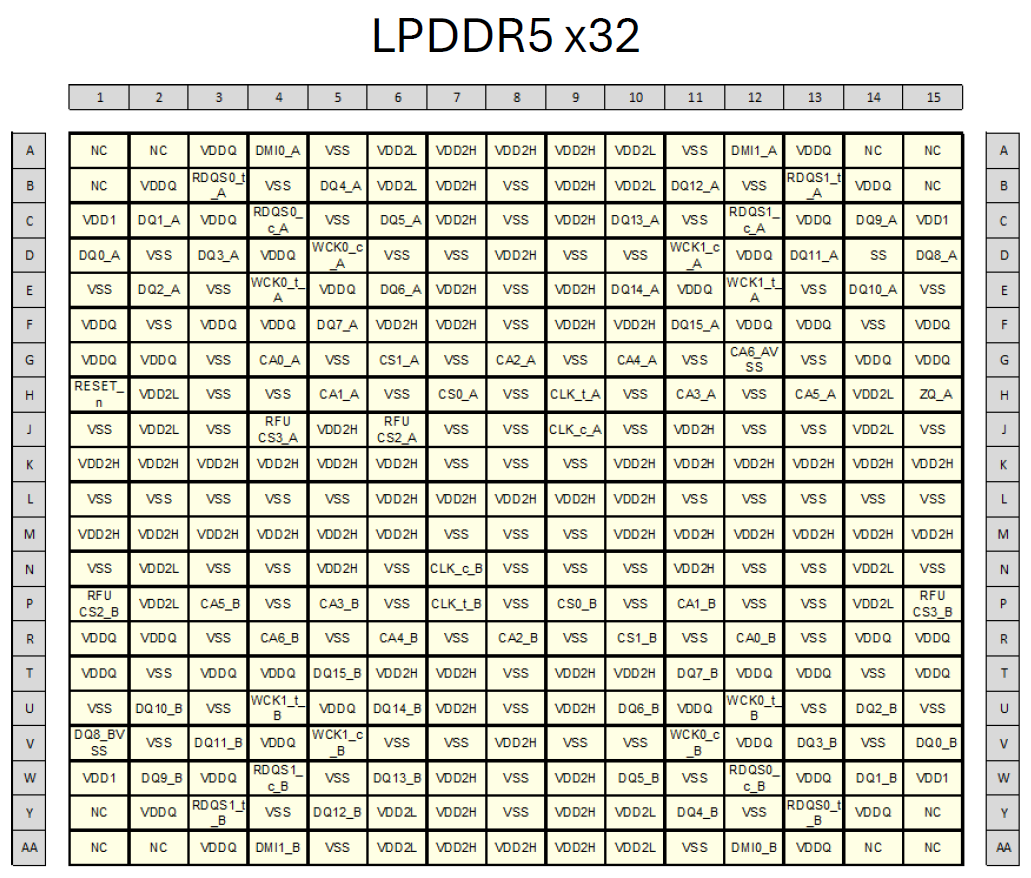

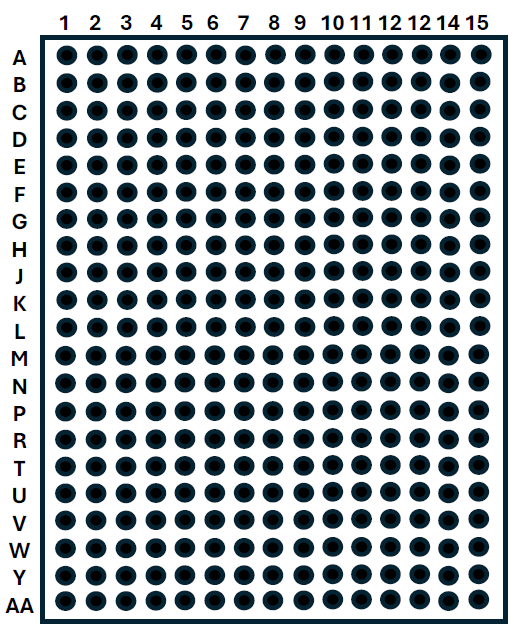

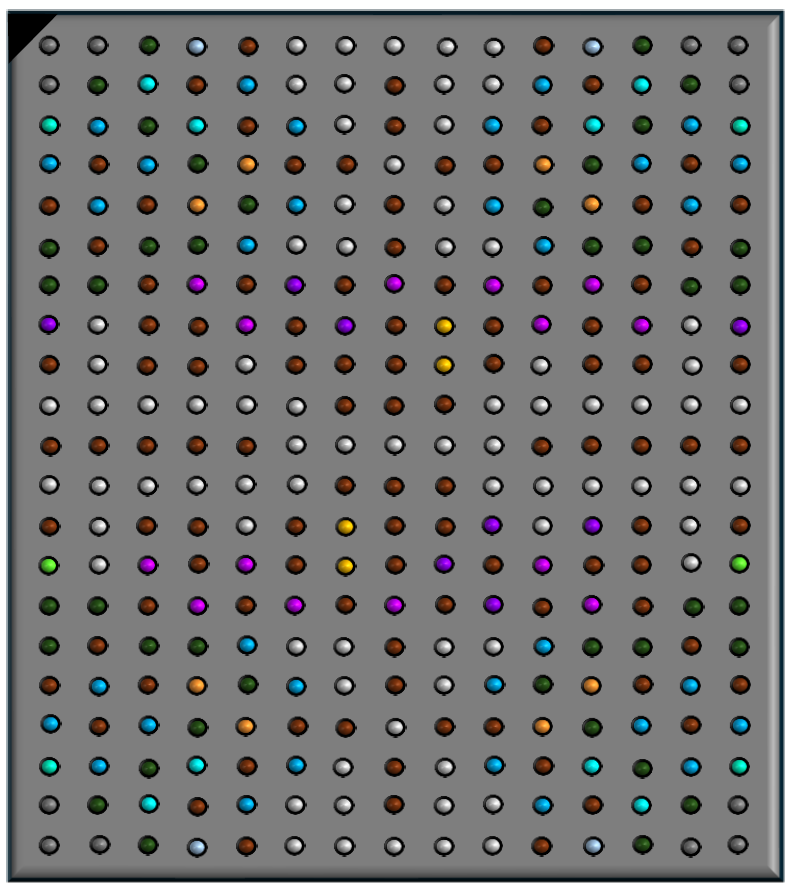

32 位數據位寬的 LPDDR5 封裝由 315 個 ball 組成,最大尺寸為 12.4mm x 15mm x 1.1mm。

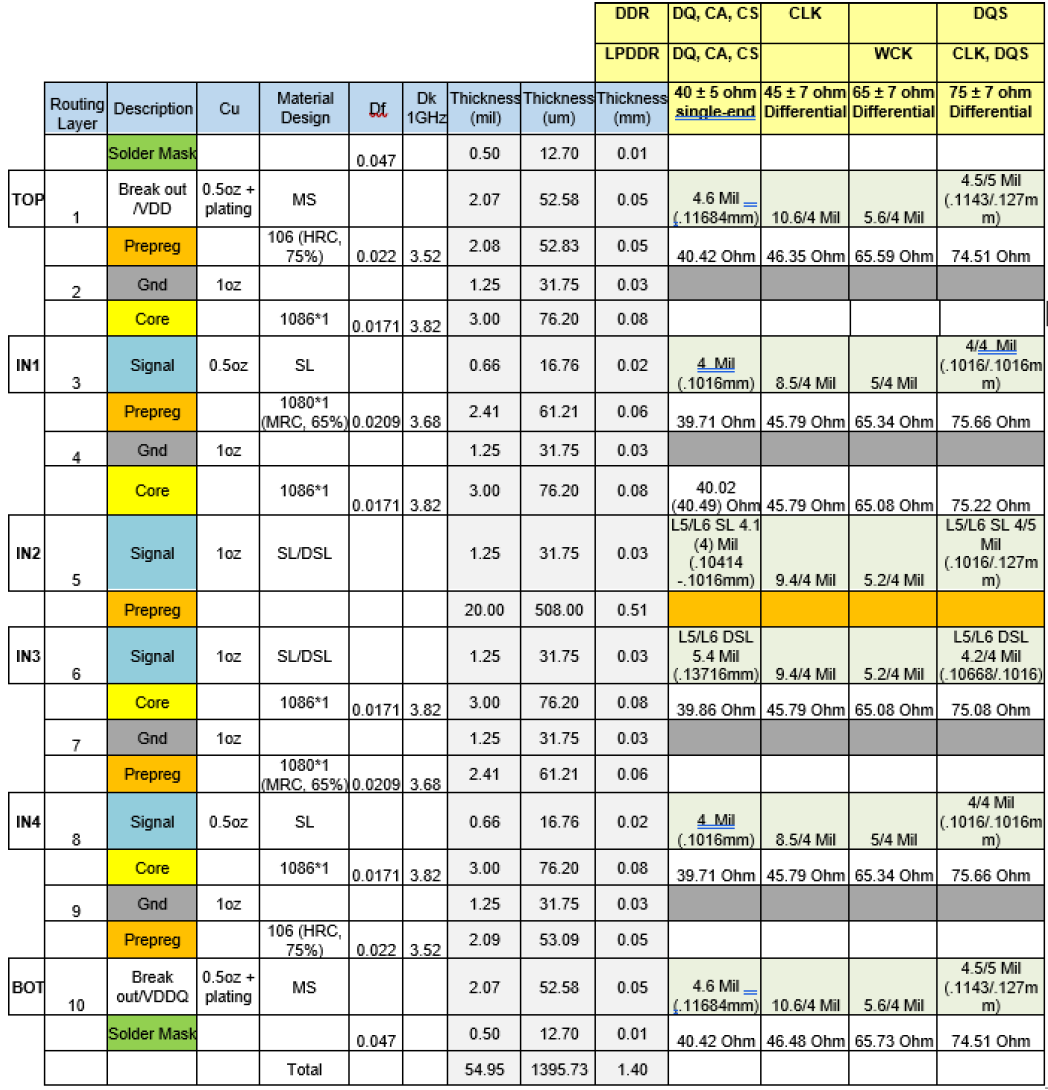

目標阻抗

走線寬度對于匹配目標阻抗非常重要。實際寬度取決于電路板層疊結構。目標是:

DDR5

-

DQ/CA/CS => 40 Ohm

-

DQS => 75 Ohm

-

時鐘

- 主板上和模組上到時鐘緩沖器:75 Ohm

- 模組上從時鐘緩沖器到 DRAM:45 Ohm

LPDDR5:

-

DQ/CA/CS => 40 Ohm

-

DQS/CLK => 75 Ohm

-

WCK => 65 Ohm

間距

DDR5 布線的一個關鍵是保持 SOC 廠家給出的間距要求。當然可能的情況下間距越大越好。以下是走線最小間距建議:

-

時鐘-時鐘=> .25 mm

-

時鐘 到 CA=> .3mm

-

CA 到 CA => .15 mm

-

DQ 到 DQS.18 mm

-

DQ 到 DQ => .18 mm

-

BYTE 到 BYTE => .3 mm

-

WCK 到 DQ => .375 mm

-

WCK 到 DQS => .375 mm

-

子通道 到 子通道 => .5 mm

線長匹配(DDR Memory Down)

長度匹配規范由 SoC 單獨設置。通常,需要匹配以下組的值:-

時鐘到時鐘:一個通道中的所有時鐘

-

時鐘到數據選通 (DQS)

-

數據(DQ) 到 DQS

-

一個字節內的 DQ

-

命令地址 (CA) 線到鐘

-

一個子通道內的 CA 線

-

片選(CS) 到時鐘

-

一個子通道內的 CS 線。

總線長匹配所需的額外數據:

-

芯片供應商提供的 SoC 封裝長度(焊盤到Die)

-

打開 Electrical Z Axis Delay 選項

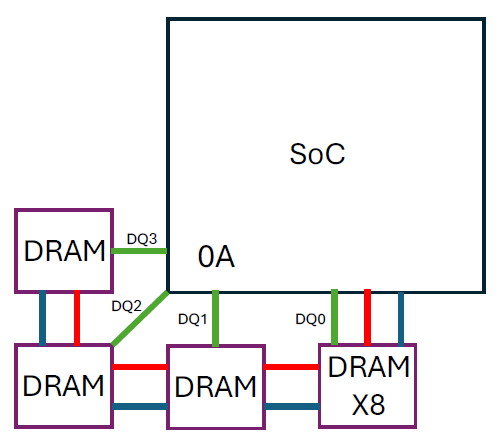

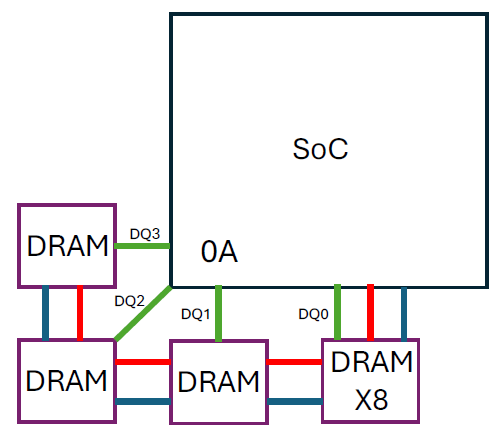

以下是單通道1 個子通道 0A 的配置示例:

每個子通道包含以下信號:

-

13 CA/4CS(藍色)

-

時鐘(紅色)

-

每個DRAM 24 Data/4 DMI/4 DQS/8DQ/1 DMI/1 DQS(綠色)

可能的長度匹配規則:

-

時鐘到 CA < 10mm?

-

DQ-DQS < 0.5mm?

-

DQx8 < 0.5mm

-

每個子通道的 CA < 1 mm

以下是調線長和過孔高度影響的布線技巧

-

在 2 個相鄰層上走所有 CA 線

-

在同一層上走所有 DQ, DMI 和 DQS

-

保持時鐘線最短 – 它們決定一切

-

檢查封裝長度 - 它們可能會破壞調線長的計劃。

-

注意規則,例如 (-20 < CLK-DQS) < 40)。舉個例子,如果時鐘是60 mm, DQS 長度可以在 80 mm和 20 mm之間。

線長匹配(LPDDR5 Memory Down)

長度匹配規范由 SoC 單獨設置。通常,需要匹配以下組的值-

時鐘到時鐘 - 所有子通道時鐘

-

時鐘到 DQS

-

DQ 到 DQS

-

一個字節內的 DQ

-

CA 線到時鐘

-

一個子通道內的 CA 線

-

CS 到 時鐘

-

一個子通道內的 CS 線。

-

寫時鐘 (WCK) 到 DQ

-

WCK 到 時鐘

以下是單通道,4個子通道0A/0B/0C/0D 的配置示例:

每個子通道包含以下信號信號:

-

7 CA/4CS

-

時鐘

-

16 Data/2 DMI/2 DQS

-

2 WCK

可能的長度匹配規則

-

時鐘 到 CA < 5mm?

-

時鐘 到 WCK < 10 mm

-

DQ-DQS< 3 mm

-

DQx8 < 4mm

-

每個子通道的 CA < 7 mm

以下是調線長和過孔高度影響的布線技巧

-

在同一層上布線所有 CA 線

-

在同一層上布線所有 DQ, DMI 和 DQS

-

保持時鐘線短 – 它們決定一切

-

檢查封裝長度 -它們可能會破壞調線長的計劃。

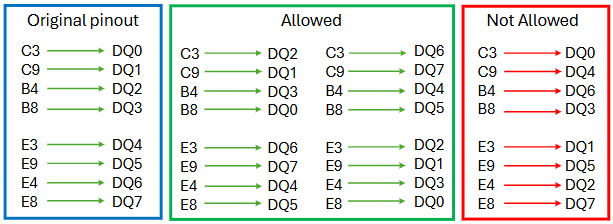

DDR5 引腳交換(Pin Swapping)

DDR5 Layout 中允許進行一些位交換。字節分為 2 個半字節 (nibble):高位和低位。

例如:在位寬為 8 的器件上:

引腳 C3, C9, B4 和 B8 是分配給 DQ[0-3] 的低位;引腳 E3, E9, E4 和 E8 是分配給 DQ[4-7] 的高位。

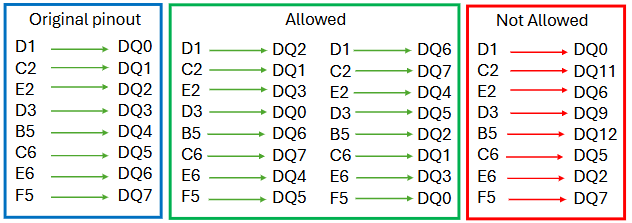

每個半字節中的位可以在其內部交換。您也可以交換整個半字節,只要同組的 4 個網絡保持在同一個半字節中。下圖中綠色框是可以交換的示例,紅色框因為網絡不在同一個半字節中,因此不允許交換。

LPDDR5 引腳交換(Pin Swapping)

LPDDR5 layout 中允許進行一些位交換。

-

字節內的任何位都可以交換

-

不允許在字節之間交換

-

可以在子通道內交換整個字節 (包括 WCK, DQS, DMI 和所有 DQ 線)

-

如果可以使布線更整潔,可以交換整個子通道。

以下為可交換及不可交換的示例:

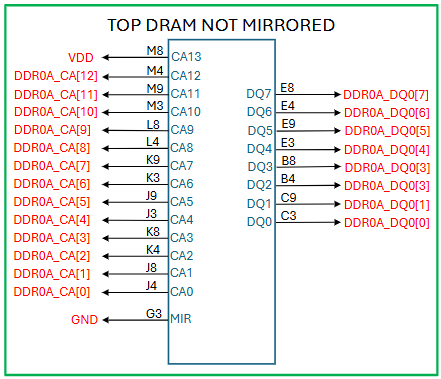

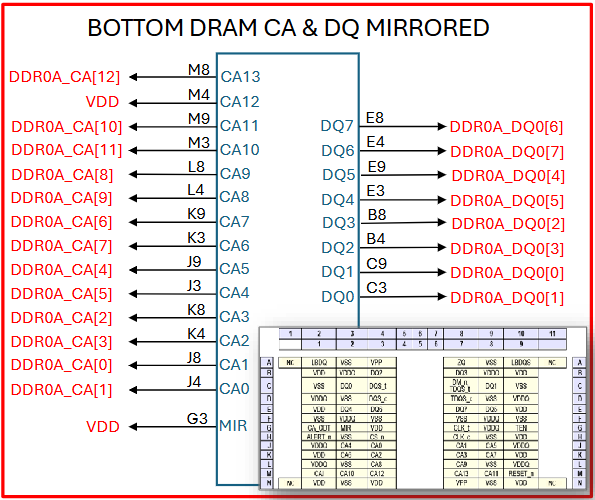

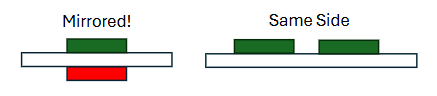

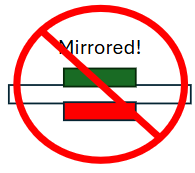

DDR5 鏡像(Mirroring)

當 MIR 引腳連接到 VDD 時,DDR5 DRAM 會被鏡像。CA 和 DQ 網絡需要被鏡像。要進行鏡像,交換 SoC 網絡 CA[0] 和 CA[1]、CA[2] 和 CA[3]、CA[4] 和 CA[5]、CA[6] 和 CA[7]、CA[8] 和 CA[9]、CA[10] 和 CA[11],以及 CA[12] 和 VDD。

頂層沒有鏡像的 DRAM:

底層 DRAM CA 及 DQ 被鏡像:

LPDDR5 無法配置鏡像。

DDR5 拓撲(Topologies)

講拓撲前再明確一下 Channel(內存通道)、Subchannel(子通道)、Rank(內存列)定義和功能。

Channel(內存通道)

Channel 是 CPU 內存控制器與內存模組(DIMM,即內存條)之間的最高級別數據總線。當我們說一個 CPU 支持“雙通道”(Dual-Channel)或“四通道”(Quad-Channel)時,指的是 CPU 有多少條這樣獨立的主高速公路。在 DDR4 時代,一個 Channel 對應一條 64-bit(不含ECC)的數據總線。在 DDR5 中,一個 Channel 依然是64-bit寬。例如,一個“雙通道”CPU(如桌面i9 或 Ryzen 9)就擁有一個128-bit(2 x 64-bit)的內存接口。

Subchannel (子通道)

這是 DDR5 最核心的架構變革。DDR5 將每條 64-bit的 Channel(主通道)拆分成了兩個獨立的 32-bit 的 Subchannel(子通道)。如果包含 ECC(錯誤校驗碼),那么一個 64-bit 的 Channel 被分為兩個 40-bit 的 Subchannel(32-bit 數據 + 8-bit ECC)。這兩個 32-bit 的 Subchannel 是獨立尋址和獨立操作的,它們有各自的地址/命令總線。與 DDR4 相比,表面看都是獲取 64 字節,但 DDR5 的優勢在于它有兩個32-bit子通道。當 Subchannel A 在忙于一個請求時,內存控制器可以立即向 Subchannel B 發送另一個完全獨立的請求。

Rank (內存列)

Rank是一組物理 DRAM 芯片(內存顆粒)的集合,這些芯片共享同一個片選信號(Chip Select, CS),并共同組成了 Subchannel 所需的數據位寬。在DDR5中,一個 Subchannel 是 32-bit 寬。如果一根內存條使用的是x8(8-bit位寬)的內存顆粒,那么一個 Rank 就需要4個這樣的顆粒(4 x 8 bits = 32 bits 來喂飽一個 Subchannel。

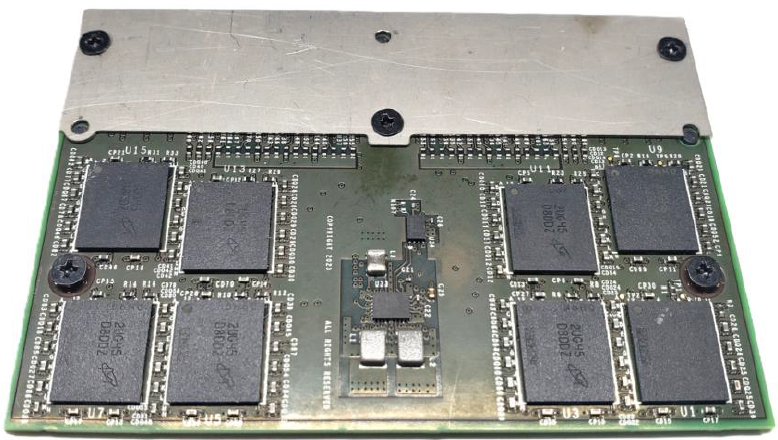

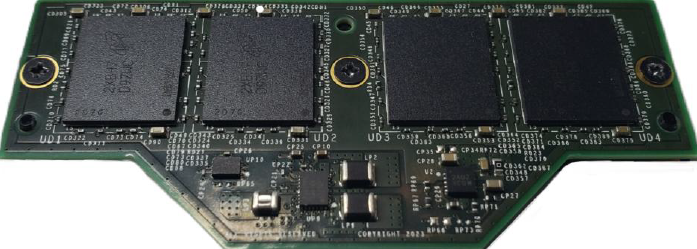

“Single-Rank (1R)” DIMM 通常意味著它為每個 Subchannel 提供了1個 Rank。對于使用 x8 顆粒的 DIMM,它總共需要 4 (SubCh A + 4 (SubCh B) = 8 個顆粒。

“Dual-Rank (2R)” DIMM 意味著它為每個 Subchannel 提供了 2 個 Rank。它總共需要 8 (SubCh A) + 8 (SubCh B) = 16 個顆粒。

單 Subchannel 單 Rank x 16 DRAM

對于單個子通道,1個 Rank,16 位的 DRAM,需要 2 個顆粒。可以同側或兩側擺放:

2 個 DRAM:

-

有獨立的數據總線

-

連接同一個 CLK、CS

-

僅共享 CA 總線

-

CA、CS 和 CLK 采用菊花鏈拓撲(Daisy chain)

-

1 個 ODT 引腳連接到 VDD 以表示子通道的末端

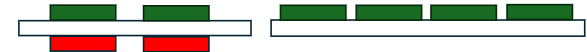

單 Subchannel 單 Rank x 8 DRAM

對于單個子通道,1個 Rank,8 位的 DRAM,需要 4 個顆粒。可以同側或兩側擺放:

4 個 DRAM:

-

有獨立的數據總線

-

連接同一個 CLK、CS

-

僅共享 CA 總線(兩側的情況 CA 可以鏡像)

-

CA、CS 和 CLK 采用菊花鏈拓撲(Daisy chain)

-

1 個 ODT 引腳連接到 VDD 以表示子通道的末端

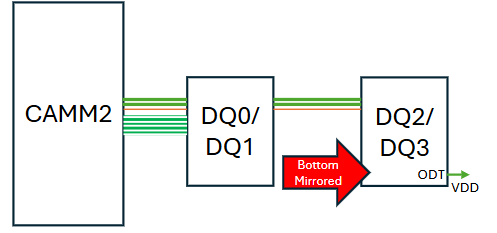

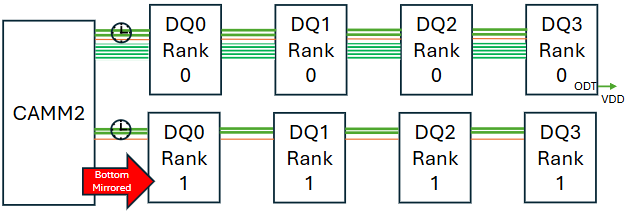

單 Subchannel 雙 Rank x 8 DRAM

對于單個子通道,2個 Rank,8 位的 DRAM,需要 8 個顆粒。

DRAM:

-

分別在頂層、底層兩側

-

共享數據總線

-

共享 CA 總線

-

CA、CS 和 CLK 采用菊花鏈拓撲(Daisy chain)

-

每個 rank 有獨立的 CLK、CS

-

4 個 DRAM 連接到頂層的 CLK0 和 CS0

-

4 個 DRAM 連接到底層的 CLK1 和 CS1

-

-

1 個 ODT 引腳連接到 VDD 以表示子通道的末端

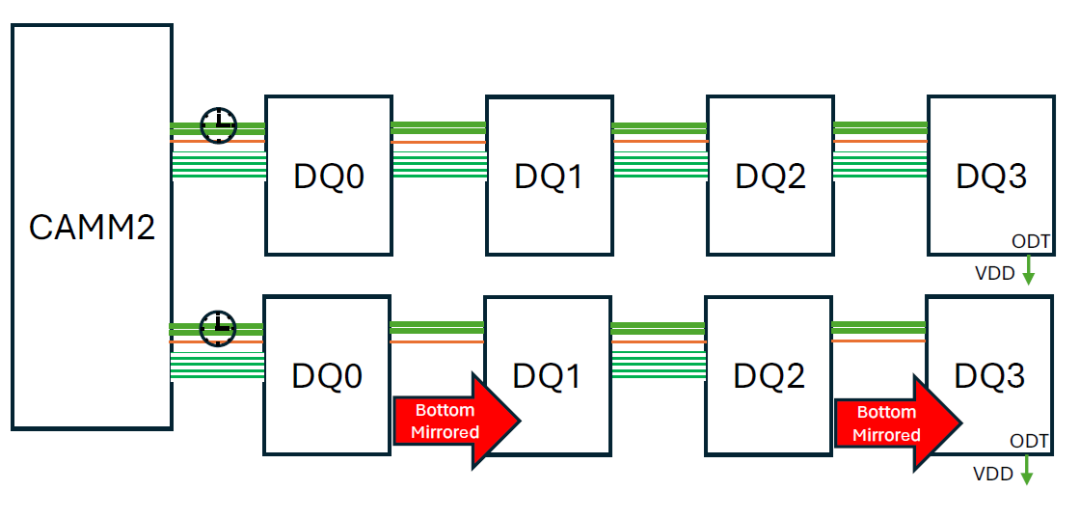

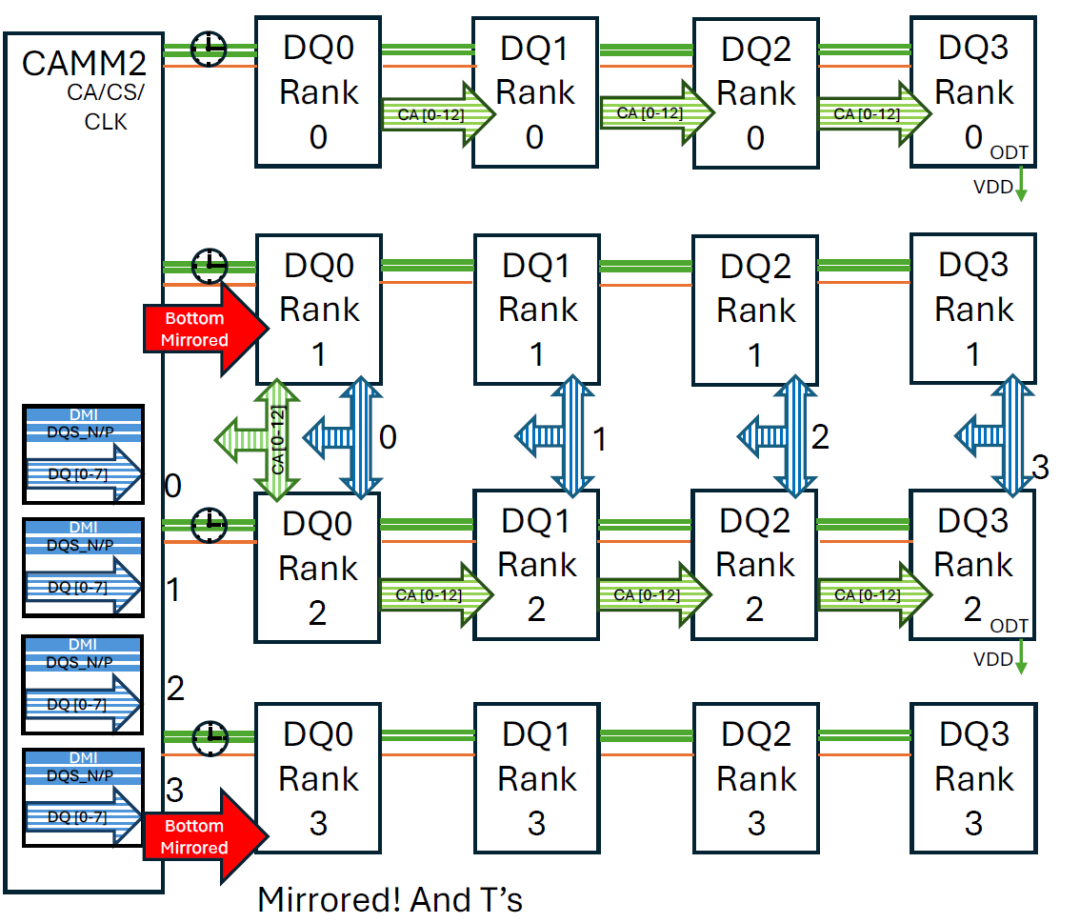

單 Channel 4 Rank x 8 DRAM

對于單個通道,4 個 Rank,8 位的 DRAM,需要 8 個顆粒。

-

DRAM 分別在頂層、底層兩側

-

共享數據總線

-

共享 CA 總線

-

CA、CS 和 CLK 采用菊花鏈拓撲(Daisy chain)

-

每個 rank 有獨立的 CLK、CS

-

鏡像 DRAM

-

Rank 0 和 1 被鏡像并共享 CA 和 DQ 線

-

Rank 2 和 3 被鏡像并共享 CA 和 DQ 線

-

CA 線是菊花鏈和 T 型拓撲的結合

-

DQ 線可以是菊花鏈或 T 型拓撲

-

ODT 在 Rank 0 和 Rank 2 的末端連接到 VDD

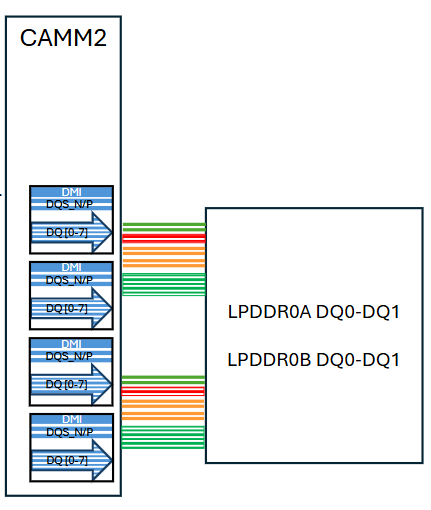

LPDDR5 拓撲

16 位單 Channel DRAM

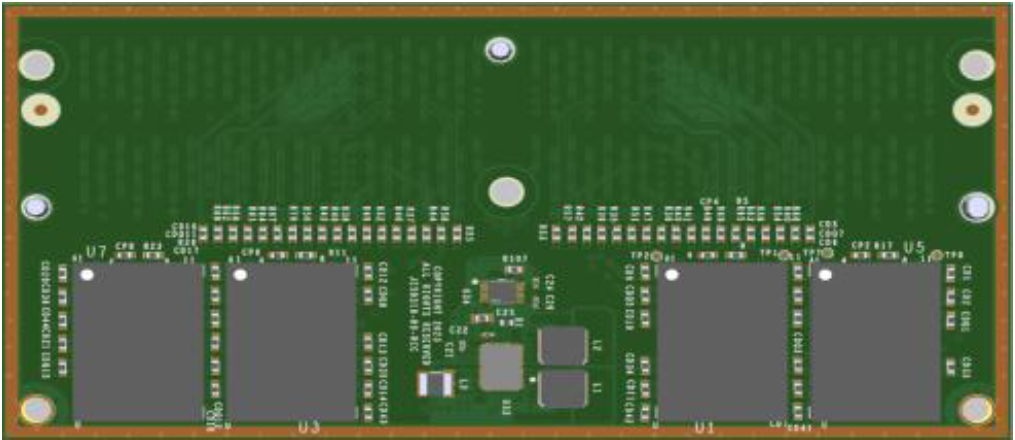

來自 CAMM2 的每顆 DRAM 4 個數據字節,不可鏡像。

-

DRAM 全部位于一側

-

獨立的數據線 - 每個子通道 16 條

-

啟用 DMI

-

雙子通道

-

每個子通道 7 條 CA 線

-

4 條 CS 線 (如果需要)

-

.8mm 間距 – 適用于 BB Via 配置和盤中孔

去耦電容

DDR5 CAMM2 去耦電容指南:|

電壓 |

指南 |

備注 |

|

VDD |

每顆 SDRAM 至少兩個到 VSS 的去耦電容,建議每顆 DRAM 平均 30uF |

應盡可能靠近 DRAM VDD 焊球 |

|

VDDQ |

每顆 SDRAM 至少兩個到 VSS的去耦電容,建議每顆 DRAM 平均 7.5uF |

應盡可能靠近 DRAM VDDQ 焊球 |

|

VPP |

每個 DRAM VPP 引腳至少一個去耦電容,建議每顆 DRAM 平均 3.5uF |

應盡可能靠近 DRAM VPP 焊球 |

|

VIN_BULK |

PMIC 輸入附近:6 顆 22uf, 3 顆 0.1uF CAMM2 連接器 VIN_BULK 引腳附近:4 顆 22uF 或 0.1uF |

|

| VDD1 | 建議每顆 DRAM 平均 5uF | 應盡可能靠近 DRAM VDD1 焊球 |

| VDD2H | 建議每顆 DRAM 平均 15uF | 應盡可能靠近 DRAM VDD2H 焊球。如果 VDD2H 和 VDD2L 合并為一根電源軌,則將該軌的兩個電容相加。 |

| VDD2L | 建議每顆 DRAM 平均 15uF | 應盡可能靠近 DRAM VDD2L 焊球。 |

| VDDQ | 建議每顆 DRAM 平均 15uF | 應盡可能靠近 DRAM VDDQ 焊球。 |

| VIN_BULK | PMIC 輸入附近:8 顆 22uf, 4 顆 0.1uF CAMM2連接器 VIN_BULK 引腳附近:6 顆 0.1uF | |

|

1. VDD, VDDQ 和 VPP 的去耦電容值因模組而異,并可能交錯以實現最佳的整體阻抗 vs 頻率響應。 |

||

|

2. VDD, VDDQ 和 VPP 的推薦去耦值為 1uF, 22uF, 4.7uF 和 10uF。 |

||

|

3. 根據 DRAM 封裝尺寸,可能無法實現所有布局。 |

||

|

4. 有關 PMIC 芯片周圍去耦的詳細信息,請參閱 PMIC 規格。 |

||

文中的部分圖片和內容引用自 Charlene McCauly 以及 Terrie Duffy 的 “設計者眼中的 DDR5” 報告。

-

DDR5

+關注

關注

1文章

480瀏覽量

25800 -

LPDDR5

+關注

關注

2文章

98瀏覽量

13378

發布評論請先 登錄

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

Introspect DDR5/LPDDR5總線協議分析儀

三種主流內存技術(DDR、GDDR、LPDDR)的速度對比與應用和DDR5芯片的設計

大多DRAM廠商DDR5相應產品發售,DDR5能成為市場的主流嗎

5G時代你是等DDR5上市 還是升級DDR4內存

內存條ddr4和顯卡ddr5

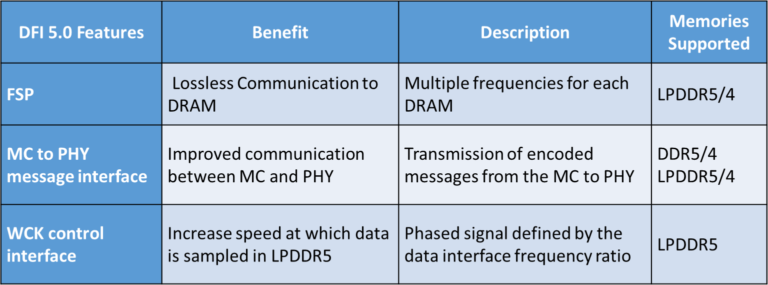

DFI 5.0如何確保DDR5/LPDDR5系統的更高性能

DDR5 設計指南(一):DDR5 VS LPDDR5

DDR5 設計指南(一):DDR5 VS LPDDR5

評論