以下文章來源于OpenFPGA,作者碎碎思

——來自 Shinshu University 的最新設計揭示低位寬算術硬件化的新途徑

原標題:Hardware-Efficient Accurate 4-bit Multiplier for Xilinx 7 Series FPGAs

隨著 IoT、邊緣計算等應用對低位寬、高并行、高效率算術運算的需求攀升,基礎算術電路,如 4 位乘法,如何在 FPGA 上做到“資源最小化+速度極致”便成為一道新的挑戰。來自日本信州大學(Shinshu University)研究團隊的最新設計中,一個專為 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了僅 11 個 LUT + 2 個 CARRY4 塊,關鍵路徑延遲達到 2.75 ns。這是一次令人印象深刻的工藝優化實踐。

核心成果概括

設計使用了 Xilinx 7 系列 FPGA 的 LUT-和-CARRY4 硬件結構。

只有 11 個 LUT + 2 個 CARRY4 模塊即可實現功能。

關鍵路徑延遲僅為 2.750 ns。

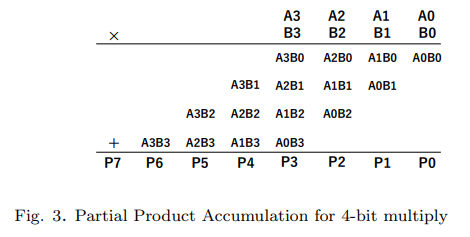

通過重組 LUT 內邏輯函數、使用 LUT6_2 模式(5 輸入、2 輸出)優化資源和速度。

專用于 Xilinx 7 系列,尚未驗證其他 FPGA 架構。

為什么值得關注?

低位寬算術仍然重要:即便是 4 位乘法,在很多應用(如量化神經網絡、圖像處理、加速器內部更細粒度模塊)里都是性能瓶頸。資源與延遲的極致優化能帶來更高并行度。

研究者還精心設計了 CARRY4 的集成方式。CARRY4 是 FPGA Slice 中專用于快速進位計算的硬件結構,其延遲遠低于使用 LUT 構建的等效邏輯,因此能夠顯著加速運算。設計通過利用相鄰 Slice 之間 CARRY4 的硬連線結構,實現了無瓶頸的長進位鏈。

LUT + CARRY4 混合使用展示 FPGA 原語優化潛力:研究利用 CARRY4 快速傳遞進位鏈、使乘法結構更緊湊。

資源 vs 延遲雙向優化:減少 LUT 數量的同時,還縮短了延遲,實屬少見。

可為各種低位算術構件設計提供參考:包括加法器、累加器、量化乘法器、低精度加速模塊等。

設計關鍵技術細節

LUT6_2 模式:在 Xilinx 7 系列中,LUT6_2 提供 5 輸入 + 2 輸出的功能,研究正是利用這一結構最大化邏輯密度。

CARRY4 模塊:專門用于進位鏈,延遲低、資源優勢明顯。關鍵路徑中將乘法中 “累加部分” 的進位傳遞交給 CARRY4。

邏輯重組:將傳統乘法展開的邏輯組合優化,減少 LUT 層級并合理安排路徑,使得關鍵路徑延遲縮短。

驗證與測試:對所有輸入組合進行窮舉仿真,確保功能正確。然后在 FPGA 上測量延遲/資源,與其它方案對比。

限制與思考

本設計專用于 Xilinx 7 系列,不保證直接遷移到其他系列或廠商 FPGA。

雖優化效果顯著,但 4 位乘法的位寬較低,實際系統中還需考慮數據寬度、流水線結構、并行度、資源共享等。

面向更高位寬(8 bit、16 bit)時,邏輯復雜度、布線擁塞、時鐘域問題等挑戰明顯增加。

在實際產品中,除了邏輯與延遲,功耗、可靠性、可測試性、資源可重用性等也需考慮。

應用建議

若你正在做 量化神經網絡加速器(如 4 位/8 位乘加),該設計思想可用于內核優化。

在 FPGA 資源緊張的場景下(如低功耗、邊緣設備),可考慮借鑒 LUT+CARRY 優化策略。

在教研/教學中,該設計是“低位寬算術優化”的優秀案例,可用于學生項目或課程設計。

如果你使用 Xilinx 7 系列 FPGA,可嘗試基于此設計搭建自己的低位乘法核,再擴展到加法、累加器、矩陣乘法模塊。

文章鏈接

https://arxiv.org/abs/2510.21533

-

FPGA

+關注

關注

1662文章

22456瀏覽量

637919 -

Xilinx

+關注

關注

73文章

2202瀏覽量

131581 -

乘法器

+關注

關注

9文章

221瀏覽量

38873

原文標題:硬件高效乘法器:4 位乘法在 Xilinx FPGA 上只用 11 個 LUT,延遲僅 2.75 ns

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA乘法器設計

FPGA乘法器軟核設計問題

4位二進制乘法器電路

怎么設計基于FPGA的WALLACETREE乘法器?

基于IP核的乘法器設計

基于FPGA的WALLACE TREE乘法器設計

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

使用Xilinx 7系列FPGA的四位乘法器設計

使用Xilinx 7系列FPGA的四位乘法器設計

評論