?

**** 第一章:**** KintexUltraScale+系列介紹

Kintex? UltraScale+? 器件在 FinFET 節點中提供最佳性價比/功率平衡,為需 要高端功能(包括 33Gb/s 收發器和 100G 連接核心)的應用提供經濟高效的解決方 案。我們的中端系列非常適合數據包處理和 DSP 密集型功能,并且非常適合無線 MIMO 技術、Nx100G 有線網絡以及數據中心網絡和存儲加速等應用。

Kintex UltraScale+器件價值與優勢如下:

可編程系統集成

高達 120 萬系統邏輯單元

用于片上存儲器集成的 UltraRAM

集成了 KR4 RS-FEC 、PCIe? Gen4 和 150G Interlaken 內核的 100G 以太網 MAC

提高系統性能

16G 和 28G 支持背板的收發器

中速級 2666 Mb/s DDR4

降低 BOM 成本

VCXO 和分數 PLL 集成降低了時鐘元件成本

總功耗降低

與 7 系列 FPGA 相比,功耗最多可降低 60

更緊密的邏輯單元封裝可降低動態功耗

加速設計生產力

與 Vivado? 設計套件協同優化,可快速完成設計

用于智能 IP 集成的 SmartConnect 技術

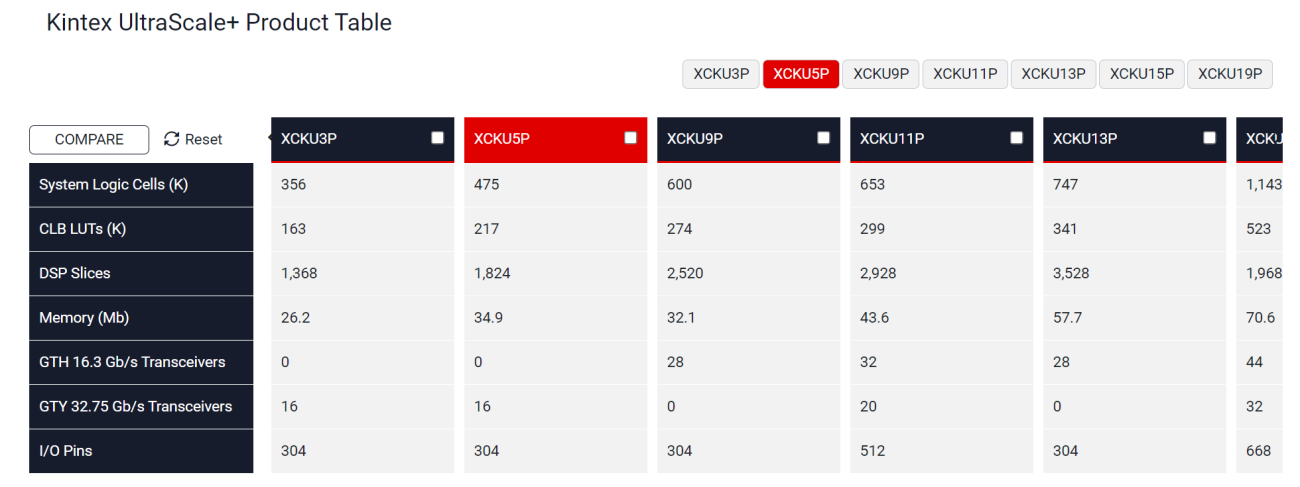

Kintex UltraScale+器件資源如下表列出,我們選用KU3P/KU5P 做為核心板的主 控芯片:

?編輯

[]()[]()第二章: ****璞致 ****KintexUltraScale+開發板概述

[]()2.1.板卡概述

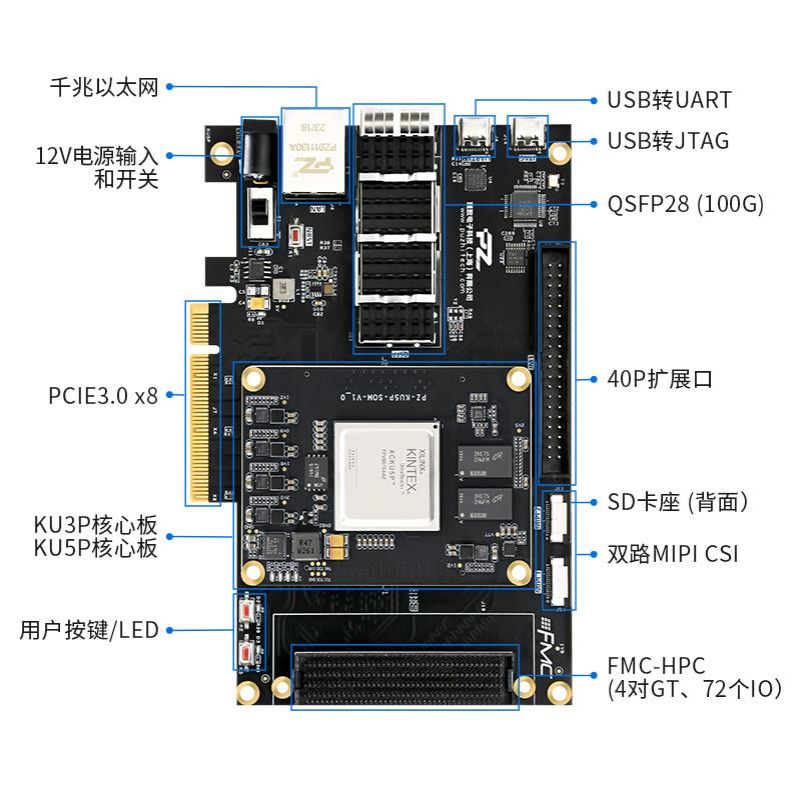

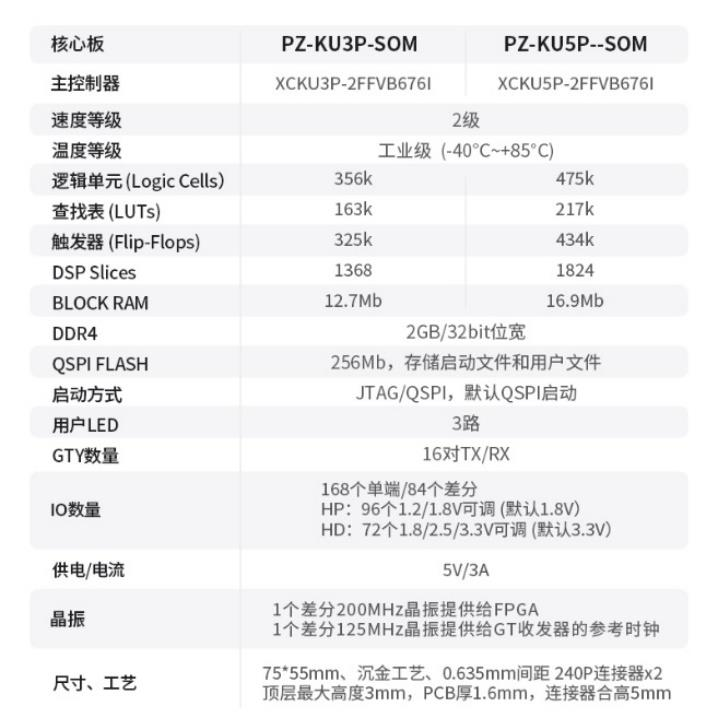

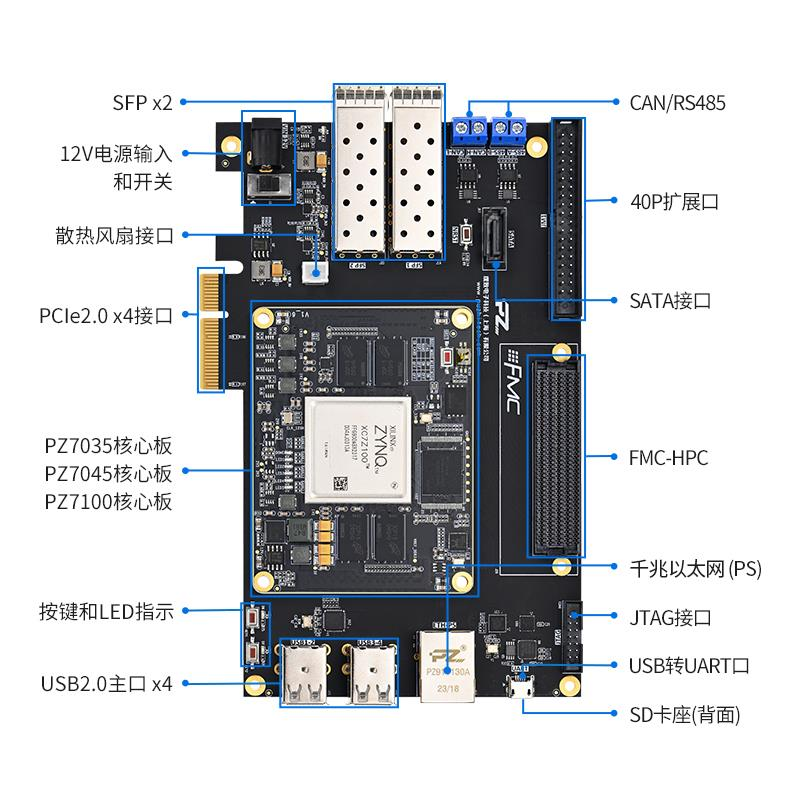

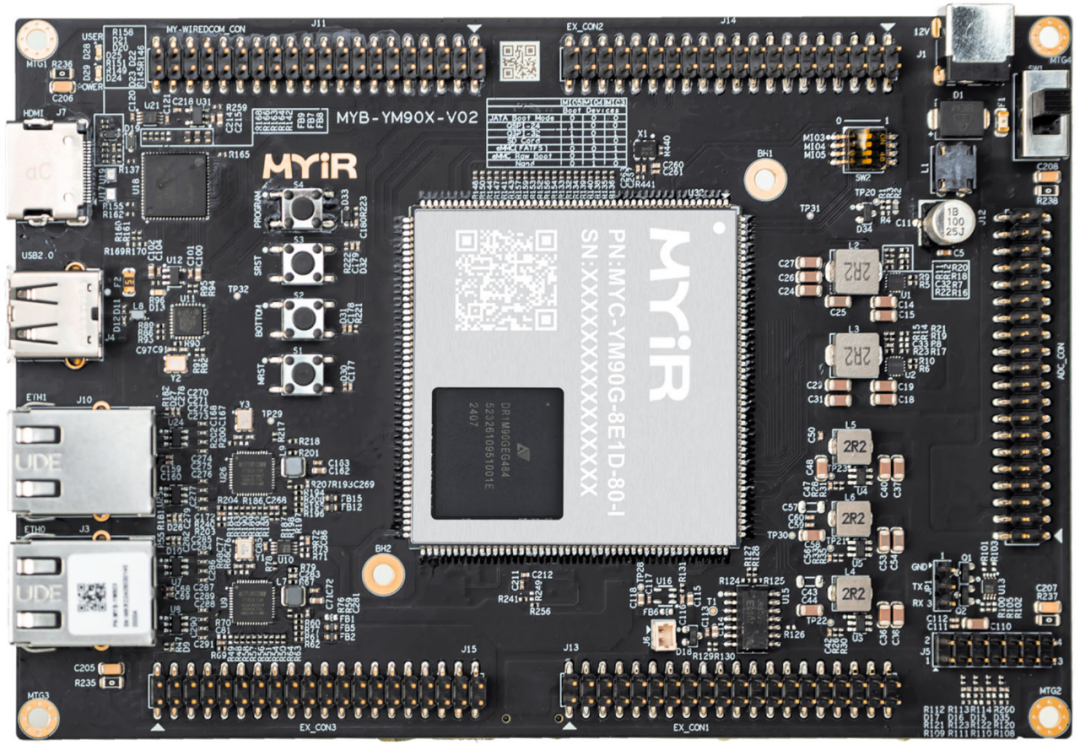

璞致電子科技 Kintex UltraScale+系列開發板提供了KU3P 和 KU5P 兩個兼 容版本,分別使用 XILINX 公司的 XCKU3P-2FFVB676I 和 XCKU5P-2FFVB676I 作為 主控制器。

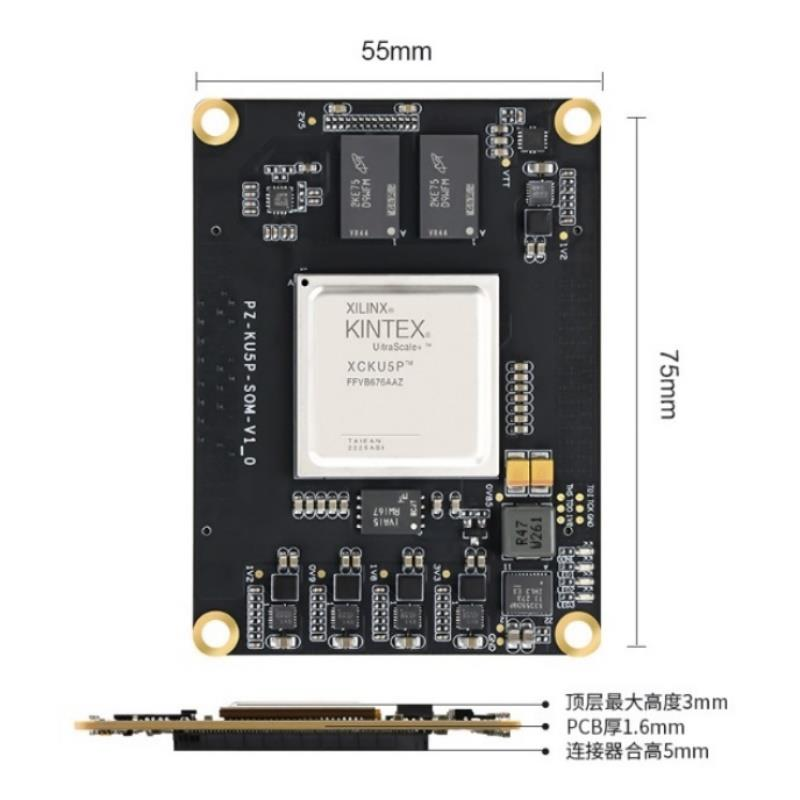

璞致電子科技 Kintex UltraScale+系列開發板以核心板加底板方式提供。核 心板通過兩個0.635mm 間距 240P 高速連接器扣接在底板上,使用上更加靈活。既 可以做學習使用,也可以使用核心板用于項目開發。

另外,開發板集成了豐富的外設資源,提供了詳盡的開發例程,加速了用 戶學習或者項目推進。除此之外,開發板還集成了 JTAG 調試器,做到了一根 USB 線和一根 12V 電源線就可以讓開發板工作起來,使用更加便捷。

關于核心板和開發板的詳細說明,可以查閱下文對應的核心板和底板章 節。

?編輯

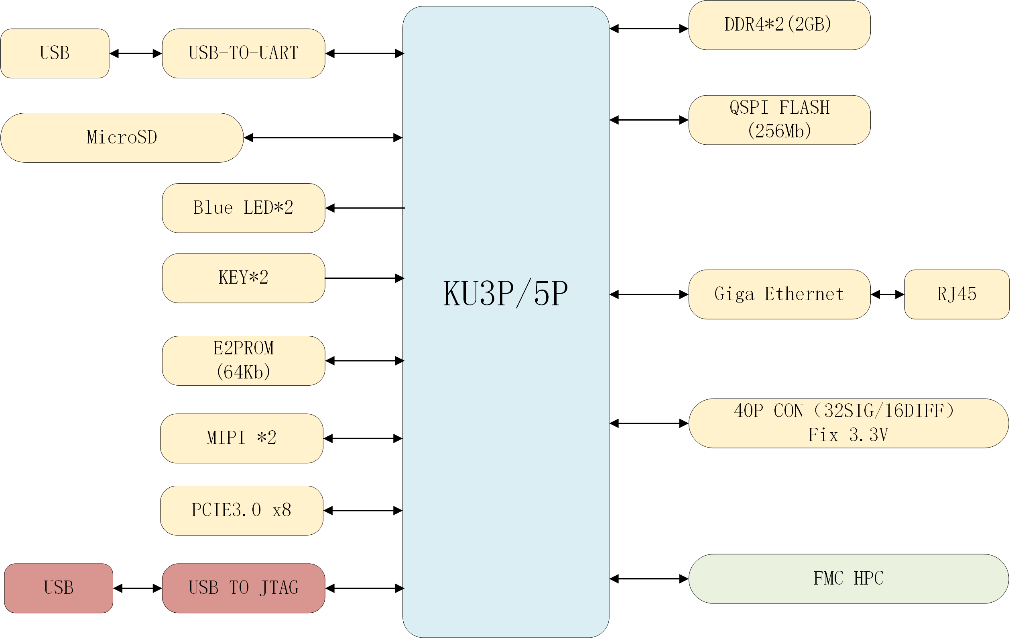

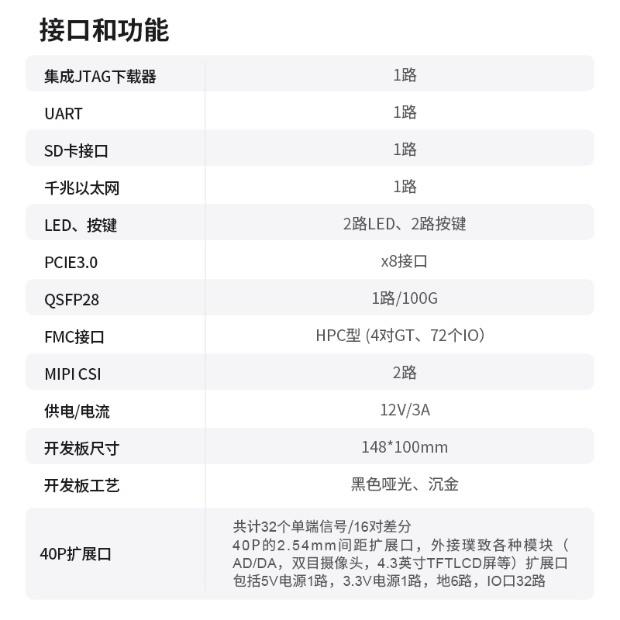

[]()2.2.開發板資源和框圖

如下分別為開發板的框圖和板載資源表,用戶可對比查看。

?編輯

?編輯

?編輯

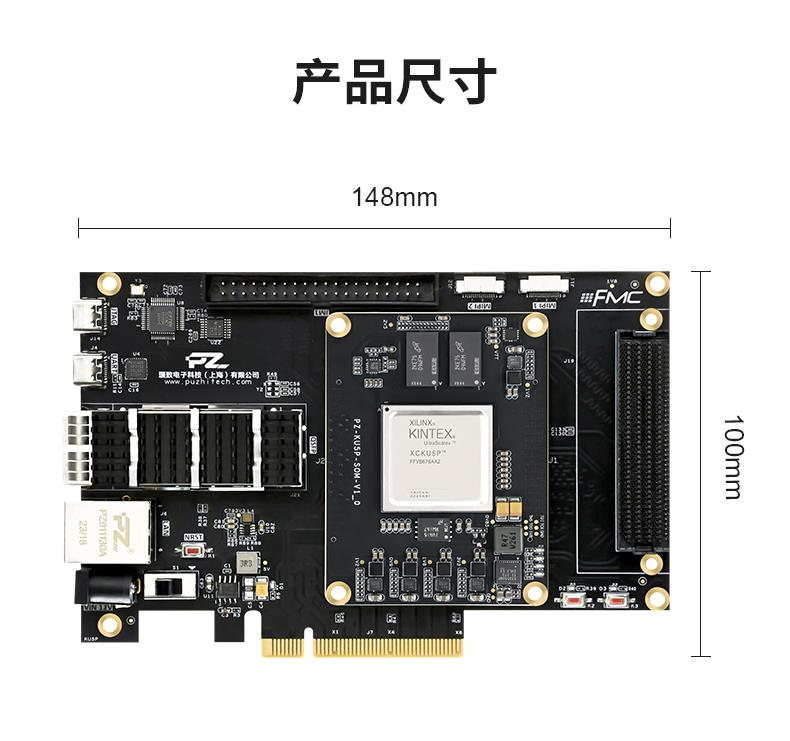

[]()2.3.開發板尺寸

如下圖標出開發板尺寸為 148x100mm,開發板的四個角各放置一個固定孔, 用于安裝支撐柱或固定單板,孔徑為 3.5mm。開發板配置了風扇、散熱片以及亞 克力防護板,為方便展示,并沒有安裝到開發板上,下圖列出了散熱片和風扇以 及對應尺寸。

?編輯

[]()[]()第三章: ****璞致 ****KintexUltraScale+核心板

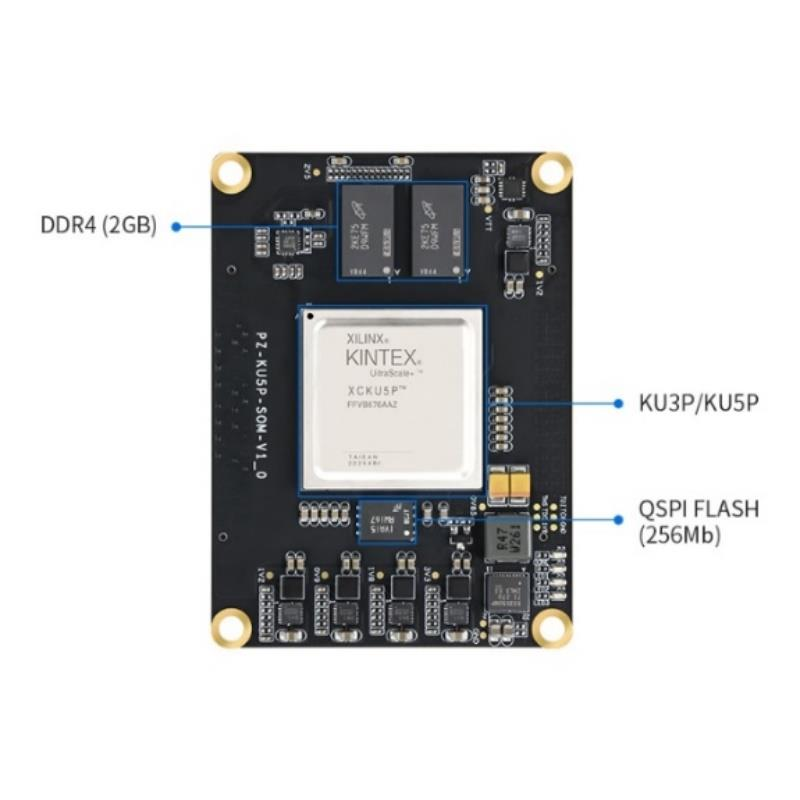

[]()3.1.核心板簡介

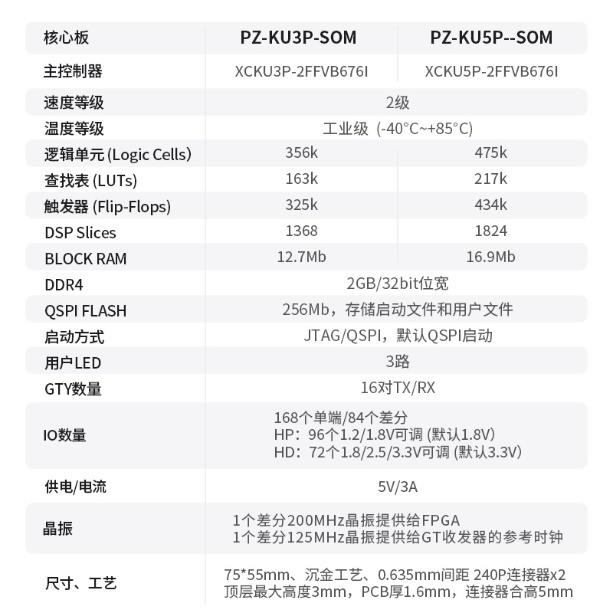

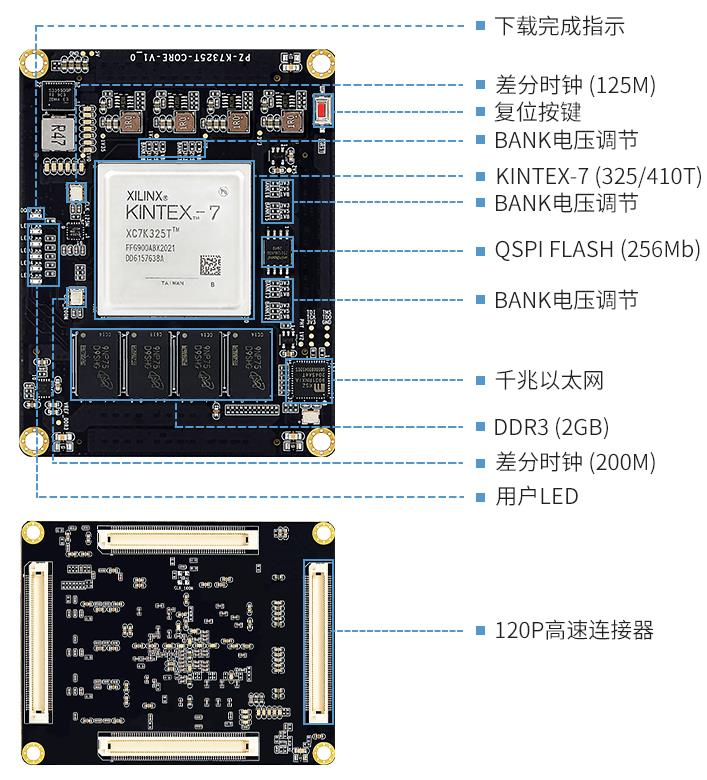

璞致 Kintex UltraScale+系列核心板提供了KU3P 和 KU5P 兩款,兩款資源 不同,接口完全兼容,通過更換核心板方式就可以實現資源升級,核心板管腳 完全兼容。如下圖詳細標注了核心板的功能模塊。

?編輯

?編輯

[]()3.2.核心板規格與尺寸

如下圖列出了核心板所有板載資源,通過下圖我們可以詳細對比兩款核心板差異: 主控芯片不同,外設資源相同。

?編輯

?編輯

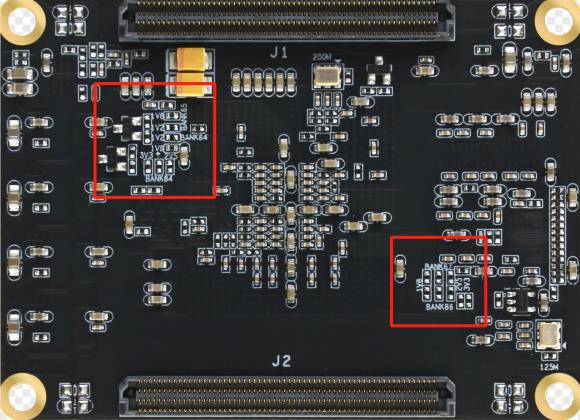

[]()3.3.核心板供電

核心板供電電壓是 5V,在核心板的兩個角都留有電源輸入管腳,電源管腳 在模塊內部已做了連通,此設計主要考慮用戶電源接入方向,哪個方向方便接 哪個,只需要接一個角就可以。電源連接需用銅皮連接且打足夠的過孔以保證 電源通流能力。核心板上的所有 GND 信號都需要連接到底板上,每個 GND 通過 兩個過孔與底板連接。因核心板邏輯使用量不同,核心板供電極限電流在

5V/3A,所以外部供電需要考慮極限電流情況以保證核心板工作穩定。

給模組供電的電源輸出電壓需要穩定,且需要考慮電源浪涌,核心板電源 輸入口需要加幾顆大電容(220UF/10V),可以加一級 DC2DC 芯片,確保供電穩 定。

?編輯

[]()3.4.核心板時鐘

核心板提供了兩路差分時鐘,頻率分別是 200M/125M,滿足了各種應用需 求。另外,125M 時鐘還加了時鐘緩沖器,可以實現板載時鐘和外部時鐘輸入切 換,當時鐘選擇信號不接地時鐘來源為差分晶振,當時鐘選擇信號接地時時鐘 來源為連接器外部輸入,如下圖詳細列出了時鐘連接的對應關系和管腳所在位 置,更詳細說明可參考璞致提供的核心板原理圖。

[]()3.5.核心板復位

考慮到最大限度的保留 IO 口引出到底板上,核心板上并沒有加復位按鍵,在開 發板上我們預留有復位按鍵,因為主控芯片是純 FPGA,所以任何一個 IO 接口都可以 當做邏輯的復位接口,用戶也可以自行定義復位接口。

[]()3.6.核心板啟動方式

主芯片的啟動模式分別是 JTAG、QSPI Flash,默認配置為 QSPI Flash 啟動,但 JTAG 模式優先級要高于 QSPI Flash,所以當用戶連接了 JTAG 接口芯片優先從 JTAG 啟動,不用做啟動模式切換。核心板上 QSPI Flash 容量為 256Mb,更詳細說明可參考 璞致提供的核心板原理圖。

[]() 3.7.BANK********接口電平選擇

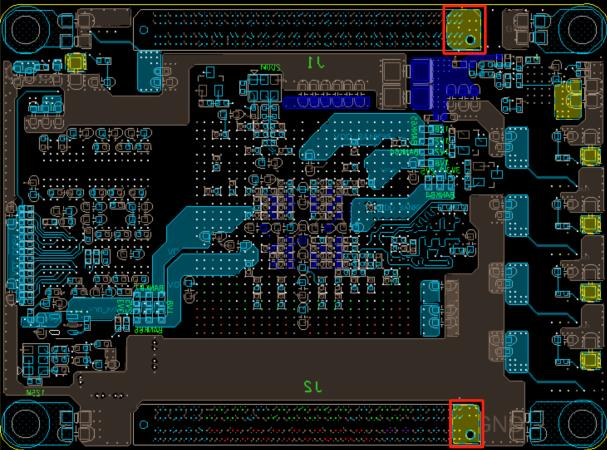

核心板上 BANK64/65 為 HP BANK,接口電平可以做 1.2/1.8V 調節,默認電平為 1.8V。BANK84/86/87 為 HD BANK,接口電平可以做 1.8/2.5/3.3V 調節,默認電平為 3.3V。核心板 BANK 電平的選擇可以通過電阻位置選焊來調節,對應的電阻標注位置 如下圖所示,精確位置參考核心板實物。

?編輯

[]()3.8.DDR4********資源

主芯片配置了兩顆 DDR4,單顆容量 1GB,兩顆共計容量為 2GB,DDR4 管腳分配參 見下表,更詳細信息可參考璞致提供的原理圖或者例程。

| DDR4********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DDR4_DQ0 | IO_L21P_T3L_N4_AD8P_67 | C23 |

| DDR4_DQ1 | IO_L24N_T3U_N11_67 | B22 |

| DDR4_DQ2 | IO_L23P_T3U_N8_67 | A24 |

| DDR4_DQ3 | IO_L24P_T3U_N10_67 | C22 |

| DDR4_DQ4 | IO_L21N_T3L_N5_AD8N_67 | B24 |

| DDR4_DQ5 | IO_L20N_T3L_N3_AD1N_67 | D21 |

|---|---|---|

| DDR4_DQ6 | IO_L23N_T3U_N9_67 | A25 |

| DDR4_DQ7 | IO_L20P_T3L_N2_AD1P_67 | E21 |

| DDR4_DM0 | IO_L19P_T3L_N0_DBC_AD9P_67 | A22 |

| DDR4_DQS_P0 | IO_L22P_T3U_N6_DBC_AD0P_67 | C21 |

| DDR4_DQS_N0 | IO_L22N_T3U_N7_DBC_AD0N_67 | B21 |

| DDR4_DQ8 | IO_L18P_T2U_N10_AD2P_67 | A19 |

| DDR4_DQ9 | IO_L15N_T2L_N5_AD11N_67 | B17 |

| DDR4_DQ10 | IO_L18N_T2U_N11_AD2N_67 | A20 |

| DDR4_DQ11 | IO_L15P_T2L_N4_AD11P_67 | C17 |

| DDR4_DQ12 | IO_L14N_T2L_N3_GC_67 | B20 |

| DDR4_DQ13 | IO_L17P_T2U_N8_AD10P_67 | B15 |

| DDR4_DQ14 | IO_L14P_T2L_N2_GC_67 | B19 |

| DDR4_DQ15 | IO_L17N_T2U_N9_AD10N_67 | A15 |

| DDR4_DM1 | IO_L13P_T2L_N0_GC_QBC_67 | C18 |

| DDR4_DQS_P1 | IO_L16P_T2U_N6_QBC_AD3P_67 | A17 |

| DDR4_DQS_N1 | IO_L16N_T2U_N7_QBC_AD3N_67 | A18 |

| DDR4_DQ16 | IO_L12P_T1U_N10_GC_67 | D19 |

| DDR4_DQ17 | IO_L8N_T1L_N3_AD5N_67 | F19 |

| DDR4_DQ18 | IO_L12N_T1U_N11_GC_67 | D20 |

| DDR4_DQ19 | IO_L9P_T1L_N4_AD12P_67 | G20 |

| DDR4_DQ20 | IO_L9N_T1L_N5_AD12N_67 | G21 |

| DDR4_DQ21 | IO_L8P_T1L_N2_AD5P_67 | F18 |

| DDR4_DQ22 | IO_L11N_T1U_N9_GC_67 | D18 |

| DDR4_DQ23 | IO_L11P_T1U_N8_GC_67 | E18 |

| DDR4_DM2 | IO_L7P_T1L_N0_QBC_AD13P_67 | H18 |

| DDR4_DQS_P2 | IO_L10P_T1U_N6_QBC_AD4P_67 | F20 |

| DDR4_DQS_N2 | IO_L10N_T1U_N7_QBC_AD4N_67 | E20 |

| DDR4_DQ24 | IO_L3P_T0L_N4_AD15P_67 | E15 |

| DDR4_DQ25 | IO_L5N_T0U_N9_AD14N_67 | G16 |

| DDR4_DQ26 | IO_L3N_T0L_N5_AD15N_67 | D15 |

| DDR4_DQ27 | IO_L2N_T0L_N3_67 | G17 |

| DDR4_DQ28 | IO_L6P_T0U_N10_AD6P_67 | D16 |

| DDR4_DQ29 | IO_L2P_T0L_N2_67 | H17 |

| DDR4_DQ30 | IO_L6N_T0U_N11_AD6N_67 | C16 |

| DDR4_DQ31 | IO_L5P_T0U_N8_AD14P_67 | H16 |

| DDR4_DM3 | IO_L1P_T0L_N0_DBC_67 | G15 |

| DDR4_DQS_P3 | IO_L4P_T0U_N6_DBC_AD7P_67 | E16 |

| DDR4_DQS_N3 | IO_L4N_T0U_N7_DBC_AD7N_67 | E17 |

| DDR4_A0 | IO_L20P_T3L_N2_AD1P_66 | F23 |

| DDR4_A1 | IO_L21N_T3L_N5_AD8N_66 | D25 |

| DDR4_A2 | IO_L22P_T3U_N6_DBC_AD0P_66 | D23 |

| DDR4_A3 | IO_L24N_T3U_N11_66 | B26 |

| DDR4_A4 | IO_L20N_T3L_N3_AD1N_66 | E23 |

|---|---|---|

| DDR4_A5 | IO_L23N_T3U_N9_66 | C26 |

| DDR4_A6 | IO_L16P_T2U_N6_QBC_AD3P_66 | F24 |

| DDR4_A7 | IO_L23P_T3U_N8_66 | D26 |

| DDR4_A8 | IO_L17P_T2U_N8_AD10P_66 | H26 |

| DDR4_A9 | IO_L19P_T3L_N0_DBC_AD9P_66 | E25 |

| DDR4_A10 | IO_L22N_T3U_N7_DBC_AD0N_66 | C24 |

| DDR4_A11 | IO_T3U_N12_66 | F22 |

| DDR4_A12 | IO_L24P_T3U_N10_66 | B25 |

| DDR4_A13 | IO_L19N_T3L_N1_DBC_AD9N_66 | E26 |

| DDR4_A14 | IO_L21P_T3L_N4_AD8P_66 | D24 |

| DDR4_A15 | IO_L12P_T1U_N10_GC_66 | J23 |

| DDR4_A16 | IO_T2U_N12_66 | G22 |

| DDR4_A17 | IO_L16N_T2U_N7_QBC_AD3N_66 | F25 |

| DDR4_BA0 | IO_L15P_T2L_N4_AD11P_66 | J25 |

| DDR4_BA1 | IO_L18P_T2U_N10_AD2P_66 | H21 |

| DDR4_BG0 | IO_L17N_T2U_N9_AD10N_66 | G26 |

| DDR4_nCS | IO_L14P_T2L_N2_GC_66 | H23 |

| DDR4_ODT | IO_T1U_N12_66 | M24 |

| DDR4_nRESET | IO_L10N_T1U_N7_QBC_AD4N_66 | L25 |

| DDR4_CLK_P | IO_L13P_T2L_N0_GC_QBC_66 | G24 |

| DDR4_CLK_N | IO_L13N_T2L_N1_GC_QBC_66 | G25 |

| DDR4_CKE | IO_L14N_T2L_N3_GC_66 | H24 |

| DDR4_nACT | IO_L10P_T1U_N6_QBC_AD4P_66 | L24 |

| DDR4_nALERT | IO_L18N_T2U_N11_AD2N_66 | H22 |

| DDR4_PARITY | IO_L15N_T2L_N5_AD11N_66 | J26 |

[]()3.9.核心板信號與等長

核心板引出到連接器的信號都做了嚴格等長,可以參考璞致提供的信號等長表格, 里面詳細列出了信號名稱和信號走線長度,表格已存放在對應的文件夾下 。。

[]()3.10.核心板封裝庫

為方便用戶快速使用核心板,我們提供了對應的封裝庫,連接器相對位置和核心 板外框絲印都已擺放好,直接調用即可。原理圖封裝提供 AD/ORCAD 兩個版本,PCB 封 裝提供 AD/Allegro 兩個版本,均已存放在對應的文件夾下。另外,文件夾下提供了核 心板的 DXF 文件,方便用戶對應結構。

13 / 25

[]()3.11.核心板對應連接器

核心板采用了兩個高密連接器與底板連接,底板上使用的連接器對應型號是 ADM6-60-01.5-L-4-2-A-TR,用戶可以自行購買,也可以聯系璞致客服購買。

[]()****[]()第四章 璞致 ****KintexUltraScale+底板

前面章節我們詳細介紹了核心板資源,本章節我們將詳細介紹開發板對應底板所 搭載的資源。

[]()4.1.開發板供電

開發板有兩種供電方式,璞致提供的 12V/3A 的適配器供電或者通過 PCIE 供電, 兩種供電方式可以通過 S1 開關來切換。電源接入后通過 DCDC 轉換成 3.3V、1.8V 等 多路電壓供板內器件使用。電源部分詳細電路可參考開發板對應的原理圖。

?編輯

[]()4.2.時鐘電路

時鐘電路主要集中在核心板上,可以參考核心板時鐘部分說明。

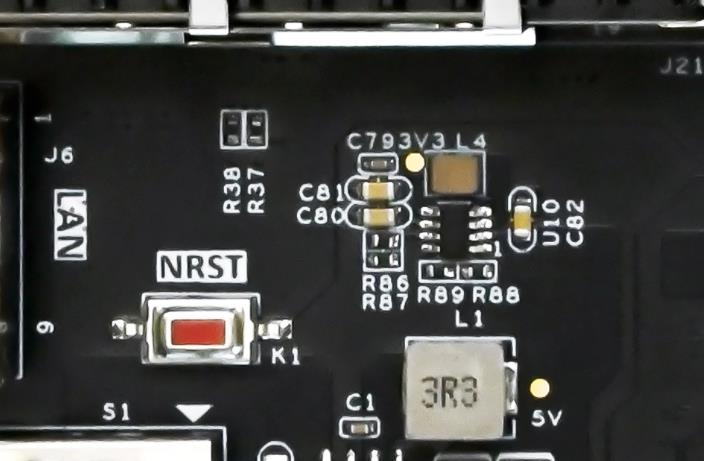

[]()4.3.復位電路

在開發板上預留了一個復位按鍵,按鍵默認高電平,按下后為低電平。

復位管腳連接到 BANK84 的 IO_4N_84(AD14)管腳,管腳電平為 3.3V。復位部分詳 細電路可參考開發板原理圖。

?編輯

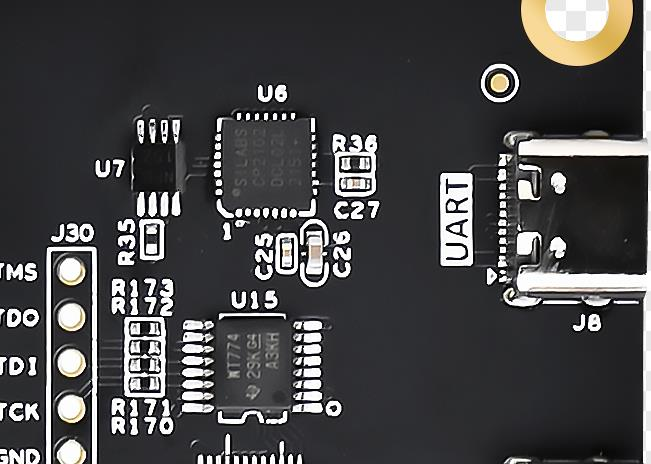

[]() 4.4.USB********轉串口

開發板使用 Silicon Labs CP2102GM 芯片實現 USB 轉 UART, USB 接口采用 TypeC 接口,用戶只要用一根 USB 線連接到 PC 上即可進行串口通信。

UART 的 TX/RX 信號與 FPGA 的 BANK84 相連,接口電平為 3.3V。 如下是信號對應 關系表和原理圖,TX/RX 方向為 FPGA 端定義。

| UART********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| UART_TX | IO_5P_84 | AC13 |

| UART_RX | IO_5N_84 | AC14 |

?編輯

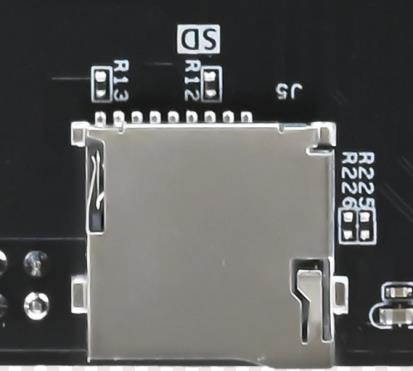

[]()4.5.SD********卡

開發板上放置了一個 SD 卡座(開發板背面), SD 卡信號連接到 FPGA 的 BANK87 上,接口電平為 3.3V。如下是信號對應關系,詳細電路可以參考開發板原理圖。

| SD********卡引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| SD-CLK | IO_10P_87 | C12 |

| SD-CMD | IO_10N_87 | B12 |

| SD-DATA0 | IO_5P_87 | G12 |

| SD-DATA1 | IO_5N_87 | F12 |

| SD-DATA2 | IO_6P_87 | F14 |

| SD-DATA3 | IO_6N_87 | F13 |

?編輯

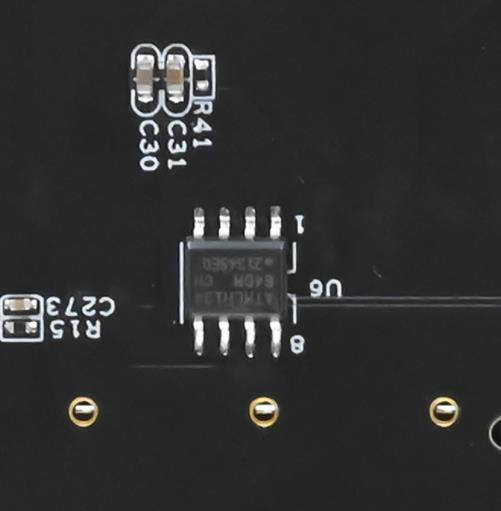

[]()4.6.E2********PROM

開發板上放置了一顆 64Kbit 的 EEPROM 芯片,型號為 AT24C64D-SSHM-T,E2PROM 通過 IIC 擴展芯片與 FPGA 的 BANK84 相連,接口電平為 3.3V。EEPROM 讀地址是 0xA1, 寫地址是 0xA0。操作代碼可參考璞致提供的例程,詳細電路可以參考開發板原理圖。

| E2********PROM | 管腳名稱 | 管腳位置 |

|---|---|---|

| E2PROM_I2C_SCL | IO_6P_84 | AB15 |

| E2PROM_I2C_SDA | IO_6N_84 | AB16 |

?編輯

[]()4.7.千兆以太網

開發板上設計了一路千兆以太網,以太網芯片與 FPGA 之間通過 RGMII 接 口互聯,連接 BANK65/87,接口電平是 1.8V,連接對應管腳見下表,網口地 址是 PHY_AD[2:0]=001,詳細電路可以參考開發板原理圖。

| RMGII********信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| GTX_CLK | IO_24P_65 | N21 |

| TX_EN | IO_24N_65 | N22 |

| TXD0 | IO_21P_65 | R20 |

| TXD1 | IO_21N_65 | R21 |

| TXD2 | IO_6P_65 | W19 |

| TXD3 | IO_6N_65 | W20 |

| RX_CLK | IO_11P_GC_65 | V23 |

|---|---|---|

| RX_DV | IO_11N_GC_65 | W23 |

| RXD0 | IO_18P_65 | R25 |

| RXD1 | IO_18N_65 | R26 |

| RXD2 | IO_15P_65 | N24 |

| RXD3 | IO_15N_65 | P24 |

| MDC | IO_11P_87 | A13 |

| MDIO | IO_11N_87 | A12 |

?編輯

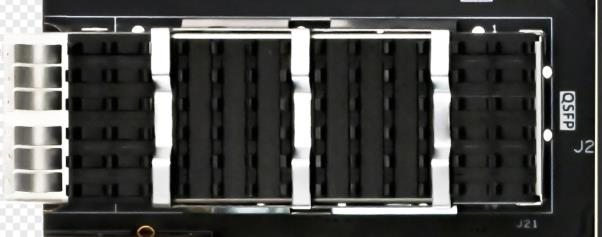

[]() 4.8.QSFP28接口

開發板上設計了一路 100G QSFP28 接口,接口信號與 FPGA 的 BANK84/BANK226 相 連,詳細可參考原理圖。

如下是 QSFP28 的引腳分配, 詳細電路可以參考開發板原理圖。

| QSFP********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| QSFP1-TX-P0 | MGT_TX_P0_226 | N5 |

| QSFP1-TX-N0 | MGT_TX_N0_226 | N4 |

| QSFP1-TX-P1 | MGT_TX_P1_226 | L5 |

| QSFP1-TX-N1 | MGT_TX_N1_226 | L4 |

| QSFP1-TX-P2 | MGT_TX_P2_226 | J5 |

| QSFP1-TX-N2 | MGT_TX_N2_226 | J4 |

| QSFP1-TX-P3 | MGT_TX_P3_226 | G5 |

| QSFP1-TX-N3 | MGT_TX_N3_226 | G4 |

| QSFP1-RX-P0 | MGT_RX_P0_226 | M2 |

| QSFP1-RX-N0 | MGT_RX_N0_226 | M1 |

| QSFP1-RX-P1 | MGT_RX_P1_226 | K2 |

| QSFP1-RX-N1 | MGT_RX_N1_226 | K1 |

| QSFP1-RX-P2 | MGT_RX_P2_226 | H2 |

| QSFP1-RX-N2 | MGT_RX_N2_226 | H1 |

| QSFP1-RX-P3 | MGT_RX_P3_226 | F2 |

| QSFP1-RX-N3 | MGT_RX_N3_226 | F1 |

| QSFP1_LPMODE | IO_10N_84 | W15 |

| QSFP1_I2C_SCL | IO_7P_84 | Y15 |

|---|---|---|

| QSFP1_I2C_SDA | IO_7N_84 | AA15 |

?編輯

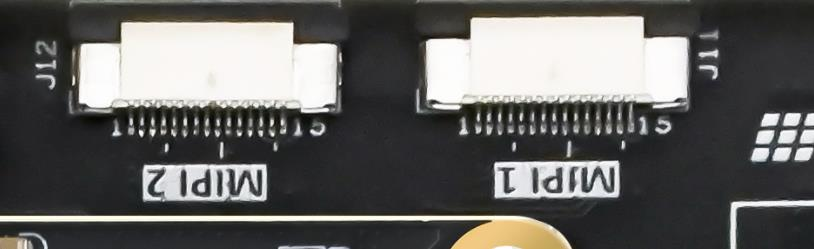

[]() 4.9.MIPI********接口

開發板設計了兩路 MIPI 接口,管腳定義如下表,詳細電路可以參考開發板原理 圖。

| MIPI1信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| MIPI1_D_P0 | IO_4P_65 | V21 |

| MIPI1_D_N0 | IO_4N_65 | V22 |

| MIPI1_D_P1 | IO_3P_65 | T20 |

| MIPI1_D_N1 | IO_3N_65 | U20 |

| MIPI1_CLK_P | IO_1P_65 | U19 |

| MIPI1_CLK_N | IO_1N_65 | V19 |

| CAM1_RST | IO_12N_87 | A14 |

| CAM1_CLK | IO_12P_87 | B14 |

| CAM1_SCL | IO_1P_87 | J12 |

| CAM1_SDA | IO_1N_87 | H12 |

| MIPI2信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| MIPI2_D_P0 | IO_20P_65 | P20 |

| MIPI2_D_N0 | IO_20N_65 | P21 |

| MIPI2_D_P1 | IO_23P_65 | N19 |

| MIPI2_D_N1 | IO_23N_65 | P19 |

| MIPI2_CLK_P | IO_22P_65 | N23 |

| MIPI2_CLK_N | IO_22N_65 | P23 |

| CAM2_RST | IO_L7N_HDGC_87 | E12 |

| CAM2_CLK | IO_L7P_HDGC_87 | E13 |

| CAM2_SCL | IO_L8P_HDGC_87 | D14 |

| CAM2_SDA | IO_L8N_HDGC_87 | D13 |

?編輯

[]()4.10.LED

開發板設計了兩路 LED。LED 高電平亮,低電平滅。詳細電路可參考開發板原理 圖。

| LED********位號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LED1 | IO-8P-84 | AA14 |

| LED2 | IO-8N-84 | AB14 |

?編輯

[]()4.11.按鍵

開發板設計了兩路用戶按鍵,一路復位按鍵。按鍵默認高電平,按下為低電平, 按鍵連到 PL 側,管腳位置如下表。

| 按鍵位號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| KEY1 | IO-2P-84 | AE13 |

| KEY2 | IO-2N-84 | AF13 |

| SYS_nRST | IO-4N-84 | AD14 |

?編輯

[]()4.12.40P********擴展口

開發板設計了一個 40P 2.54mm 間距的簡易牛角座,用于擴展信號的連接,信號 與 FPGA 的 BANK86/87 連接,電平為 3.3V。如下表標出了信號所在的芯片位置,詳細 連接關系參考原理圖部分。

| JM1信號順序 | 管腳名稱 | 管腳位置 | JM1信號順序 | 管腳名稱 | 管腳位置 |

|---|---|---|---|---|---|

| 5 | IO_L5P_HDGC_86 | G10 | 6 | IO_L7P_HDGC_86 | E11 |

| 7 | IO_L5N_HDGC _86 | G9 | 8 | IO_L7N_HDGC_86 | E10 |

| 9 | IO_L6P_HDGC _86 | F10 | 10 | IO_L8P_HDGC_86 | D11 |

| 11 | IO_L6N_HDGC _86 | F9 | 12 | IO_L8N_HDGC_86 | D10 |

| 13 | IO_L10P_86 | B9 | 14 | IO_L12P_86 | C11 |

| 15 | IO_L10N_86 | A9 | 16 | IO_L12N_86 | B11 |

| 17 | IO_L11P_86 | B10 | 18 | IO_L9P_86 | D9 |

| 19 | IO_L11N_86 | A10 | 20 | IO_L9N_86 | C9 |

| 21 | IO_L4P_86 | H11 | 22 | IO_L2P_86 | J11 |

| 23 | IO_L4N_86 | G11 | 24 | IO_L2N_86 | J10 |

| 25 | IO_L3P_86 | J9 | 26 | IO_L1P_86 | K10 |

| 27 | IO_L3N_86 | H9 | 28 | IO_L1N_86 | K9 |

| 29 | IO_L4P_87 | J15 | 30 | IO_L2P_87 | J13 |

| 31 | IO_L4N_87 | J14 | 32 | IO_L2N_87 | H13 |

| 37 | IO_L9P_87 | C14 | 38 | IO_L3P_87 | H14 |

| 39 | IO_L9N_87 | C13 | 40 | IO_L3N_87 | G14 |

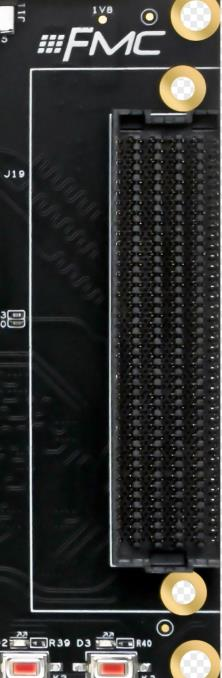

[]() 4.13.FMC********擴展接口

開發板上設計了一路 FMC-HPC 連接器,但因芯片管腳數量有限,實際并沒有全部 連接,只連接了 4 對 MGT 和 LA 信號,如下表列出了信號對應關系。詳細連接關系參 考原理圖部分。

21 / 25

| 序號 | FMC-HPC 管腳 | 管腳名稱 | 管腳位置 |

|---|---|---|---|

| A2 | DP1_M2C_P | MGT_RX_P1_227 | C4 |

| A3 | DP1_M2C_N | MGT_RX_N1_227 | C3 |

| A6 | DP2_M2C_P | MGT_RX_P2_227 | B2 |

| A7 | DP2_M2C_N | MGT_RX_N2_227 | B1 |

| A10 | DP3_M2C_P | MGT_RX_P3_227 | A4 |

| A11 | DP3_M2C_N | MGT_RX_N3_227 | A3 |

| A22 | DP1_C2M_P | MGT_TX_P1_227 | E5 |

| A23 | DP1_C2M_N | MGT_TX_N1_227 | E4 |

| A26 | DP2_C2M_P | MGT_TX_P2_227 | D7 |

| A27 | DP2_C2M_N | MGT_TX_N2_227 | D6 |

| A30 | DP3_C2M_P | MGT_TX_P3_227 | B7 |

| A31 | DP3_C2M_N | MGT_TX_N3_227 | B6 |

| B20 | GBTCLK1_M2C_P | MGT_CLK0_P_227 | K7 |

| B21 | GBTCLK1_M2C_N | MGT_CLK0_N_227 | K6 |

| C2 | DP0_C2M_P | MGT_TX_P0_227 | F7 |

| C3 | DP0_C2M_N | MGT_TX_N0_227 | F6 |

| C6 | DP0_M2C_P | MGT_RX_P0_227 | D2 |

| C7 | DP0_M2C_N | MGT_RX_N0_227 | D1 |

| C10 | LA06_P | IO_L3P_64 | AF24 |

| C11 | LA06_N | IO_L3N_64 | AF25 |

| C14 | LA10_P | IO_L6P_64 | AB24 |

| C15 | LA10_N | IO_L6N_64 | AC24 |

| C18 | LA14_P | IO_L23P_64 | Y17 |

| C19 | LA14_N | IO_L23N_64 | AA17 |

| C22 | LA18_P_CC | IO_L13P_MRCC_64 | AD20 |

| C23 | LA18_N_CC | IO_L13N_MRCC_64 | AE20 |

| C26 | LA27_P | IO_L16P_65 | U26 |

| C27 | LA27_N | IO_L16N_65 | V26 |

| C30 | SCL | IO_L11P_84 | Y13 |

| C31 | SDA | IO_L11N_84 | AA13 |

| D4 | GBTCLK0_M2C_P | MGT_CLK0_P_226 | P7 |

| D5 | GBTCLK0_M2C_N | MGT_CLK0_N_226 | P6 |

| D8 | LA01_P_CC | IO_L11P_SRCC_64 | AD21 |

| D9 | LA01_N_CC | IO_L11N_SRCC_64 | AE21 |

| D11 | LA05_P | IO_L1P_64 | AE25 |

| D12 | LA05_N | IO_L1N_64 | AE26 |

| D14 | LA09_P | IO_L2P_64 | AB25 |

| D15 | LA09_N | IO_L2N_64 | AB26 |

| D17 | LA13_P | IO_L24P_64 | Y18 |

| D18 | LA13_N | IO_L24N_64 | AA18 |

| D20 | LA17_P_CC | IO_L12P_MRCC_64 | AB21 |

| D21 | LA17_N_CC | IO_L12N_MRCC_64 | AC21 |

| D23 | LA23_P | IO_L9P_64 | AC22 |

| D24 | LA23_N | IO_L9N_64 | AC23 |

| D26 | LA26_P | IO_L10P_65 | W25 |

| D27 | LA26_N | IO_L10N_65 | W26 |

| G2 | CLK1_M2C_P | IO_L14P_SRCC_65 | T25 |

| G3 | CLK1_M2C_N | IO_L14N_SRCC_65 | U25 |

|---|---|---|---|

| G6 | LA00_P_CC | IO_L14P_SRCC_64 | AC19 |

| G7 | LA00_N_CC | IO_L14N_SRCC_64 | AD19 |

| G9 | LA03_P | IO_L18P_64 | AD16 |

| G10 | LA03_N | IO_L18N_64 | AE16 |

| G12 | LA08_P | IO_L7P_64 | AE22 |

| G13 | LA08_N | IO_L7N_64 | AF22 |

| G15 | LA12_P | IO_L8P_64 | AD23 |

| G16 | LA12_N | IO_L8N_64 | AE23 |

| G18 | LA16_P | IO_L5P_64 | AD24 |

| G19 | LA16_N | IO_L5N_64 | AD25 |

| G21 | LA20_P | IO_L4P_64 | AC26 |

| G22 | LA20_N | IO_L4N_64 | AD26 |

| G24 | LA22_P | IO_L19P_64 | Y20 |

| G25 | LA22_N | IO_L19N_64 | Y21 |

| G27 | LA25_P | IO_L5P_65 | T22 |

| G28 | LA25_N | IO_L5N_65 | T23 |

| G30 | LA29_P | IO_L1P_65 | U19 |

| G31 | LA29_N | IO_L1N_65 | V19 |

| G33 | LA31_P | IO_L4P_65 | V21 |

| G34 | LA31_N | IO_L4N_65 | V22 |

| G36 | LA33_P | IO_L8P_65 | Y25 |

| G37 | LA33_N | IO_L8N_65 | Y26 |

| H4 | CLK0_M2C_P | IO_L12P_MRCC_65 | V24 |

| H5 | CLK0_M2C_N | IO_L12N_MRCC_65 | W24 |

| H7 | LA02_P | IO_L17P_64 | AE17 |

| H8 | LA02_N | IO_L17N_64 | AF17 |

| H10 | LA04_P | IO_L15P_64 | AF18 |

| H11 | LA04_N | IO_L15N_64 | AF19 |

| H13 | LA07_P | IO_L16P_64 | AC18 |

| H14 | LA07_N | IO_L16N_64 | AD18 |

| H16 | LA11_P | IO_L22P_64 | AB17 |

| H17 | LA11_N | IO_L22N_64 | AC17 |

| H19 | LA15_P | IO_L20P_64 | AA19 |

| H20 | LA15_N | IO_L20N_64 | AB19 |

| H22 | LA19_P | IO_L21P_64 | AA20 |

| H23 | LA19_N | IO_L21N_64 | AB20 |

| H25 | LA21_P | IO_L10P_64 | AA22 |

| H26 | LA21_N | IO_L10N_64 | AB22 |

| H28 | LA24_P | IO_L7P_65 | Y22 |

| H29 | LA24_N | IO_L7N_65 | Y23 |

| H31 | LA28_P | IO_L9P_65 | AA24 |

| H32 | LA28_N | IO_L9N_65 | AA25 |

| H34 | LA30_P | IO_L2P_65 | U21 |

| H35 | LA30_N | IO_L2N_65 | U22 |

| H37 | LA32_P | IO_L3P_65 | T20 |

| H38 | LA32_N | IO_L3N_65 | U20 |

?編輯

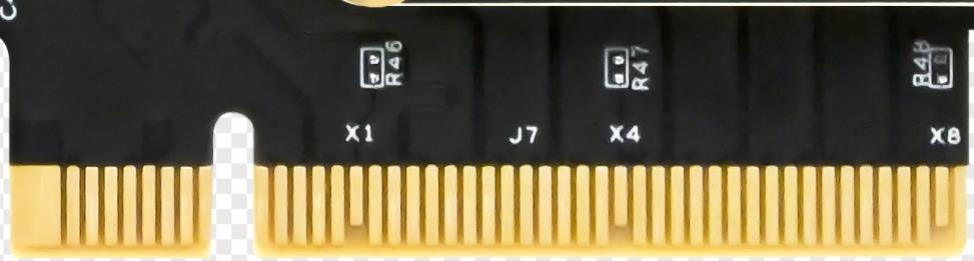

[]()4.14.PCIE3.0********接口

開發板板載了 PCIE3.0 接口,為 X8 接口,如下表列出了PCIE 接口對應關系。

| PCIE********3.0 | 管腳名稱 | 管腳位置 |

|---|---|---|

| PERST_N | IO_4P_84 | AD13 |

| REF_CLK_P | MGT_CLK_P0_224 | AB7 |

| REF_CLK_N | MGT_CLK_N0_224 | AB6 |

| PER0_P | MGT_TX_P0_224 | AF7 |

| PER0_N | MGT_TX_N0_224 | AF6 |

| PER1_P | MGT_TX_P1_224 | AE9 |

| PER1_N | MGT_TX_N1_224 | AE8 |

| PER2_P | MGT_TX_P2_224 | AD7 |

| PER2_N | MGT_TX_N2_224 | AD6 |

| PER3_P | MGT_TX_P3_224 | AC5 |

| PER3_N | MGT_TX_N3_224 | AC4 |

| PER4_P | MGT_TX_P0_225 | AA5 |

| PER4_N | MGT_TX_N0_225 | AA4 |

| PER5_P | MGT_TX_P1_225 | W5 |

| PER5_N | MGT_TX_N1_225 | W4 |

| PER6_P | MGT_TX_P2_225 | U5 |

| PER6_N | MGT_TX_N2_225 | U4 |

| PER7_P | MGT_TX_P3_225 | R5 |

| PER7_N | MGT_TX_N3_225 | R4 |

| PET0_P | MGT_RX_P0_224 | AF2 |

| PET0_N | MGT_RX_N0_224 | AF1 |

| PET1_P | MGT_RX_P1_224 | AE4 |

| PET1_N | MGT_RX_N1_224 | AE3 |

| PET2_P | MGT_RX_P2_224 | AD2 |

| PET2_N | MGT_RX_N2_224 | AD1 |

|---|---|---|

| PET3_P | MGT_RX_P3_224 | AB2 |

| PET3_N | MGT_RX_N3_224 | AB1 |

| PET4_P | MGT_RX_P0_225 | Y2 |

| PET4_N | MGT_RX_N0_225 | Y1 |

| PET5_P | MGT_RX_P1_225 | V2 |

| PET5_N | MGT_RX_N1_225 | V1 |

| PET6_P | MGT_RX_P2_225 | T2 |

| PET6_N | MGT_RX_N2_225 | T1 |

| PET7_P | MGT_RX_P3_225 | P2 |

| PET7_N | MGT_RX_N3_225 | P1 |

?編輯

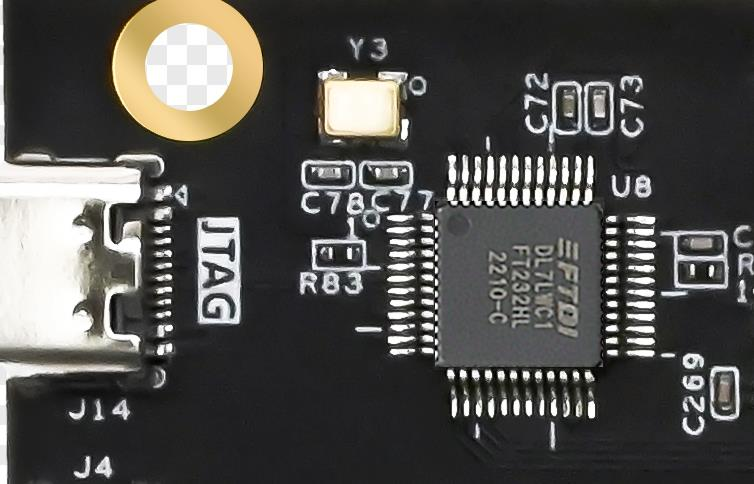

[]() 4.15.USB轉JTAG********下載器

開發板板載了一個 USB 轉 JTAG 下載器,安裝好 Vivado 軟件后使用USB 線連接好 JTAG 對應的 USB 口,即可實現調試下載,非常方便。如下是接口在開發板上的位置 圖。

?編輯

?審核編輯 黃宇

-

FPGA

+關注

關注

1662文章

22470瀏覽量

638240 -

Xilinx

+關注

關注

73文章

2204瀏覽量

131694 -

開發板

+關注

關注

26文章

6359瀏覽量

119868

發布評論請先 登錄

ESP32-P4全功能開發板和ESP32-P4-TINY開發板該怎么選?看這篇就夠了!

FPGA開發板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用說明 XILINX核心板簡介

fpga開發板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發板用戶手冊

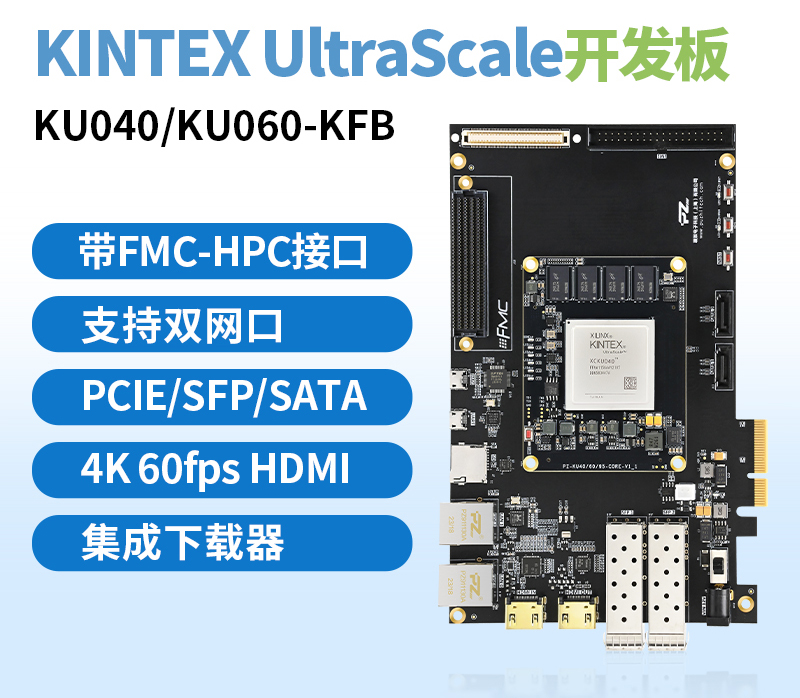

Kintex UltraScale 純 FPGA 開發平臺,釋放高速并行計算潛能,高性價比的 FPGA 解決方案

【PZ7020-StarLite 入門級開發板】——FPGA 開發的理想起點,入門與工業場景的雙重優選

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發平臺

PZ/璞致【PZ-ZU19EG-KFB】—ZYNQ UltraScale + 賦能異構計算與高性能嵌入式系統開發

fpga開發板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開發板用戶手冊

fpga開發板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開發板用戶手冊

評論