以下文章來源于數字站

本文旨在通過講解不同模式的原理圖連接方式,進而配置用到引腳的含義(手冊上相關引腳含義有四、五頁,通過本文理解基本上能夠記住所有引腳含義以及使用場景),熟悉xilinx 7系列配置流程,以及設計原理圖時需要注意的一些事項,比如flash與FPGA的上電時序。

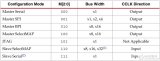

xilinx配置相關的引腳主要集中在bank0,bank14、bank15也存在一些輔助配置引腳,配置的模式主要由bank0上面的M[2:0]三個引腳的狀態決定,總共存在7種不同的配置方式(因為M[2:0]=3’b011不存在),因為M[2:0]三個引腳內部有上拉電阻,所以默認是從串行配置模式(3'b111),配置模式如下表1所示。

表1 配置模式

| 配置模式 | M[2:0] | 總線位寬 | CCLK方向 |

| Master Serial | 000 | X1 | 輸出 |

| Master SPI | 001 | X1,X2,X4 | 輸出 |

| Master BPI | 010 | X8,X16 | 輸出 |

| Master SelectMAP | 100 | X8,X16 | 輸出 |

| JTAG(only) | 101 | X1 | 無效 |

| Slave SelectMAP | 110 | X8,X16,X32 | 輸入 |

| Slave Serial | 111 | X1 | 輸入 |

注意:如果M[2:0]為101,則該FPGA只支持JTAG進行配置。處于其余配置模式下時,依舊可以使用JTAG模式進行調試,并且優先級最高。

一般必然存在的JTAG調試模式,另外使用較多的是主SPI模式和從串行配置模式,后面主要講解這幾種配置,其余并行配置模式由于消耗引腳較多,一般不會使用,與這幾種串行模式的區別僅在于數據引腳的區別,需要了解的可以自行查看ug470手冊,下載地址如下,或者在后臺回復ug470即可獲取。

xilinx.com/content/dam/xilinx/support/documents/user_guides/ug470_7Series_Config.pdf

不同模式只有一些用于傳輸數據的引腳不同,都會使用一些相同的控制信號,并且在不同模式下這些信號功能基本一致。

01共用控制信號

01CFGBVS引腳

bank0電壓范圍選擇引腳,該引腳用于確定bank0的供電電源的范圍,如果該引腳接VCC,則bank0使用2.5V或者3.3V供電,如果接GND,則bank0供電電壓小于等于1.8V。如下圖所示,CFGBVS接高電平3.3V,則bank0的供電電壓VCC_0_1和VCC_0_2均接3.3V。當然可以加上拉和下拉電阻。

圖1 bank0電壓配置

02PROGRAM_B引腳

這個引腳可以清除FPGA內部的所有配置信息,讓FPGA回到配置狀態,重新進行配置,低電平有效。但注意在上電時把PROGRAM_B 保持為低電平不會使 FPGA 配置保持復位狀態,延遲配置的時間需要使用INIT_B信號配合完成,后續講解上電配置時詳細說明。PROGRAM_B 引腳外部需要通過4.7KΩ以上的電阻上拉至VCC。相關連接如圖1所示原理圖中該管腳外部通過4.7KΩ上拉電阻接到VCC,并且將該信號引出,便于其他控制器可以控制ARM的配置。

03INIT_B引腳

FPGA 初始化引腳或配置錯誤信號,低電平有效。當 FPGA 處于配置復位狀態或當 FPGA 正在初始化(清除)其配置存儲器(PROGRAM_B信號為低電平)時或當 FPGA 檢測到配置錯誤時,FPGA 會將該引腳驅動為低電平。在上電期間,可以通過將該引腳拉低,來延遲上電配置程序的時間。當完成初始化后,該引腳被釋放,外部上拉電阻將該引腳拉高,當檢測到該信號上升沿之后,FPGA會讀取M[2:0]引腳狀態,從而確定后續采用哪種配置方式進行配置。故該引腳外部也需要通過4.7KΩ的電阻上拉到VCC。

04DONE引腳

該信號高電平表示FPGA配置序列完成,默認情況下,該引腳為開漏輸出,內部有一個不大于10KΩ的上拉電阻,外部只需要通過一個330Ω的電阻上拉即可。

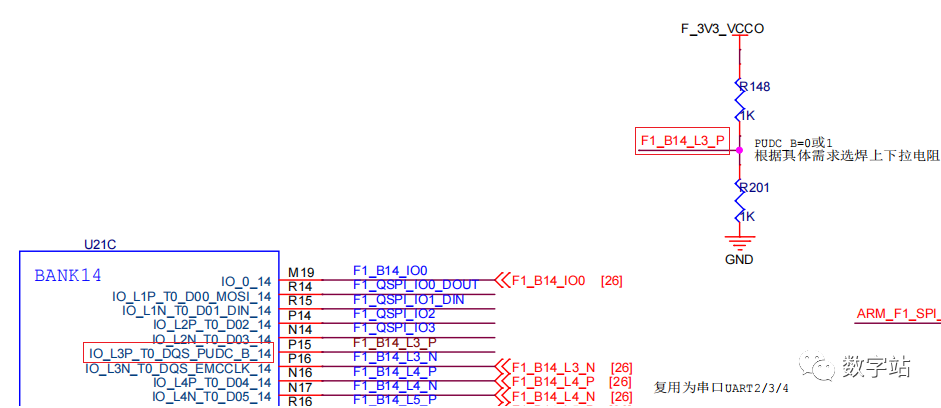

05PUDC_B引腳

該引腳的狀態決定在配置期間非專用配置IO的狀態,如果該引腳接高電平,則這部分IO設置為高阻態,如果該引腳為低電平,則這部分引腳被上拉輸出高電平。該引腳外部通過1KΩ電阻上拉到VCCO_14或者下拉到GND。注意該引腳不能懸空,連接如圖2所示。

圖2 pudc_b信號上下拉配置

06VCCBATT引腳

該引腳是FPGA內部易失性存儲器的電池備用電源,用于存儲AES解密器的密鑰,如果不需要使用AES易失性密鑰存儲區域中的解密器密鑰,那么將該引腳接地就行,該引腳不是I/O,不受VCCO_0的影響。了解該引腳功能即可,一般都用作接地處理。

不管采用何種配置方式,上述5個信號均具有相同功能,并且必須進行設置,不能懸空處理,接下來就可以看一下具體的上電配置流程,同樣,不管是何種配置方式,上電配置流程均相同,配置模式只能影響接收發送數據的方式。

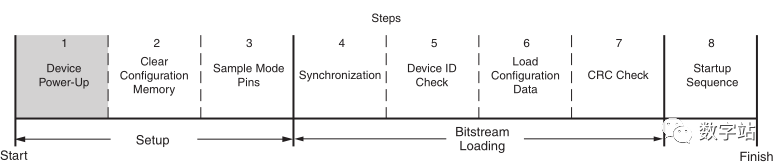

02配置流程

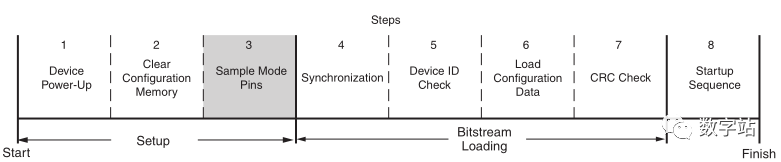

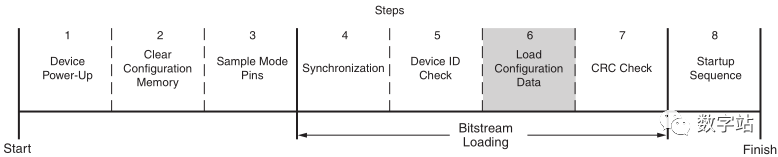

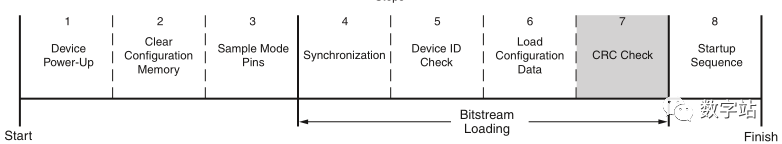

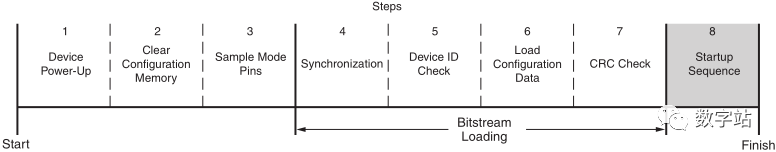

配置流程包含三個大步驟(復位,加載程序,初始化啟動),分為8個小步驟,如圖3所示:

圖3 7系列FPGA配置步驟

01設備上電

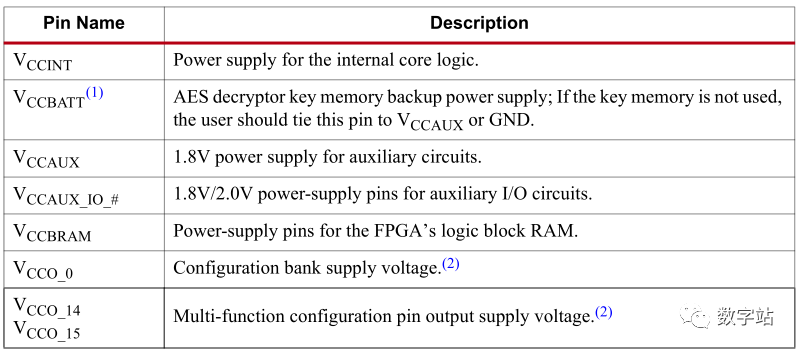

這部分主要涉及到不同電源軌上電時序的要求,不同系列上電要求不一致,需要參考對應手冊的上電時序。電源的種類如圖4所示。

圖4 電源種類

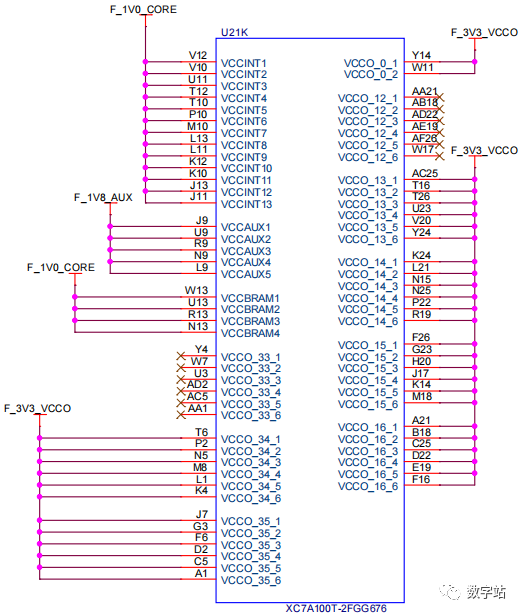

上圖對應的電源種類一般位于電源bank上,原理圖如圖5所示,Vccint為內核電源,另外有給AES加密和BRAM供電的電源,還有bank0的供電電源,ban14和bank15輔助配置供電電源,最后還有各個IO bank供電引腳。

圖5 電源bank

02清除配置內存

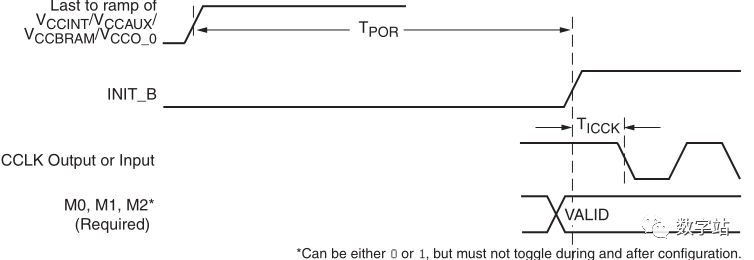

如圖6所示,在上電期間,program_b引腳拉低,FPGA的配置存儲器按順序清零,BRAM被重置為初始狀態,觸發器通過全局置位(GSR)重置被初始化。在此期間,除了少數配置引腳之外,其余IO通過全局三態將I/O置為高阻態,如果pudg_b為低電平,則這些IO內部上拉電阻使能,輸出高電平。上電配置時,init_b信號在初始化期間被內部驅動輸出低電平,經過Tpor時間后釋放。

圖6 上電清除時序

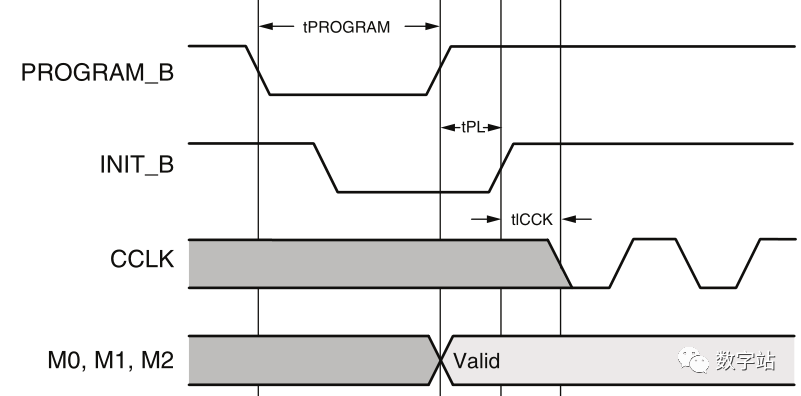

如果不是上電,其余情況的初始化如圖7所示,將program_b引腳拉低,初始化配置存儲器,持續時間由Tprogram決定。一直把program_b信號拉低是無法讓FPGA停留在初始化過程的,想要停留在這個過程中只能通過把init_b信號保持為低電平來實現延遲初始化過程。如果init_b引腳外部保持低電平,則器件在初始化過程中等待,直到引腳釋放,滿足TpoR或TPL延遲。

圖7 上電配置復位時序

這里需要注意一個上電順序的點:

上電時,FPGA會自動開始其配置過程,當FPGA處于主機串行SPI配置模式時,FPGA將FCS_B置為低電平,選擇SPI閃存,并向SPI閃存發送讀取命令。在FPGA將FCS_B驅動為低電平并發送讀取命令之前,SPI閃存必須處于喚醒狀態并準備好接收命令。

由于不同的電源軌可以為FPGA和SPI閃存供電,或者因為FPGA和SPI閃存可以沿著共享電源的斜坡在不同的時間做出響應,因此必須特別注意FPGA和SPI閃存的上電順序或上電斜坡。上電順序或電源斜坡可能會導致FPGA在Flash完全上電之前啟動,反之亦然。此外,一些SPI閃存設備指定了一個最短時間段,該時間段從通電開始可能是幾毫秒,在此期間不得選擇該設備。對于許多具有近乎同時的電源斜坡的系統,FPGA上電重置時間(TpoR)可以充分延遲FPGA配置過程的開始,使得SPI閃存在FPGA配置過程開始之前就準備好了。一般系統設計必須考慮電源順序、電源斜坡、FPGA上電復位時序和SPI閃存上電時序對開始配置和SPI閃存就緒之間的時序關系的影響。

03采樣模式引腳狀態

圖8 采樣模式引腳

在init_b引腳上升沿時,FPGA采集模式引腳M[2:0]的狀態,確定采用何種配置模式,如果是主機模式,則開始驅動CCLK輸出時鐘信號,之后FPGA在CCLK時鐘的上升沿采集數據輸入引腳的數據。BPI和SelectMAP模式,總線寬度初始為8,在總線寬度檢測序列之后,更新狀態寄存器,更新到對應的總線寬度。

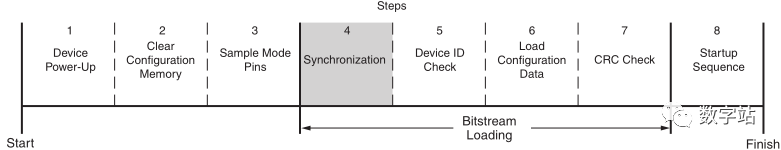

04Synchronization

圖9 自動檢測位寬

對于BPI、Slave SelectMAP和Master SelectMAP這些并行模式,狀態寄存器默認使用8位總線,需要經過自動檢測之后,才能夠確定其使用總線的具體位寬,所以在初始化之后,在傳輸配置數據之前,要確定具體的總線位寬。從機串口、主機串口、SPI和JTAG模式會忽略總線寬度檢測模式。

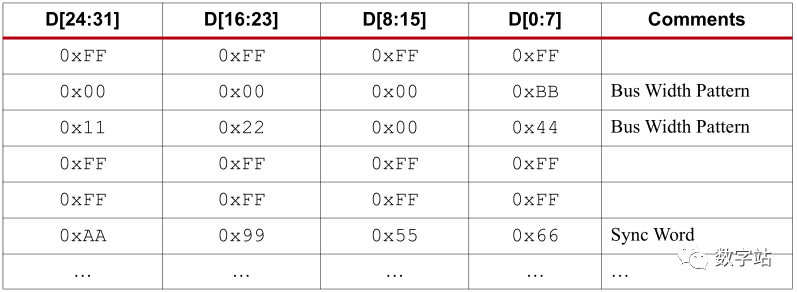

自動檢測總線位寬的方式

Xilinx工具生成的所有配置文件都包括總線寬度自動檢測模式,如果模式引腳設置為主機串行、從機串行、JTAG或SPI模式,則配置邏輯會忽略這些模式。FPGA其實是通過2個32位的數據來判斷總線位寬的,如下表所示,根據總線低8位數據狀態來確定總線實際位寬,如果第一次檢測低八位數據為0xBB,第二次檢測到數據為0x11,則該總線每次傳輸八位數據,即總線位寬為8位。如果第一次檢測數據為0xBB,第二次檢測數據為0x22,則總線每次傳輸16位數據,即總線位寬為16位。如果第一次檢測為0xBB,第二次檢測數據為0x44,則總線每次傳輸32位數據,即總線位寬為32位。

如果0xBB之后的數據不是0x11、0x22或0x44,則會重新檢測下一個0xBB,直到找到有效序列為止。確認外部總線寬度后,切換到對應的總線寬度并鎖定。

表2 自動檢測位寬數據

然后,必須向配置邏輯發送一個特殊的32位同步字(0xAA995566),提醒器件即將到來的配置數據,并將配置數據與內部配置邏輯對齊。同步前配置輸入引腳上的任何數據都會被忽略,自動檢測總線位寬序列除外。

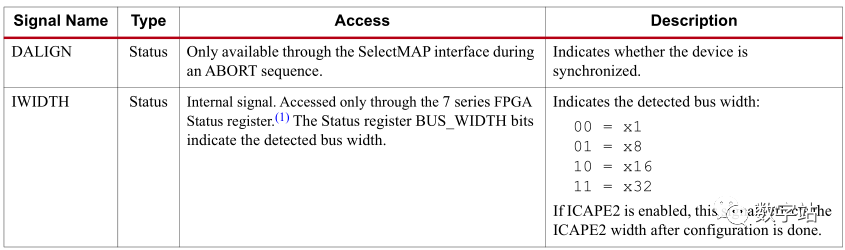

可以通過兩個寄存器的狀態確定同步是否成功以及總線寬度,如圖10所示。

圖10 與同步有關的信號

05檢查設備ID

圖11 檢測設備ID

設備同步后,必須先通過設備ID檢查,然后才能加載配置數據幀。這可防止使用針對不同設備格式化的比特流進行配置。如果在配置過程中發生ID錯誤,設備將嘗試執行回退重新配置。

設備ID檢查是通過配置邏輯文件中的命令執行的,而不是通過JTAG IDCODE寄存器執行。

7系列FPGA JTAG ID代碼寄存器的格式如下:

vvvv:fffffff:aaaaaaaaa:ccccccccccccc1 //其中:V=版本 f=7位系列

代碼 A=9位陣列代碼(包括4位子系列和5位設備代碼) C=公司代碼

06加載配置數據

當總線位寬檢測和同步完成,并且設備ID正確之后,就該加載配置數據了,不同模式按照不同的總線加載數據即可。

圖12 加載配置數據

07CRC校驗

圖13 CRC校驗

這個流程沒有什么介紹的,就是計算接收數據的CRC校驗和,與配置文件中的校驗和進行對比,一致則傳輸正確,不同則將init_b信號拉低后終止配置。

08啟動

圖14 啟動

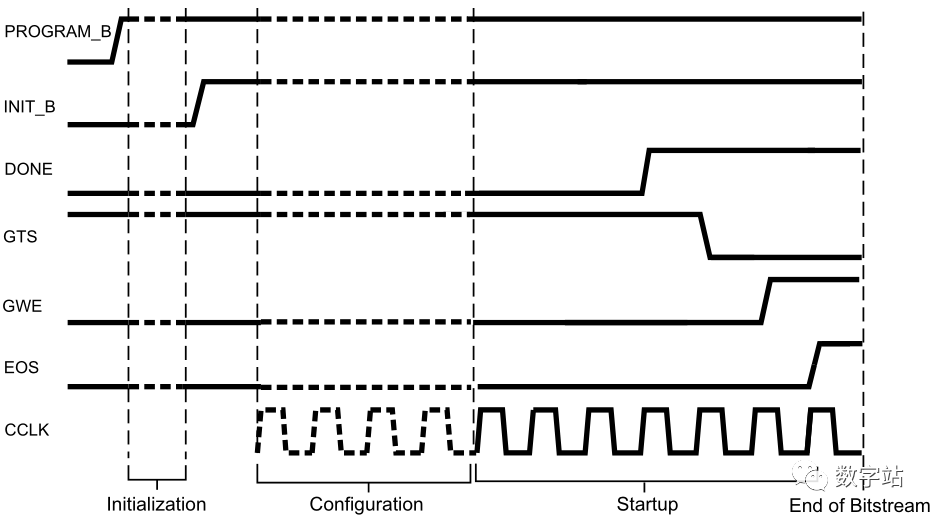

加載配置幀后,比特流指示設備進入啟動序列。啟動序列需要做一些操作,第一步可以選擇是否等待MMCM時鐘管理單元鎖定和DCI匹配(一般這兩個都不用關心),第二步釋放done引腳,通過外部上拉電阻變為高電平,第三步釋放GTS信號,也就是啟用除少數配置引腳之外的所有I/O,第四步使能全局寫入啟用信號(GWE),該信號使能后,CLB和IO管理單元里面的觸發器和RAM就可以根據初始化的值改變狀態了,第五步就是使能EOS信號表示配置和啟動過程均結束。前四步的順序可以在軟件設置里面進行調整,但第五步是固定的,對應時序圖如圖15所示。

圖15 配置信號排序(默認啟動設置)

上述就是一個完整的配置步驟,了解這個過程之后,就能夠具體了解整個上電流程的時序,以及前面講解5個通用配置管腳的功能,能夠知道在配置期間其余IO的狀態。

03配置方式

由2.3小節知,在init_b上升沿時,通過采集模式引腳M[2:0]狀態確定此次的配置方式,不同配置會使用不同的管腳(2.6步驟所使用引腳)來傳輸數據。

01主、從串行配置

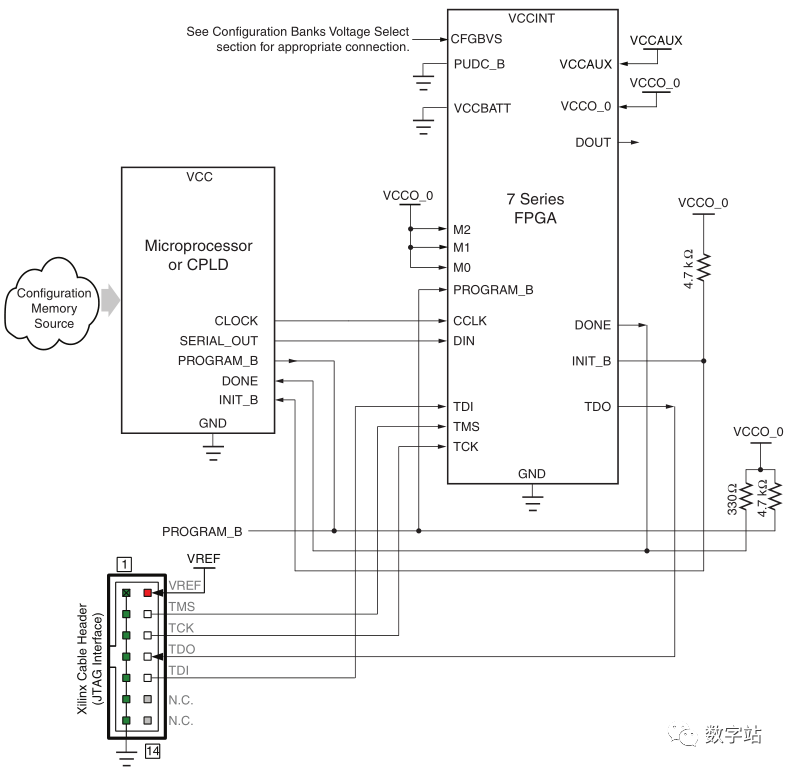

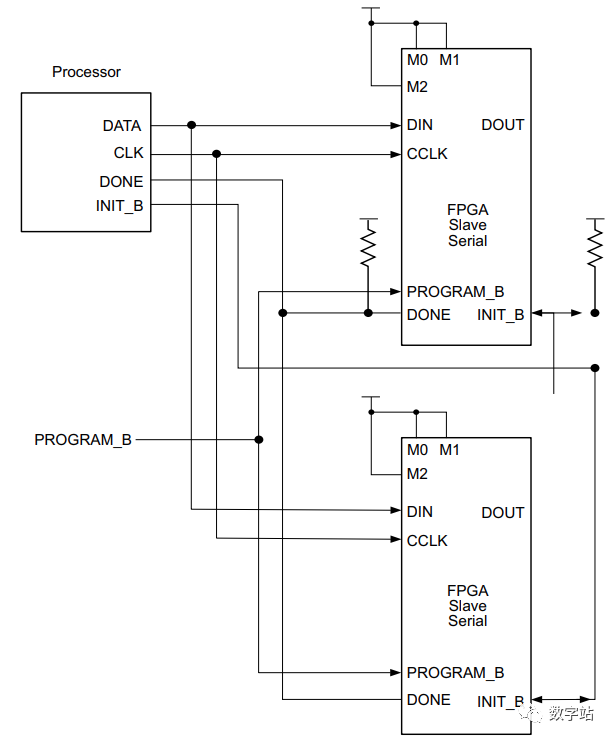

串行模式分為主串行模式(FPGA作為主機,模式引腳狀態M[2:0]=3’b000)和從串行模式(FPGA作為從機,模式引腳狀態M[2:0]=3’b111),區別在于配置數據的時鐘引腳CCLK方向不同。從串行模式,CCLK作為輸入信號,對應原理圖配置如圖16所示。

圖16 從串行配置模式原理圖

不管是什么模式,一般都會帶有JTAG(一般也會存在TCK、TMS、TDI、TDO這四個JTAG引腳)。通過上圖可知,單個FPGA通過從串行配置除了1節講到的通用引腳之外,該配置只使用到了時鐘引腳CCLK和數據輸入管腳DIN,這兩個引腳用于在2.6小節配置過程中加載數據,進而完成配置。

上述連接的優勢在于,ARM或者CPLD可以通過拉低program_b引腳,來重新配置FPGA,當done引腳為高電平表示FPGA已經配置完成,另外消耗的引腳極少。

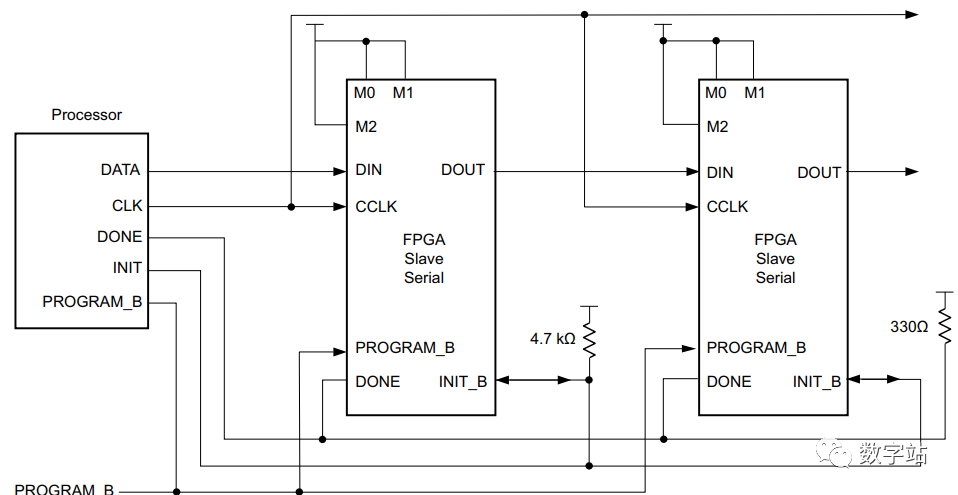

從din引腳輸入的數據,會通過dout引腳輸出,所以可以通過菊花鏈的方式,使用一片ARM或者CPLD達到配置多片FPGA的目的,連接方式如圖17所示,多片FPGA的配置引腳連在一起,配置數據會在前一片FPGA的配置時鐘下降沿從DOUT引腳輸出,后一片FPGA可以在配置時鐘下個時鐘上升沿從DIN引腳采集數據,從而達到配置多片FPGA的目的。

圖17 從串行模式菊花鏈配置多片FPGA

當然還可以直接將數據線也全部并聯,如圖18所示,這種并行配置要求所連接的FPGA型號必須完全相同,且配置相同代碼。

圖18 并行配置原理圖

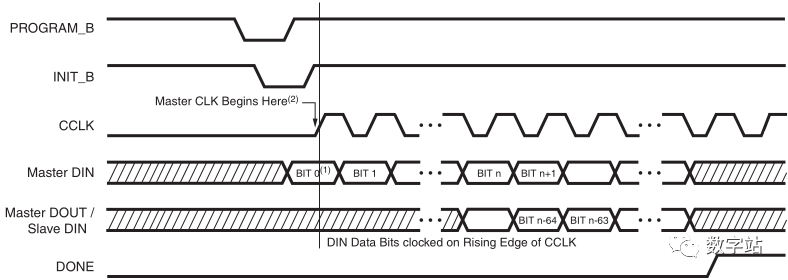

主串行模式與從串行模式的引腳連接基本一致,上電時序也基本一致,如圖19所示,但有兩點區別:其一,主機模式的CCLK對于FPGA來說是輸出管腳,該管腳在init_b拉高后才開始輸出時鐘序列,而從機模式下CCLK信號作為FPGA輸入信號,對時鐘序列持續時間沒有要求。其二,由于主機模式配置時鐘管腳CCLK作為輸出信號,多片FPGA不能共用配置時鐘信號,所以主機模式下不能實現菊花鏈功能。

圖19 主、從串行模式配置時序

綜上,主、從串行配置模式,除了通用的配置管腳和JTAG配置管腳之外,需要使用配置時鐘CCLK和配置輸入數據引腳DIN,如果需要使用菊花鏈配置多片FPGA,那么還會用到配置數據輸出引腳DOUT。

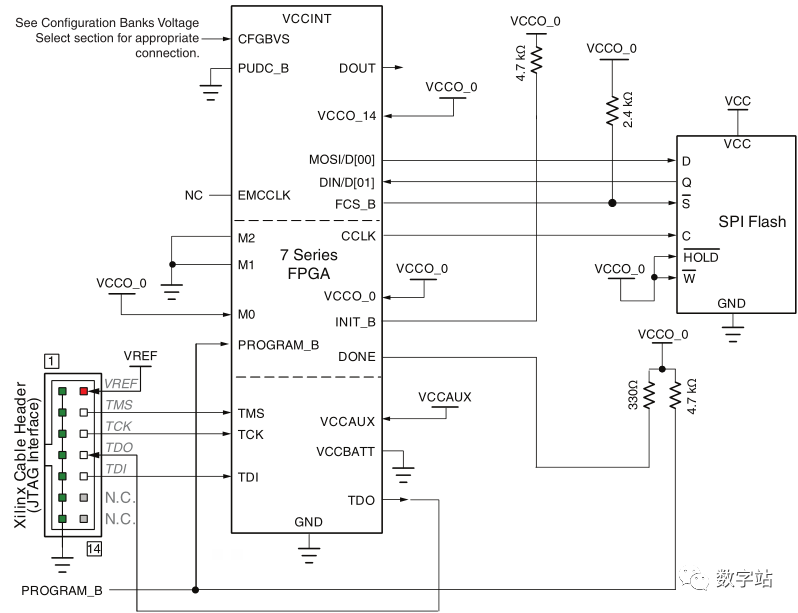

02主SPI模式

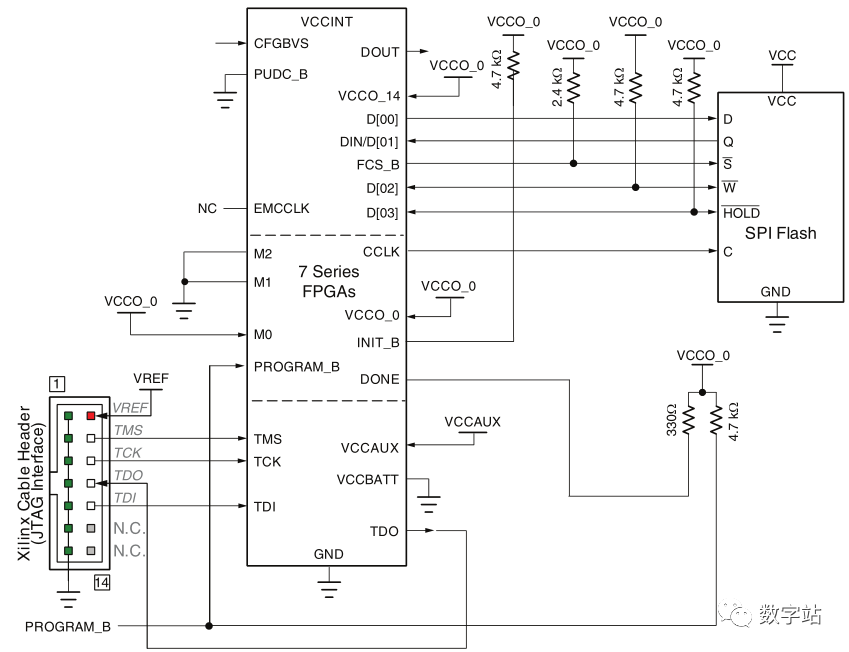

此模式應該是altera和xilinx的FPGA配置最常用的模式,根據配置數據線不同可分為SPIX1、SPIX2、SPIX4三類。因為配置數據輸出管腳DOUT只有一位,故只有SPIX1支持菊花鏈配置,該配置對應原理圖如圖20所示。

圖20 主SPI x1/x2時序圖

使用FCS_B引腳作為flash閃存的片選信號,CCLK作為配置時鐘信號,DIN引腳作為數據輸入引腳,而MOSI引腳作為FPGA數據輸出引腳,向flash發送相關指令,然后獲取配置數據。默認情況下,在配置時鐘CCLK上升沿數據通過DIN引腳輸入FPGA,在CCLK下降沿數據通過DOUT引腳輸出FPGA,因此菊花鏈連接方式依舊是使用前一片FPGA的DOUT引腳連接后一片FPGA的DIN引腳,如圖21所示。

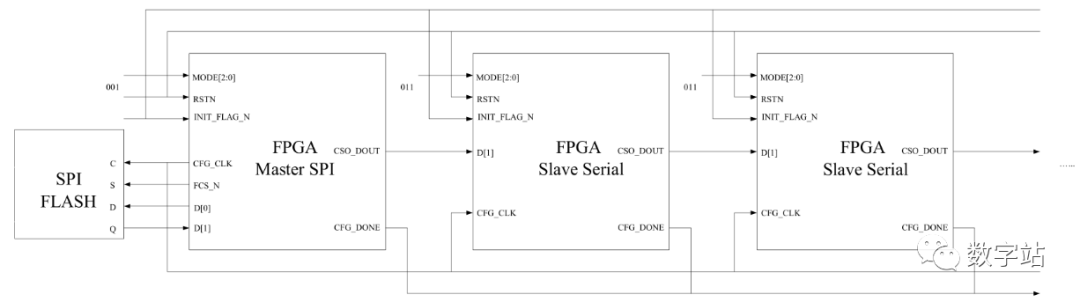

圖21 主SPI模式菊花鏈配置

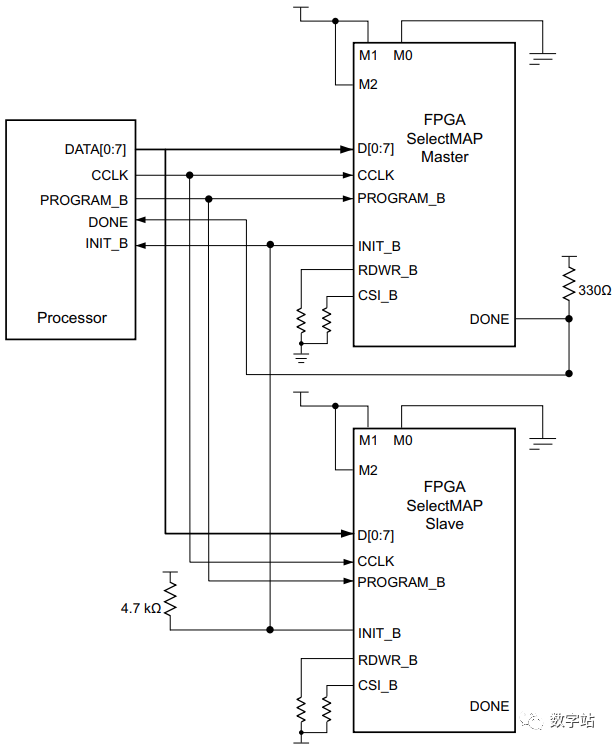

注意:一個配置系統只允許存在一個主機,因為所有器件的配置時鐘CCLK信號必須要共用,所以第一片FPGA采用主SPI配置,其余FPGA采用從串行配置方式,體現在上圖的模式引腳M[2:0]的狀態。

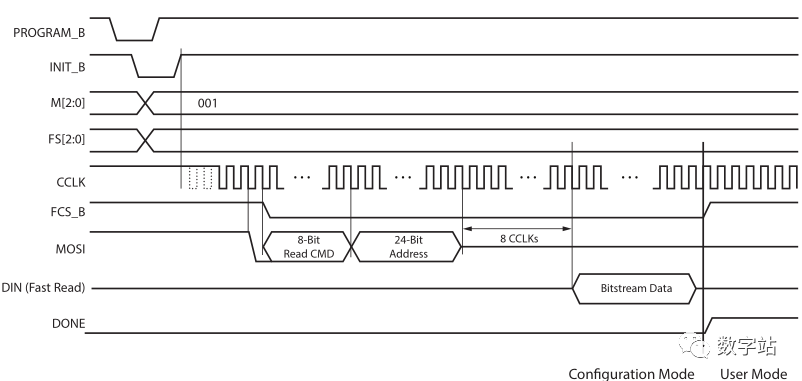

SPI配置的時序如圖22所示,在同步和檢驗設備ID之后,先發送8位讀命令,然后發送24位讀地址數據,8個配置時鐘周期之后,DIN引腳開始傳輸配置數據。CCLK在Configrate之前為3MHz,在Configrate期間會提高數據傳輸頻率。

圖22 7系列FPGA SPI x1模式序列

7系列FPGA的主SPI配置模式支持雙路和四路快速讀取操作,FPGA首先將快速讀取操作碼(0x0B)傳輸到SPI,然后讀取命令以更改比特流早期部分的數據寬度。然后,FPGA向SPI設備發出用于雙路(操作碼0x3B)或四路(0x6B)讀取操作的新讀取命令,并開始讀取適當的數據寬度。

SPI X 4的原理圖連接如下所示,此處的MOSI引腳在發送0x6B之后就會變為輸入數據的最低位D[0],與其他三根數據線構成輸入數據線,其余與SPIx1方式相同,只是不能使用菊花鏈方式進行配置了。

圖23 7系列FPGA SPI x4模式序列

綜上,主SPI模式處理通用配置引腳和JTAG調試引腳外,與配置相關的就片選引腳FCS_B,配置時鐘CCLK,數據輸入DIN,數據輸出MOSI,菊花鏈數據輸出DOUT。原理圖設計時需要特別注意DOUT與MOSI是兩個不同引腳,功能也不相同。如果是SPIx2在發送0x3B之后,會以2位數據寬度讀取flash閃存里的數據,MOSI變為輸入數據的最低位D[0],而數據輸入管腳DIN作為數據輸入的D[1],由此SPIx2與SPIx1的原理圖設計是相同的。如果是SPIx4則需要在SPIx2的基礎上增加兩位數據線D[3]和D[4]連接到flash。

前面提到默認是在時鐘上升沿采集數據,但是可以通過設置在時鐘下降沿采集數據,一般不會用到,需要了解的查看UG470手冊即可。

03主、從SelectMAP配置模式

SelectMAP配置接口為7系列FPGA配置邏輯提供8位、16位或32位雙向數據總線接口,可用于配置和回讀。數據總線的回讀和讀方向僅適用于從SelectMAP模式,根據配置器件的數量不同,一般分為三種單器件配置,多器件串聯菊花鏈配置,多個相同器件并聯配置相同程序。

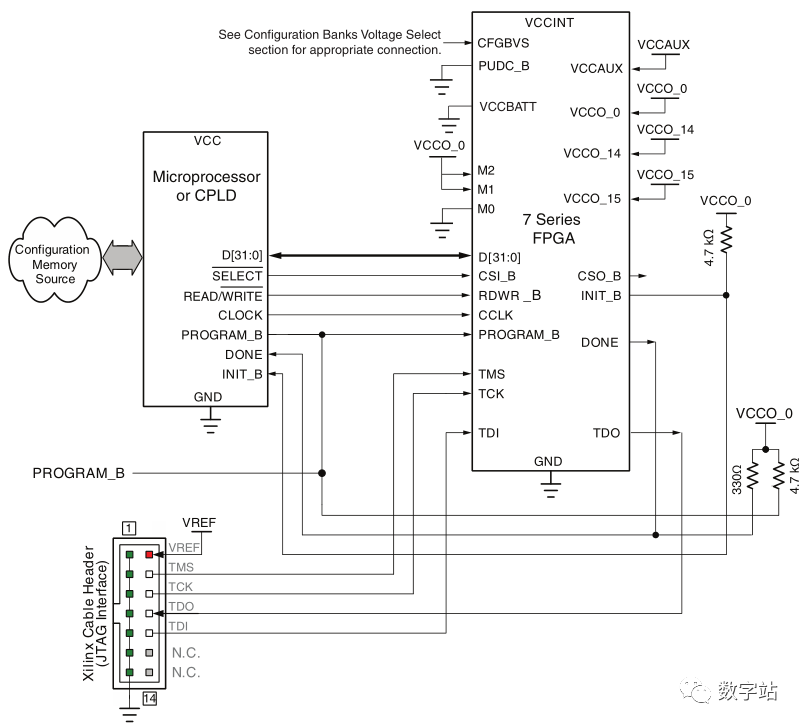

01單器件配置

這種配置方式一般使用微處理器或者CPLD來配置單個7系列器件,可以使用主SelectMAP模式(使用來自FPGA的CCLK)或從SelectMAP模式(如下圖24),一般首選從SelectMAP模式,因為該模式支持回讀。關于該模式下微處理器的控制方式可以參考XAPP583手冊。

圖24 單從機選擇微處理器或CPLD中的MAP配置

由于D[31:0]這32位數據線分布在bank14和bank15,所以需要配置這兩個bank電源VCCO_14、VCCO_15。CSI_B信號作為片選信號,用來指示數據線和RDWR_B的信號是否有效,如果該信號為高電平,則D[31:0]被視為高阻狀態,通過控制該信號可以連續配置數據或者間斷的配置數據。由于數據線D[31:0]是雙向的,需要通過RDWR_B信號狀態判斷數據線作為輸入還是輸出,因此可以通過控制該信號狀態來控制寫入或者讀出數據,從而可以實現數據回讀,如果不需要回讀,可以把該引腳接地處理。

在從配置模式下,當CSI_B為低電平時,如果RDWR_B的值從低電平變為高電平會終止配置,并且將數據線異步更改為輸出。當CSI_B為低電平時,將RDWR_B的值從高變為低會終止回讀,并且將數據線異步更改為輸入。故CSI_B使能時,RDWR_B信號狀態不能發生變化。

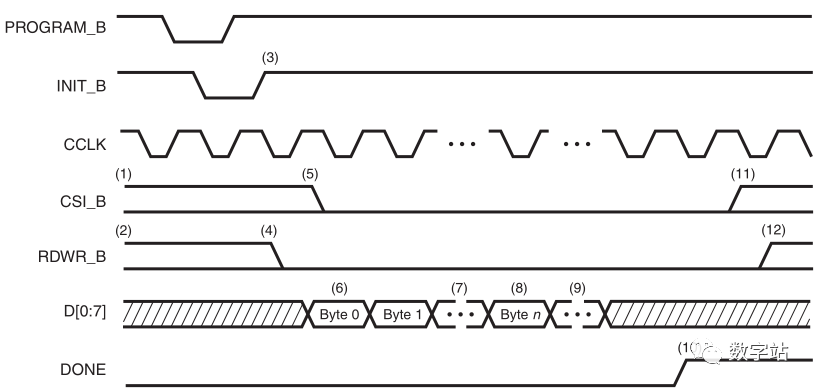

連續配置時序如圖25所示,上電后,配置控制器設置寫控制的RDWR_B信號(RDWR_B=0),并使能CSI_B信號(CSI_B=0)。在使能CSI_B之前,RDWR_B必須被驅動為低電平并保持不變,否則會終止配置。在下一個CCLK上升沿,FPGA開始采樣數據引腳[7:0]狀態,自動匹配數據總線寬度,直到確定總線寬度為止。之后對數據總線的適當寬度進行采樣,以用于同步字搜索,同步完成后,配置開始。加載配置比特流完成后,器件進入啟動序列。在比特流指定的啟動序列階段,FPGA將其DONE置為高電平。控制器應繼續發送CCLK脈沖,直到啟動序列完成。(根據2.8小節知在Done變為高電平后,可能需要幾個CCLK脈沖)。

配置后,CSI_B和RDWR_B信號可以拉高,也可以保持使能,由于SelectMAP端口處于非活動狀態,此時切換RDWR_B不會導致終止配置。

圖25 連續x8 SelectMAP數據加載

如果控制器無法提供連續的數據流,那么可以使用非連續的數據加載方式,這種方式可以通過兩種方式實現。方法一是通過拉高CSI_B信號(如圖26所示),第二種方法是通過停止生成CCLK實現(如圖27所示)。

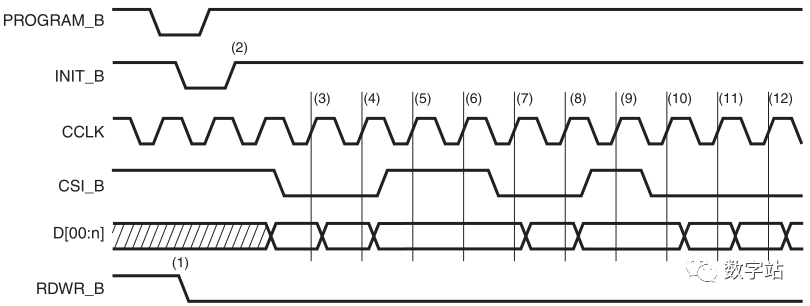

如圖26,在3、4、7、8、10、11、12的CCLK上升沿處,CSI_B信號使能,加載一個配置數據,而5、6、9處CSI_B信號被拉高,該處數據無效,不會加載配置數據,從而實現非連續數據加載。

圖26 通過CSI_B控制的非連續SelectMAP數據加載

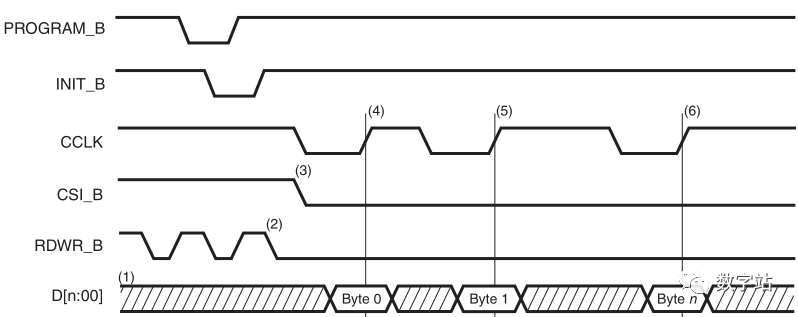

如圖27所示,CSI_B片選和RDWR_B信號的狀態保持正常,通過改變CCLK時鐘寬度,更改CCLK上升沿位置,從而實現非連續的數據加載。

圖27 通過控制CCLK的非連續SelectMAP數據加載

02配置多個相同器件

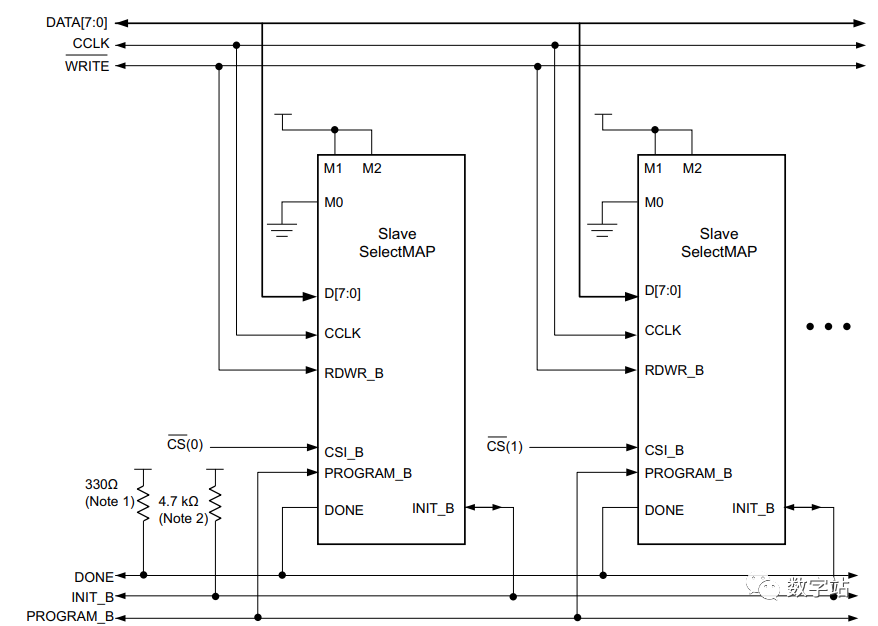

根據是否需要回讀,依舊有兩種配置方式,如圖28所示支持回讀FPGA配置數據,通過將多片FPGA的數據線D和配置時鐘CCLK以及數據線方向控制i新年好PDWR_B連接在一起實現,由于需要回讀操作,即需要FPGA輸出數據,那么多片FPGA不能存在同時驅動同一組數據線的情況,所以多片FPGA的片選信號CSI_B必須分開連接到ARM或者CPLD,否則可能會燒毀器件。

圖28 8位SelectMAP總線上的多從設備配置(一)

這種方法的劣勢在于需要多個片選信號,優勢在于通過控制CSI_B信號可以給多片FPGA分別燒寫不同的配置程序,而且支持回讀功能。

另一種不需要使用回讀功能的配置方式如圖29所示,數據線和時鐘線與圖28連接一致,將片選CSI_B和方向信號PDWR_B均接地。

圖29 8位SelectMAP總線上的多從設備配置(二)

這種方式的優勢在于節省了控制多個片選信號CSI_B的引腳,缺點在于多個器件只能配置相同程序,且不支持回讀。

03菊花鏈配置多個器件

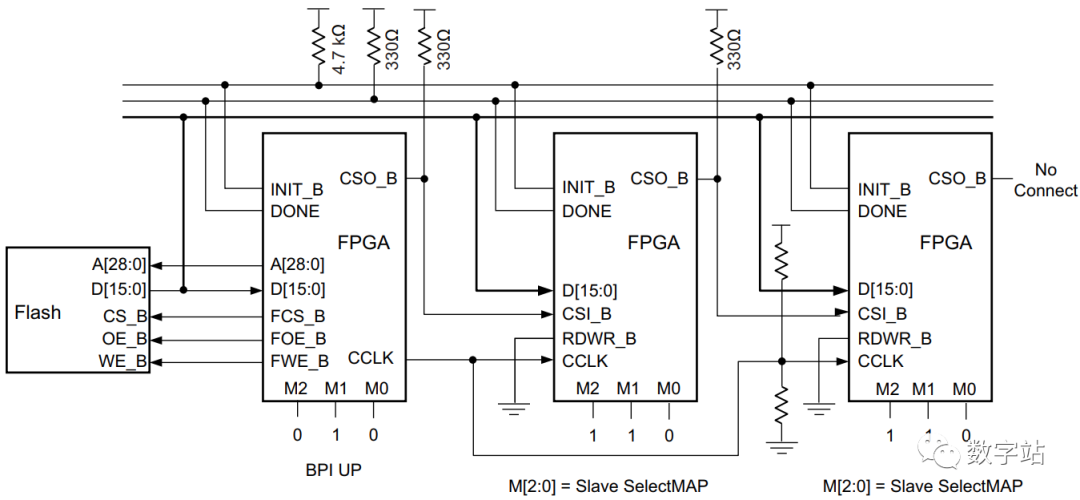

并行器件的菊花鏈配置方式如圖30所示,注意第一個器件可以是主BPI、主SelectMAP、從SelectMAP三種配置之一,但后續器件必須采用從SelectMAP配置模式,該配置方式不支持回讀和回退操作。

圖30 并聯菊花鏈

注意上圖中D[15:00]、CCLK、RDWR_B、PROGRAM_B、DONE、INIT_B均連接在一起,菊花鏈是通過一路片選信號FCS_B或者CSI_B進行控制的,CSO_B會把CSI_B的信號輸出,所以上一片FPGA的CSO_B引腳連接到下一片FPGA的SCS_B引腳就能實現菊花鏈控制。關于BPI控制在3.4節講解。

綜上,SelectMAP配置相比串行配置區別在于數據線數量增加且變為雙向,需要PDWR_B信號控制數據線方向,還增加了一個片選信號CSI_B,菊花鏈的連接方式也由數據信號DIN變為控制片選信號CSI_B。在配置期間會相對串行會增加一個自動檢測總線寬度的流程,之后才會對同步數據,然后傳輸配置數據,在從SelectMAP模式下還可以支持回讀和非連續性傳輸配置數據。

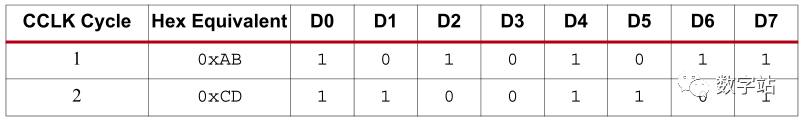

編寫微控制器或者CPLD程序時需要注意,在SelectMAP x8模式下,每個CCLK加載一個字節配置數據,每個字節的MSB提供給D0引腳。圖31顯示了如何將十六進制值0xABCD加載到SelectMAP數據總線中。

圖31 SelectMAP 8位模式的位排序

圖32顯示了7系列FPGA SelectMAP x8、x16和x32數據總線寬度的位排序。

圖32 位排序

04主BPI配置

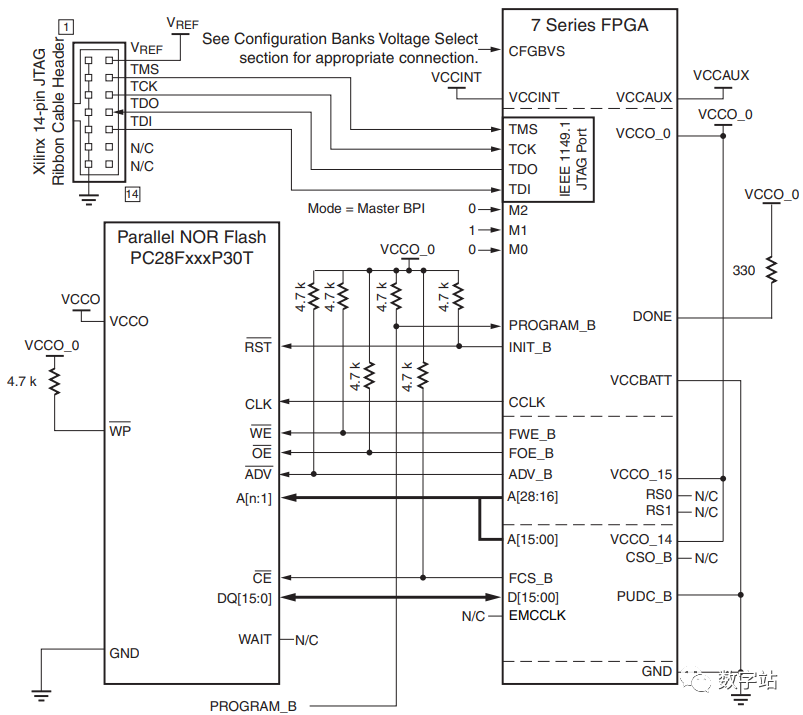

7 系列 FPGA Master BPI 配置模式支持使用行業標準并行 NOR (BPI) 閃存器件進行比特流存儲。FPGA 支持直接連接到 BPI 閃存的地址、數據和控制信號,以提取存儲的比特流。

注意,某些所需的引腳位于組 15 中,Artix-7 7A50T 和較小器件的 CPG236 封裝不進行綁定Bank 15,因此不支持 BPI 配置。Spartan-7 系列不支持 BPI 配置。

7系列FPGA Master BPI配置模式有兩種可用的BPI閃存讀取模式:異步和同步。與其他直接配置模式相比,使用帶有外部主時鐘的 BPI 閃存同步讀取模式可以實現更快的配置時間。此外,可通過多達 29 條地址線訪問更寬密度范圍的并行 NOR 閃存。

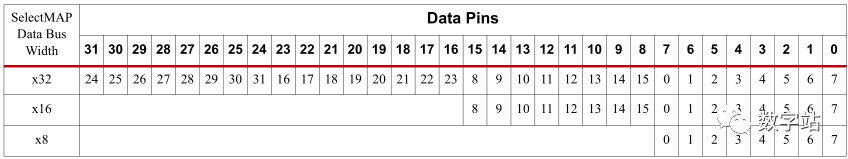

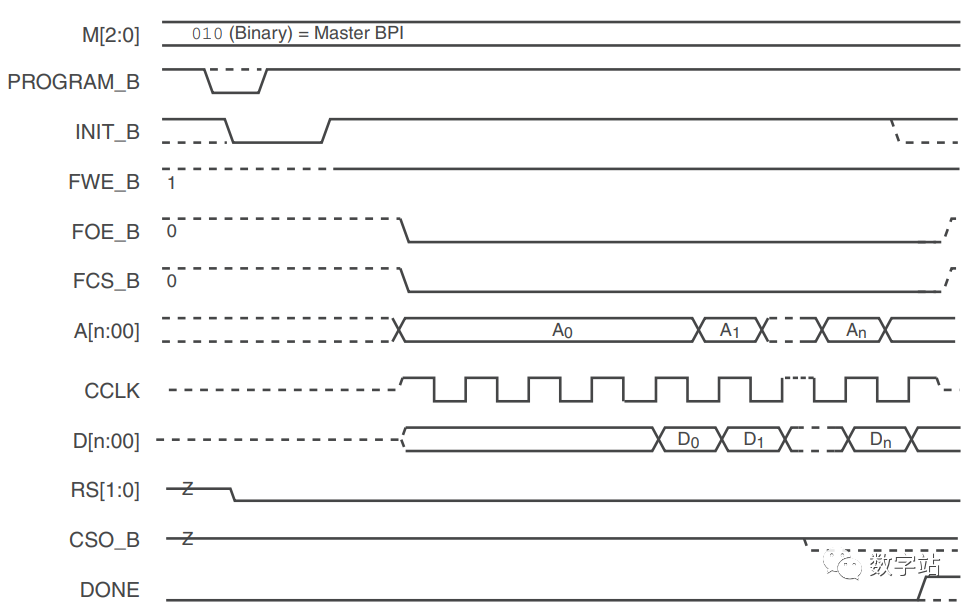

01異步讀取

在Master BPI配置模式下,7系列FPGA默認使用BPI flash異步讀取模式來讀取比特流數據,如圖33所示。FPGA從給定的起始地址驅動地址總線,BPI flash發回比特流數據,默認起始地址是地址 0。此模式下配置時鐘CCLK信號不需要連接,INIT_B信號作為flash的復位信號,FWE_B作為flash的寫使能信號,FOE_B信號作為flash芯片的輸出使能信號,而FCS_B作為flash芯片的片選信號,注意對配置相關信號帶有后綴_B的表示低電平有效。該配置方式數據位寬支持8位及16位,地址線有29位,消耗的IO會比較多,但是配置速度比串行模式更快。

圖33 7 系列 FPGA 主站 BPI 配置接口 - 異步讀取示例

對應時序圖如圖34所示,上電后,當 FPGA 的 INIT_B 輸出變高時,采樣模式引腳 M[2:0] ,PUDC_B 引腳必須在整個 FPGA 配置過程中保持恒定的邏輯電平。Master BPI 配置模式確定后,FPGA 驅動閃存控制信號(flash輸出使能信號FOE_B 拉低,flash寫使能信號FWE_B拉高,flash片選信號FCS_B拉低)。雖然對于 BPI flash 異步讀取模式,CCLK 輸出沒有連接到 BPI flash 器件,但 FPGA 在 CCLK 上升沿之后輸出地址,且仍然在 CCLK 的下一個上升沿采樣數據,BPI相關的時序參數還是以CCLK引腳為參考。

在主 BPI 模式下,地址從 0 開始并遞增 1,直到 DONE 引腳拉高。如果地址達到最大值 (29’h1FFFFFFF) 且配置未完成(DONE為低電平),則會在狀態寄存器中寫入錯誤標志,把RS0和RS1管腳拉低,并開始回退重新配置,如果不適用回退模式,則RS0和RS1引腳可以懸空。

圖34 7 系列 FPGA 主 BPI 配置 — 異步讀取波形

FPGA 通過其 A[n:00] 引腳驅動初始地址 (A00),并保持初始地址至少 10 個 CCLK 周期,對于上電配置,初始地址為 0x00000000。默認情況下,在 DONE 變為高電平后的一個周期,多功能配置 I/O 切換到用戶模式。

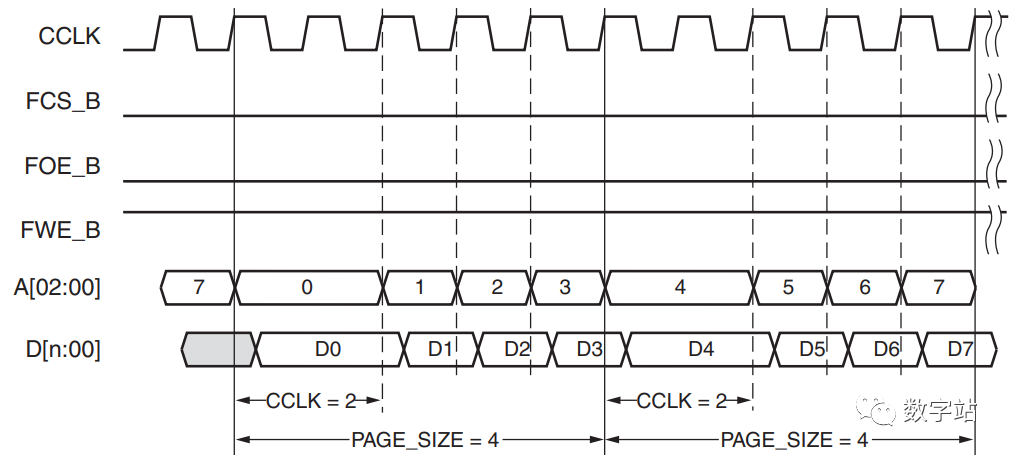

7 系列 FPGA BPI 模式還支持異步頁模式讀取,以允許提高 CCLK 頻率。首次訪問頁面通常需要最長的時間(約 100 ns),后續訪問同一頁面所需的時間較短(約 25 ns)。這些參數可在 7 系列器件中進行位流編程,以利用頁面讀取并最大化 CCLK 頻率:頁面大小為1(默認)、4 或8。如果實際閃存頁面大小大于8,則應使用值8 以使效率最大化。首次訪問CCLK 周期為1(默認)、2、3 或4。如果頁面大小為1,則CCLK 周期必須為1。CCLK 頻率。

圖35 BPI 波形(頁面大小 = 4,首次訪問 CCLK = 2)

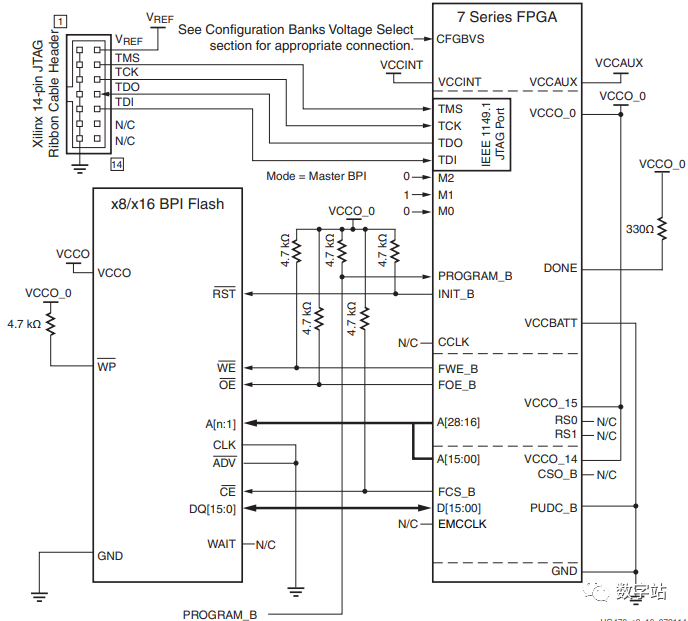

02同步讀取

注意:新設計不建議使用主 BPI 同步讀取模式,閃存芯片可能不支持該方式,需要聯系閃存廠家確認是否支持該方式讀寫。

7 系列 FPGA 主 BPI 配置模式可以選擇支持突發、同步讀取模式讀取比特流,如圖36所示,并在同步讀取模式支持。同步模式將來自 FPGA 的給定起始地址鎖存到其內部地址計數器中,然后給定一個時鐘,閃存在每個時鐘周期內將數據從下一個順序地址位置輸出到其數據總線。在同步讀取模式下,BPI 設備傳輸數據的速度比通過異步接口讀取快很多倍。

FPGA 以異步讀取模式啟動,使用默認的 CCLK 頻率,比特流標頭確定讀取模式是繼續異步還是切換到同步讀取模式。如果設置了 BPI_sync_mode 選項,比特流命令將啟動從異步讀取到同步讀取的切換。該選項有兩種可用設置:類型1用于設置 G18F 閃存系列同步和延遲位,類型2用于設置 P30/P33。同步模式的切換由 FPGA 控制器完成,該控制器對 BPI 閃存配置寄存器執行異步寫入,將器件設置為同步模式并啟動比特流重讀。為了支持同步讀取模式,FPGA CCLK 輸出連接到 BPI 閃存器件,并且 ADV_B FPGA 信號必須連接到閃存 ADV 信號。

BPI 閃存配置寄存器同步位設置是易失性的,在斷電時或當 FPGA INIT_B 變低向 BPI 閃存發出復位時會被清除。

圖36 7 系列 FPGA Master BPI 配置接口同步讀取示例

與異步讀取模式相比,同步讀取模式增加了配置時鐘信號CCLK和ADV_B信號,其余信號連接方式保持不變。ADV_B信號為低電平時,表示地址線上輸出的數據有效。其時序與異步相似。

綜上所述,主BPI模式是用來并行讀取flash數據的,一般用于速度要求較高的場合,相比主SPI模式,增加了flash的數據輸出使能信號FOE_B,flash寫數據使能信號FWE_B,地址信號A[28:1],數據線由1~4位增加到了8位或者16位,同步方式還需要ADV_B地址有效指示信號。根據是否支持回退重配置功能,可能還需要RS0與RS1信號。

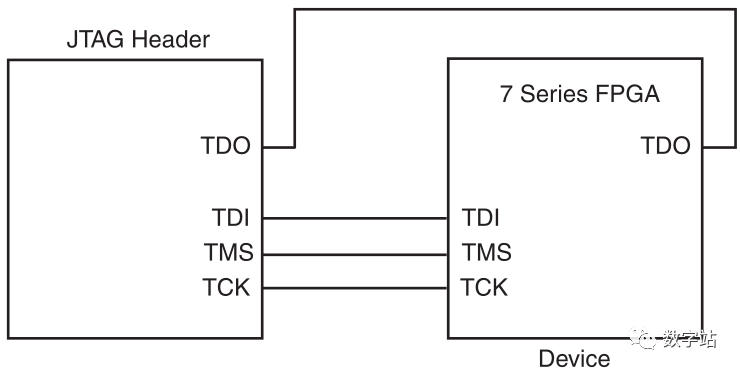

05JTAG配置模式

7 系列器件無論配置模式引腳設置如何,器件都支持隨時通過 JTAG 端口進行配置。但當要通過 JTAG 端口專門配置器件時,可以使用顯式 JTAG 配置模式設置。

對于單器件配置,如果使用 Xilinx 工具配置器件,則會自動發出 TAP 控制器命令。下載電纜必須連接到相應的四個 JTAG 引腳(TMS、TCK、TDI 和 TDO),以將比特流自動從計算機端口傳送到 7 系列 FPGA。這些工具會自動檢查連接是否正確,并驅動命令來傳送和驗證配置位是否得到正確管理。

圖 347顯示了典型的 JTAG 設置,其中需要將單個器件連接到 JTAG 信號接頭,該信號接頭可以在xilinx工具的控制下由處理器或 Xilinx 編程電纜驅動。TCK 是用于邊界掃描操作的時鐘, TDO-TDI 連接創建了一個串行數據路徑,用于通過 JTAG 鏈傳輸數據, TMS 控制 TAP 控制器中狀態之間的轉換,這四個管腳內部均有上拉電阻。

圖37 單個器件 JTAG 編程連接

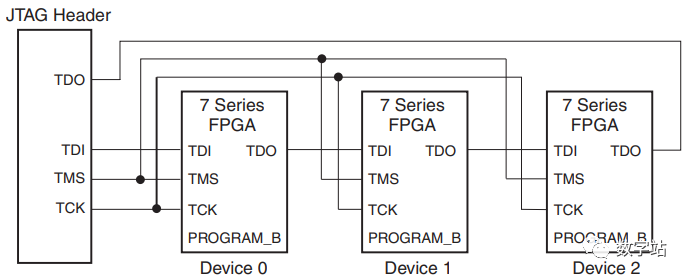

可以在鏈中配置多個 7 系列設備,電路連接方式如圖38所示。

圖38 多器件邊界掃描鏈

對于JTAG配置的詳細流程會比較多,需要了解的可以查看硬件接口協議之“JTAG”(https://xilinx.eetrend.com/content/2019/100044971.html),或者直接查看Boundary-Scan for 7 Series Devices Using IEEE Standard 1149.1標準協議。

04總結

通過上述講解,可知xilinx7系列FPGA配置方式有7種,其中JTAG優先級最高,在其他模式下也可以直接進行JTAG配置。然后六種其實可以根據外設區分,如果是flash對FPGA進行配置,那么FPGA只能作為主機,根據數據線的寬度可分為SPI模式和BPI模式,其中SPIx1和BPI模式支持菊花鏈方式。如果是用微處理器或者CPLD來配置FPGA,那么FPGA可以作為主機,也可以作為從機,根據數據線寬度可以分為主串行、從串行、主并行、從并行共4種配置模式,主從是根據FPGA的時鐘方向確定的,FPGA作為主機,則輸出配置時鐘信號CCLK。從串行、從并行支持菊花鏈配置模式,并行模式數據線可以為8位、16位、32位,在同步之前需要通過自動檢測數據線位寬。

關于回讀,回退重新配置等操作沒有做講解,使用的頻率較低,需要的可以閱讀UG470手冊,另外要注意zynq系列的配置方式與純PL的器件也有區別,zynq器件除JTAG以外不能對PL單獨配置,必須通過PS去配置PL,麻煩一點。

-

FPGA

+關注

關注

1652文章

22258瀏覽量

629427 -

原理圖

+關注

關注

1339文章

6422瀏覽量

244362 -

Xilinx

+關注

關注

73文章

2192瀏覽量

129709 -

引腳

+關注

關注

16文章

2068瀏覽量

54990

原文標題:誰說配置難?這篇文章讓你輕松掌握xilinx 7系列FPGA配置技巧

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Xilinx 7系列FPGA的時鐘結構解析

Xilinx 7系列FPGA管腳是如何定義的?

xilinx7系列FPGA的7種邏輯代碼配置模式

Xilinx 7系列與Ultrascale系列FPGA的區別

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

一文詳解xilinx 7系列FPGA配置技巧

一文詳解xilinx 7系列FPGA配置技巧

評論