先給大家簡單快速地介紹一下 Vivado 集成設計環境,即 IDE。當打開 Vivado 工程后,會有一個工程概要,向您介紹工程的設置、警告和錯誤信息以及工程的一般狀態。

2012-04-25 09:00:43 7233

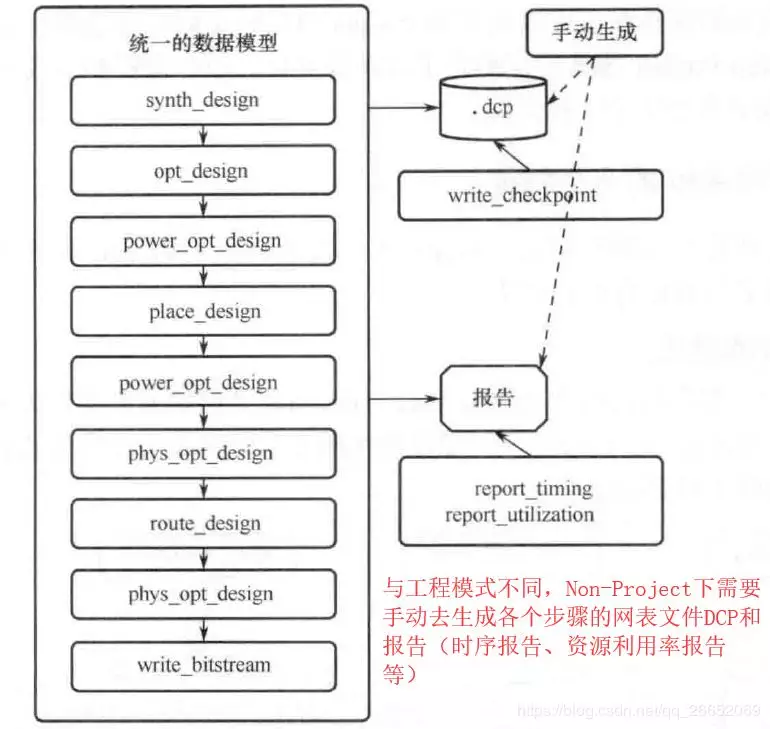

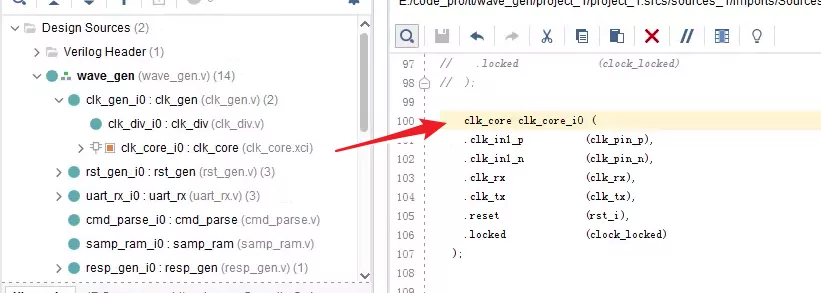

7233 01. Vivado的兩種工作模式 Vivado設計有工程和非工程兩種模式: 1. 工程模式: 工程模式是使用Vivado Design Suite自動管理設計源文件、設計配置和結果,使用圖形化

2020-11-09 17:15:47 5785

5785

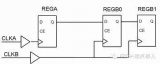

跨時鐘域路徑分析報告分析從一個時鐘域(源時鐘)跨越到另一個時鐘域(目標時鐘)的時序路徑。

2020-11-27 11:11:39 6743

6743

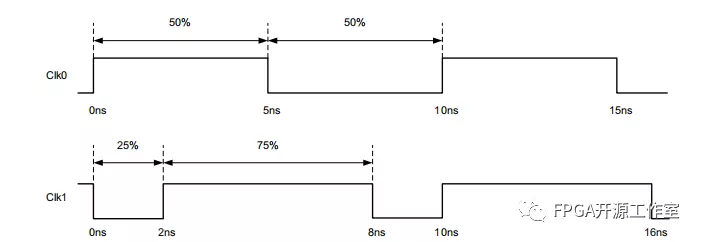

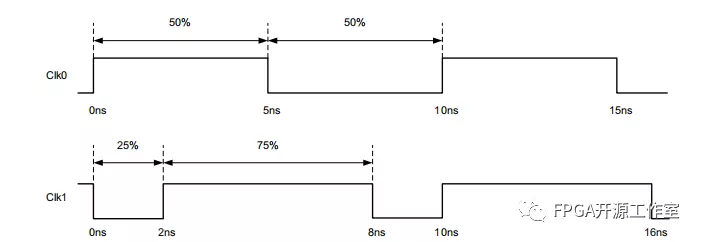

1. 時鐘介紹 在數字設計中,時鐘代表從寄存器(register)到寄存器可靠傳輸數據的時間基準。Xilinx Vivado集成設計環境(IDE)時序引擎使用ClocK特征計算時序路徑要求,并通過

2020-11-29 10:51:45 8525

8525

作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 4357

4357 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-14 09:09:56 2515

2515 ,只有在時鐘的支持下,電子產品才能正常工作。 ? 那么時鐘產品有哪些種類,它們分別有什么特性,工程師在選用的時候需要注意些什么呢,我們今天就來一起聊一聊。 ? 時鐘產品的分類 時鐘產品主要分為兩大類,一類是異步時鐘產品,

2021-09-06 07:18:00 9228

9228 Vivado概述 / 251.3.1 Vivado下的FPGA設計流程 / 251.3.2 Vivado的兩種工作模式 / 261.3.3 Vivado的5個特征 / 30參考文獻 / 31第2章

2020-10-21 18:24:48

Vivado下set_multicycle_path該怎樣去使用呢?在兩個不同時鐘主頻的情況下使用set_multicycle_path的情況是怎樣的?

2022-02-16 08:00:49

和Vivado的綜合性能,管腳位置與電平約束完全一致。PS:若時鐘和管腳約束直接敲命令,兩者除了語法,沒有明顯區別。6、綜合實現——點評:Vivado默認策略情況下從綜合到生成bit共計23分50秒。而

2021-01-08 17:07:20

)無法通過放置階段,會產生大量的放置錯誤,如下所示。基本上,Vivado不能放置與時鐘相關的任何原語 -BUFG,BUFH,PLLE2_ADV,GTHE2_COMMON等。設計針對xc7vx690t

2018-11-02 11:32:44

Vivado綜合可以理解多種多樣的RAM編寫方式,將其映射到分布式RAM或塊RAM中。兩種實現方法在向RAM寫入數據時都是采取同步方式,區別在于從RAM讀取數據時,分布式RAM采用異步方式,塊RAM

2020-09-29 09:40:40

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的時鐘方案是zynq PS FCLK_CLK0-->時鐘向導IP輸入(Primitive PLL)的輸入。合成

2018-11-05 11:40:53

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

現代高級雷達系統正在受到多方面的挑戰——頻率分配上的最新變化導致許多雷達系統的工作頻率非常接近通信基礎設施和其他頻譜要求極高的系統。

2019-07-22 07:50:19

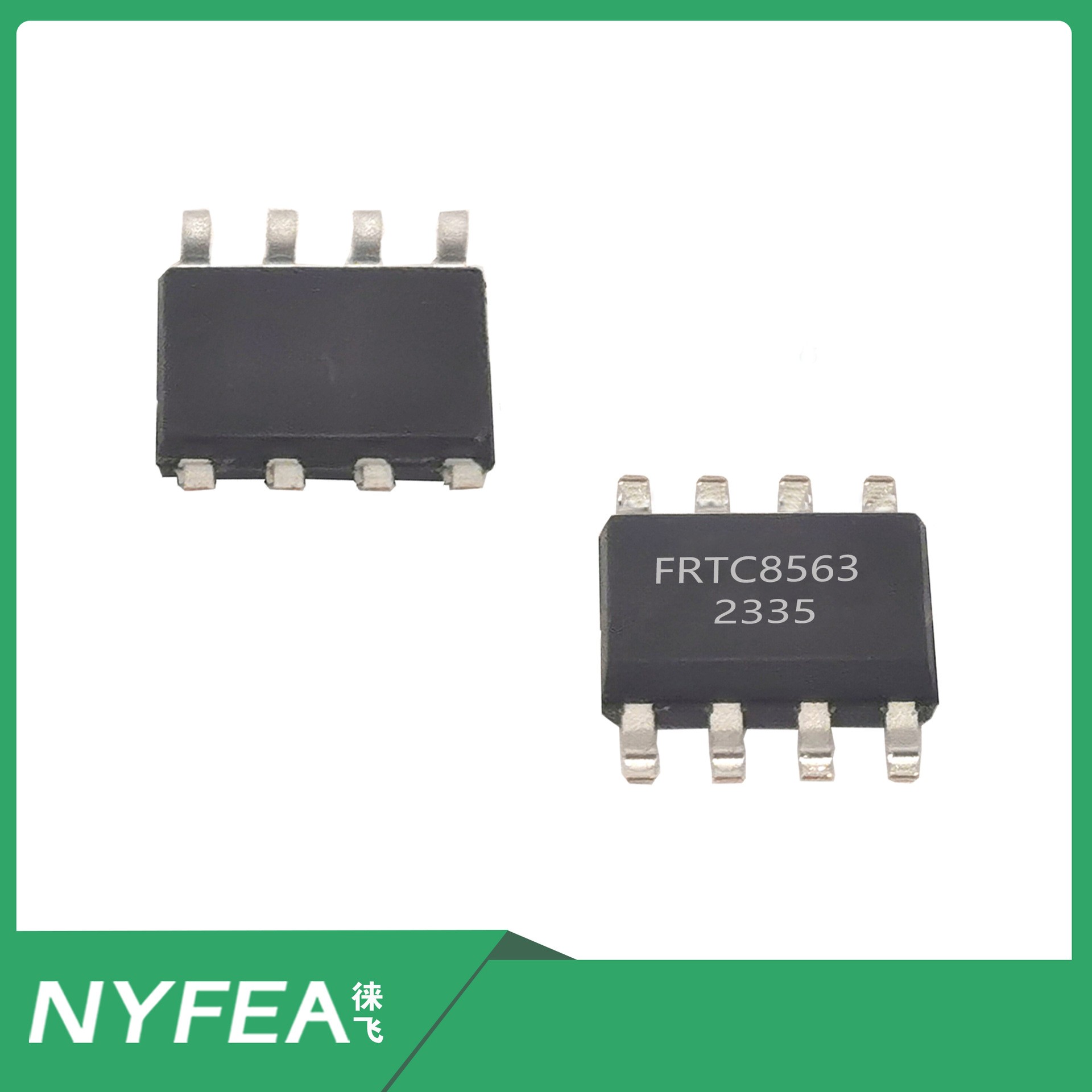

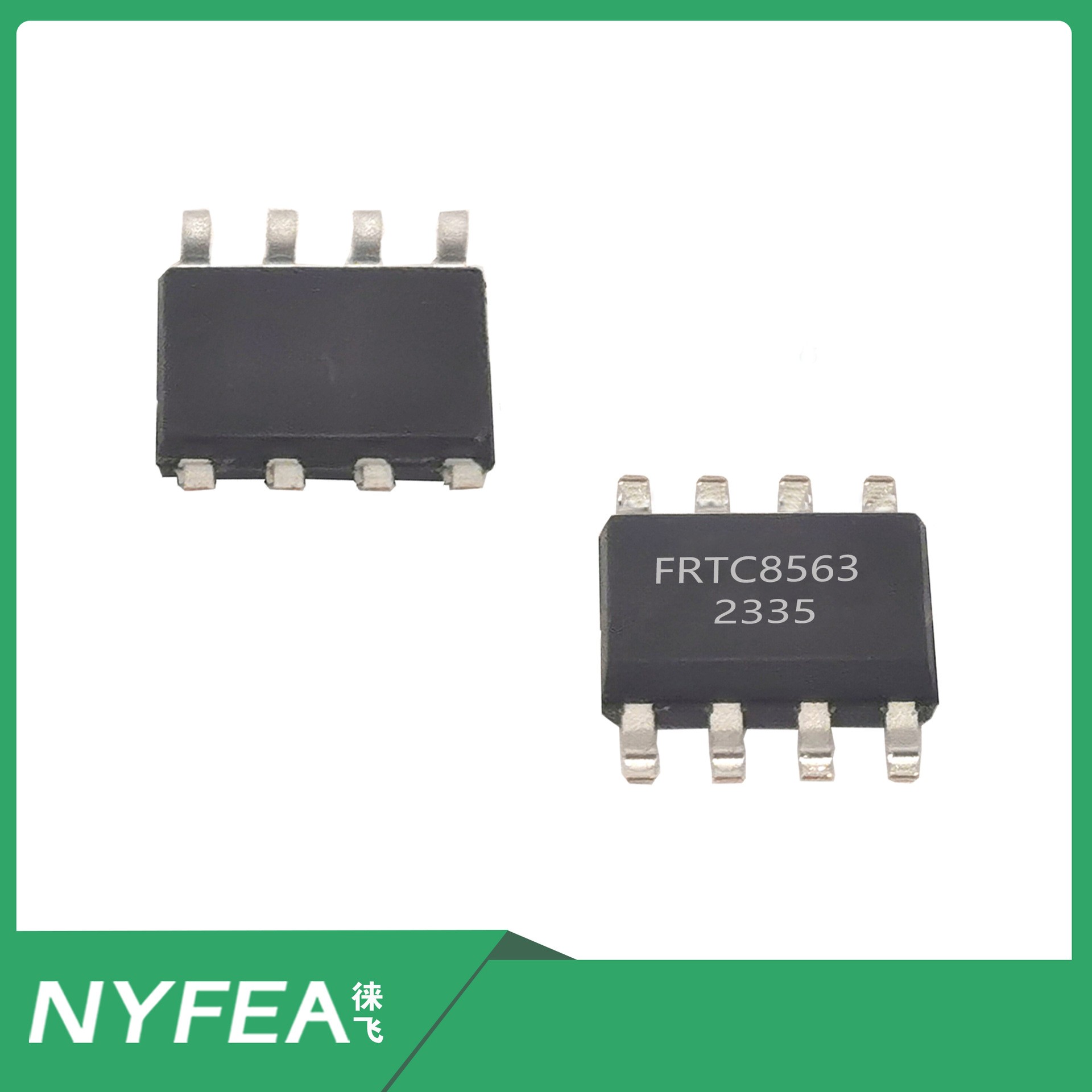

RTC時鐘具有哪些特性應用?

2021-10-13 06:09:16

RTC時鐘具有哪些特性? RTC正常工作的一般配置步驟是怎樣的?

2021-11-23 06:52:26

STM32F407之時鐘、頻率、存儲概述文章目錄STM32F407之時鐘、頻率、存儲概述1.整體特性1.1存儲器組織架構1.2 內嵌SRAM1.3Flash和自舉程序2.電源3.時鐘介紹3.1系統

2021-08-02 07:24:37

為什么要使用thumb模式,與ARM相比較,Thumb代碼的兩大優勢是什么?

2022-11-02 14:17:55

問候!我正在使用Virtex7 / XC7V2000T / ***1925。我有兩個clcoks,pipe3_clk和ulpi_clk,連接到同一時鐘區域的兩個CCIO,X1Y7。但Vivado在

2020-07-16 14:18:54

伺服電機分為交流伺服和直流伺服兩大類。交流伺服電機的基本構造與交流感應電動機(異步電機)相似。在定子上有兩個相空間位移90°電角度的勵磁繞組Wf和控制繞組WcoWf,接恒定交流電壓,利用施加到Wc上

2021-06-28 09:45:02

,設置的主時鐘頻率是250M,實際送給cpu的也是這個頻率,但是看了一下nuclei studio里面的system_hbirdv2.c文件里面的時鐘頻率確是80M,這倆已經不匹配了,但是在vivado

2023-08-11 11:18:54

單片機最小系統電路包括哪兩大類

2023-10-31 07:28:49

我在vivado 2016.3中看到了以下地方的錯誤錯誤:[放置30-675]支持全局時鐘的IO引腳和BUFG對的次優放置。如果此子設計可接受此子優化條件,則可以使用.xdc文件中

2018-11-09 11:37:33

秒(100 Mhz)關閉和打開一個LED,我這樣做是為了驗證如何更改ZYNQ的時鐘頻率使用vivado的約束。這是我放在.xdc文件中生成不同的時鐘頻率set_property PACKAGE_PIN

2020-04-01 08:46:16

。標準的嵌入式系統架構有兩大體系,RISC處理器和CISC處理器體系。嵌入式主板分為比較常見的兩大類:1、基于X86的嵌入式主板,Intel的X86 處理器就屬于CISC體系,(一般使用INTEL、AMD、威盛、或其他產家的...

2021-12-16 06:41:20

大家好,據我了解,Vivado僅在合成過程的地點和路線部分使用多線程。那么,真正改變vivado性能的方法(性能=從頭開始合成項目的速度+在vivado合成時在計算機上執行其他工作的能力)主要是核心

2019-04-25 06:33:01

嗨,我想創建一個設計,我需要2Mhz clk,我想用16Mhz輸入時鐘的vivado套裝中的“時鐘向導”IP核生成它。根據Xilinx手冊(下面的鏈接),這可以通過CLKOUT4_CASCADE選項

2020-07-27 06:32:48

量級。如要對晶振老化漂移優化,需要得到晶振在上級時鐘良好、時鐘板處于鎖定狀態下的漂移,通過讀取鎖定電壓值即可。 需要特別注意的是,這個鎖定值會在晶振老化漂移的基礎上疊加晶振溫度特性的影響,如果晶振溫度

2013-12-17 16:10:55

誰來闡述一下電感式傳感器可分為哪兩大類?

2019-11-18 15:14:40

癌細胞生長速度比一般人快24倍;我國每年出生的2000萬兒童中,有35萬為缺陷兒,其中25萬為智力殘缺,有專家認為,電磁輻射是影響因素之一因此,電磁輻射問題越來越受到世界各國的普遍重視。高爾生教授在他的《空調使用對***質量的影響》中指出,電磁輻射對人體的危害,表現為熱效應和非熱效應兩大方面。

2019-05-31 06:45:55

親愛的大家,我現在正在使用Vivado 2013.3。我試圖將PL結構時鐘從1 MHZ更改為500KHZ。 (1 MHZ下沒問題)但是,Vivado在運行綜合時崩潰了。對我來說減少PL結構時鐘非常重要,因為我打算在一個時鐘周期內收集更多的XADC數據。我該怎么辦?謝謝!

2020-03-25 08:40:07

加拿大攻克新型太陽能電池兩大技術瓶頸

電解液和電極涂層材料是20余年來困擾新型太陽能電池技術發展的兩大難題。加拿大科學

2010-04-10 08:41:18 666

666 在Vivado中通過set_clock_groups來約束不同的時鐘組,它有三個選項分別是-asynchronous,-logically_exclusive

2017-02-08 08:39:49 1357

1357

Suite? 和 ?UltraFast?? 設計方法加速設計生產力: .????????? 查看 UltraFast? 設計方法指南 ·????????? 觀看? Vivado? 快速入門視頻 ,深入了解 ?Vivado Design Suite? 的各種工具與特性,視

2017-02-09 09:06:11 455

455 最近有些朋友在ISE中做的V7項目需要切換到vivado來,但導入代碼后,導入約束時,發現vivado不再支持UCF文件,如果手抄UCF約束到 VIVADO 的 XDC 約束,不僅浪費時間,而且容易出錯,這里介紹一種方法可以實現兩種約束的切換。

2017-03-24 13:54:36 9459

9459

搭載“部分重配置技術”的 Vivado 2017.1 的 HLx 版本軟件現在可以下載了!

2018-07-08 06:23:00 5116

5116 此篇文章里,我們將通過使用InTime來檢驗Vivado 2017.1和Vivado2016.4之間的性能對比。 概要:分別進行了3個Vivado 2017.1對Vivado2016.4的性能測試

2018-07-04 11:23:00 10852

10852

vivado設計套件資料

2017-10-31 09:49:03 44

44 Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。本文介紹了Tcl在Vivado中的基礎應用,希望起到拋磚引玉的作用,指引使用者在短時間內快速掌握相關技巧,更好地發揮Vivado在FPGA設計中的優勢。

2017-11-18 03:52:01 5363

5363

時鐘擴展對使用賽靈思Vivado設計套件的工程師來說是一個很大的挑戰,但不是一個不可逾越的障礙。隨著越來越多的賽靈思用戶開始使用Vivado?設計套件,部分用戶對未擴展時鐘表示困惑。那么什么是未擴展

2017-11-18 13:28:01 1079

1079 對于模擬CMOS(互補對稱金屬氧化物半導體)而言,兩大主要危害是靜電和過壓(信號電壓超過電源電壓)。了解這兩大危害,用戶便可以有效應對。

2018-05-07 10:49:00 2406

2406

現在的硬件設計中,大量的時鐘之間彼此相互連接是很典型的現象。為了保證Vivado優化到關鍵路徑,我們必須要理解時鐘之間是如何相互作用,也就是同步和異步時鐘之間是如何聯系。 同步時鐘是彼此聯系的時鐘。

2018-05-12 10:15:00 20926

20926 本文主要介紹了企業對MES系統硬件結構的兩大要求。

2018-06-04 08:00:00 10

10 時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習Vivado軟件時序分析的筆記,小編這里使用的是18.1版本的Vivado。 這次

2019-09-15 16:38:00 7943

7943

該視頻演示了如何使用Vivado IP Integrator組裝具有多個時鐘域的設計。

它顯示了Vivado中的設計規則檢查和功能如何幫助用戶自動執行此流程。

2018-11-27 07:40:00 4293

4293 了解report_design_analysis,這是一個新的Vivado報告命令,可以獨特地了解時序和復雜性特征,這些特性對于分析時序收斂問題很有價值。

2018-11-26 07:01:00 4107

4107 在Vivado Design Suite中,Vivado綜合能夠合成多種類型的屬性。在大多數情況下,這些屬性具有相同的語法和相同的行為。

2019-05-02 10:13:00 4772

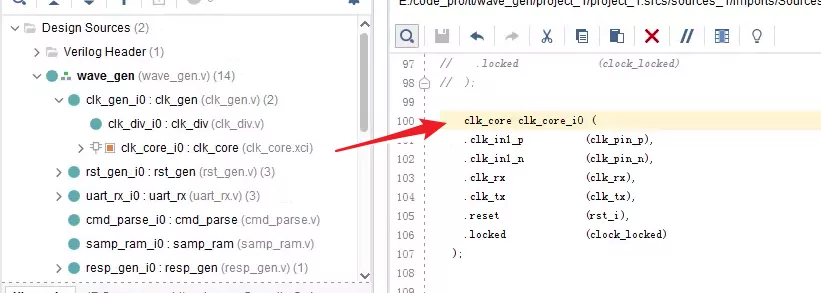

4772 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,下面就介紹一下在vivado2017.3中進行PL開發時調用IP的方法。

2018-12-22 14:26:38 5200

5200 在調試Vivado 過程中,由于生成的BIT文件過大,而我使用的FLASH又是32MBIT的,出現了FLASH過小,無法燒錄的情況。

2018-12-22 14:21:58 10167

10167 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,這是同步時序電路的關鍵,這時就需要使用到時鐘向導IP,下面就介紹一下在vivado中進行PL開發時調用IP的方法。

2018-12-22 15:14:38 10894

10894 vivado創立的某個文件夾路徑太長了,導致報錯。這個是本身工程目錄路徑名很長導致的。這個錯誤在windows下才會有,因為windows本身就限制了路徑長度,Linux下運行vivado不會這樣。

2019-03-30 09:39:44 8166

8166 關于Vivado Dashboard的功能可閱讀這篇文章(Vivado 2018.3這個Gadget你用了嗎)Vivado 2019.1的Dashboard功能進一步增強。

2019-06-12 14:49:24 9205

9205

部分重配置技術實現了動態可配置性,在切換設計中的某些部分時,其余部分還能繼續保持工作,完全不需停機,且幾乎不影響成本與開發時間。

2019-07-29 17:13:49 7127

7127 交互式時鐘域的交叉分析:該功能支持設計人員在設計早期階段調試CDC問題。結合Vivado設計套件的交互式時序分析和交叉探測特性,CDC分析功能可提供強大的時序分析和調試功能,并加速產品上市進程。

2019-08-01 09:14:54 2524

2524 想到要寫這一系列關于工具和方法學的小文章是在半年多前,那時候Vivado已經推出兩年,陸陸續續也接觸了不少客戶和他們的設計。我所在的部門叫做“Tools & Methodology Applications”,其實也是專為Vivado而設的一個部門。

2019-08-01 08:47:59 3465

3465 上面我們講的都是xdc文件的方式進行時序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進行時序約束:時序約束編輯器(Edit Timing Constraints )和時序約束向導(Constraints Wizard)。兩者都可以在綜合或實現后的Design中打開。

2020-03-08 17:17:00 20443

20443

Vivado HLS 2020.1將是Vivado HLS的最后一個版本,取而代之的是VitisHLS。那么兩者之間有什么區別呢? Default User Control Settings 在

2020-11-05 17:43:16 40985

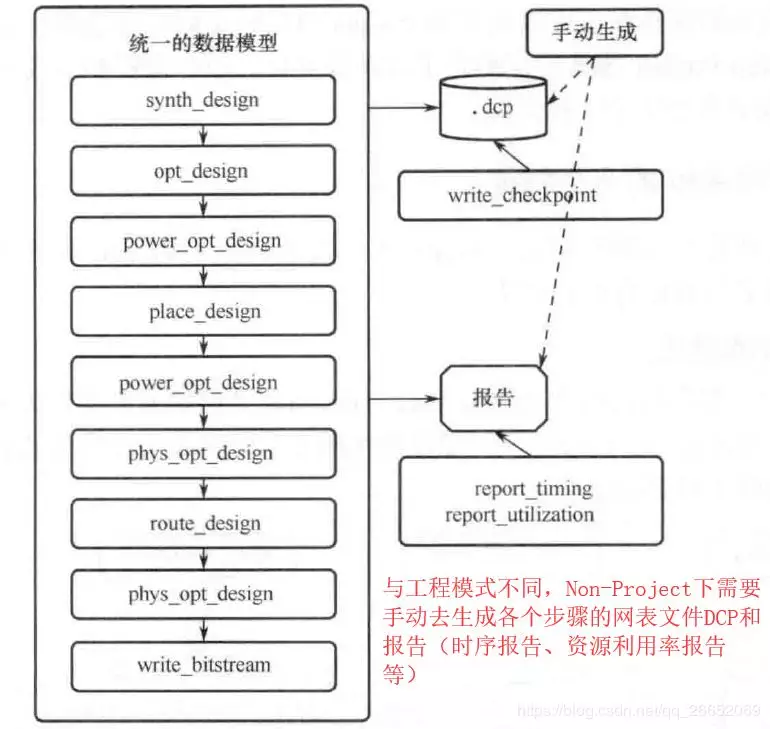

40985 Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程。

2021-03-22 11:39:53 51

51 Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程

2021-03-25 14:39:13 28

28 Vivado 的XDC設置輸出延時 Vivado 的XDC設置輸出延時,用于輸出伴隨時鐘和數據的,數據是由系統時鐘125M驅動,伴隨時鐘是由125M經過Pll相位移動-90度。 設置輸出時鐘

2021-06-09 17:28:01 5014

5014

,只有在時鐘的支持下,電子產品才能正常工作。 那么時鐘產品有哪些種類,它們分別有什么特性,工程師在選用的時候需要注意些什么呢,我們今天就來一起聊一聊。 時鐘產品的分類 時鐘產品主要分為兩大類,一類是異步時鐘產品,它的

2021-09-08 14:23:44 6921

6921 Vivado License Manager在使用Vivado License Manager時,如果通過如下圖所示方式指定license的路徑時,要保證路徑僅包含ASCII字符而沒有中文字

2021-09-12 15:15:19 7447

7447 和FPGA設計進行連接。由于VIO核與被監視和驅動的設計同步,因此應用于設計的時鐘約束也適用于VIO核內的元件。當使用這個核進行實時交互時,需要使用Vivado邏輯分析特性。 接下來將介紹VIO的原理及應用,內容主要包括設計原理、添加VIO核、生成比特流文件和下載并調試設計。 設計原理

2021-09-23 16:11:23 11260

11260

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 27

27 Vivado下set_multicycle_path的使用說明 vivado下多周期路徑約束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 對于7系列FPGA,需要對GT的這兩個時鐘手工約束:對于UltraScale FPGA,只需對GT的輸入時鐘約束即可,Vivado會自動對這兩個時鐘約束。

2022-02-16 16:21:36 2136

2136

在選定時有兩大標準可以參考,具體是什么標準相信各位沒有一個清晰的認知,今天這一期我公司來為各位全面講解關于NSK軸承選定的兩大標準。

2022-02-23 10:20:32 3154

3154 數字設計中,“時鐘”表示在寄存器間可靠地傳輸數據所需的參考時間。Vivado的時序引擎通過時鐘特征來計算時序路徑需求,通過計算裕量(Slack)的方法報告設計時序空余。時鐘必須有合適的定義,包含如下特性:

2022-04-20 10:40:48 10386

10386 Vivado 2022.1已正式發布,今天我們就來看看其中的一個新特性。

2022-07-03 17:00:25 3330

3330 Vivado可以導出腳本,保存創建工程的相關命令和配置,并可以在需要的時候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠遠小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級到Vivado 2020.2為例,討論如何升級Vivado工程腳本。

2022-08-02 10:10:17 2471

2471 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-19 16:20:51 2298

2298 在本文中我們將拆解分析AMD的“Ryzen 7000”和Intel的“第13代Intel Core”系列,以探索兩大芯片巨頭的演進之道。

2022-11-30 10:34:48 1699

1699 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

2023-02-02 10:14:01 5002

5002 了快速掌握 Vivado 使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏 升級到 Vivado 的信心。

2023-04-15 09:43:09 2185

2185 在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

溫度傳感器是一種廣泛應用于工業、醫療和家庭等領域的重要設備,用于測量環境溫度并將其轉化為可讀的電信號。根據溫度傳感器的工作原理和電氣特性,可以將溫度傳感器的測量方式分為兩大類:基于物理原理和基于電氣特性。本文將詳細介紹這兩大類溫度傳感器測量方式的原理、特點和應用場景。

2023-06-29 16:28:12 4745

4745 使用“時鐘校準去歪斜”時,在 Vivado 中會顯示下列消息以指明是否啟用該功能特性

2023-07-07 14:14:50 1157

1157

vivado開發軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學者進行仿真實驗。

2023-07-18 09:06:59 6642

6642

電子發燒友網站提供《Vivado設計套件用戶:使用Vivado IDE的指南.pdf》資料免費下載

2023-09-13 15:25:36 16

16 電子發燒友網站提供《Vivado Design Suite用戶指南:I/O和時鐘規劃.pdf》資料免費下載

2023-09-13 15:10:58 2

2 今天來聊一聊時鐘樹。首先我先講一下我所理解的時鐘樹是什么,然后介紹兩種時鐘樹結構。

2023-12-06 15:23:47 3288

3288 在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩

2024-01-05 14:31:06 4095

4095 Xilinx Vivado開發環境編譯HDL時,對時鐘信號設置了編譯規則,如果時鐘由于硬件設計原因分配到了普通IO上,而非_SRCC或者_MRCC專用時鐘管腳上時,編譯器就會提示錯誤。

2024-04-15 11:38:26 13022

13022 FRTC8563是一款實時時鐘(RTC)芯片,它采用SOP-8封裝,這種封裝形式使得芯片具有較小的體積和良好的引腳連接穩定性,便于集成到各種電子設備中。 以下是關于FRTC8563芯片的一些主要特性

2024-09-09 14:24:19 1976

1976

普強憑借其深厚的技術積累和創新能力,不斷推出高性能、高質量的產品和解決方案,成功榮登兩大榜單,這是對普強卓越的技術實力和應用層面的肯定。

2024-09-13 10:34:29 1860

1860 Vivado 2024.1已正式發布,今天我們就來看看新版本帶來了哪些新特性。

2024-09-18 10:30:39 3210

3210

從綜合角度看,Vivado 2024.1對SystemVerilog和VHDL-2019的一些特性開始支持。先看SystemVerilog。

2024-09-18 10:34:33 2647

2647

傳感器的特性可以分為靜態特性和動態特性兩大類,這兩類特性分別描述了傳感器在不同輸入條件下的輸出響應特點。下面將詳細介紹這兩類特性的主要參數。

2024-09-29 16:24:31 7994

7994 隨著 AMD Spartan UltraScale+ 系列現已投入量產,解鎖其功能集的最快途徑便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南資源。該集

2025-09-23 09:15:55 1390

1390

12月11日,中國歐盟商會 2025 年可持續商業獎頒獎典禮在上海舉行。博世中國憑借在綠色制造及社區共創兩大領域的持續深耕,一舉斬獲兩大重要獎項。

2025-12-22 15:06:27 390

390

電子發燒友App

電子發燒友App

評論