在 Vivado 2021.1 和 2021.1.1 中,默認啟用該功能。

在 Vivado 2021.2 和 2021.2.1 中,默認禁用該功能。

如果您當前使用“時鐘校準去歪斜”,那么時序所含的偏差結果是不正確的。

解決方案:

Vivado 2021.1 和 2021.1.1 使用“時鐘校準去歪斜”,因此您需要應用此處隨附的補丁。

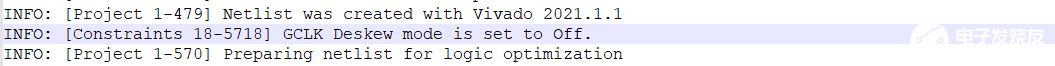

使用“時鐘校準去歪斜”時,在 Vivado 中會顯示下列消息以指明是否啟用該功能特性。

INFO: [Constraints 18-5720] The default GCLK Deskew mode is Calibrated.

應用隨附補丁后,需重新實現設計,您可檢查 Vivado log 日志以驗證是否已應用該補丁。

Vivado 2021.2.x 默認禁用該功能特性,因此不受影響。

| Vivado 版本 | 時鐘校準去歪斜默認設置 |

| 2020.3 及先前版本 | 關閉 |

| 2021.1 和 2021.1.1 | 開啟 *需補丁 |

| 2021.2 和 2021.2.1 | 關閉 |

| 2022.1 | 根據指定的器件和速度文件(請參閱下表),無需安裝補丁(請參閱Vivado 2022.1 - Versal 時鐘校準去歪斜的時序問題) |

| 2022.2 | 根據指定的器件和速度文件(請參閱下表),無需安裝補丁(請參閱000034546 - Vivado 2022.2 - Versal 時鐘校準去歪斜的時序問題) |

| 2022.2.2 | 根據指定的器件和速度文件(請參閱下表),無需安裝補丁(請參閱Vivado 2022.2.2 - Versal 時鐘校準去歪斜的時序問題) |

注釋:本答復記錄隨附的策略補丁還提供了適用于下列問題的補丁。此處提供了單個通用補丁以便于您使用。

Vivado 2021.1.x 和更低版本中的“時鐘管理器”上的“去歪斜檢相器”(即,使用 CLKIN_DESKEW 和 CLKFB_DESKEW 管腳)可能導致 Vivado 時序報告中出現錯誤的時序。

[1] 由于 CPM4 會將 DPLL 與去歪斜檢相器搭配使用,因此會受此問題影響,請參閱76947 - 適用于 PCI Express 的 Versal ACAP CPM 模式 (Vivado 2021.1) - 啟用 CPM4 到 PL 接口的設計中可能存在時序問題

[2] 如果 MMCM 使用 CLKIN_DESKEW 管腳或 CLKFB_DESKEW 管腳,則可能會受此問題影響,請參閱76908 - Vivado 2021.1 Vivado Versal 時鐘設置:MMCM 和 DPLL 的去歪斜邏輯時序錯誤

審核編輯:湯梓紅

-

時鐘

+關注

關注

11文章

1971瀏覽量

135004 -

Vivado

+關注

關注

19文章

857瀏覽量

71120 -

Versal

+關注

關注

1文章

173瀏覽量

8477

發布評論請先 登錄

VIVADO時序約束及STA基礎

AMD Versal自適應SoC內置自校準的工作原理

vivado:時序分析與約束優化

關于Vivado時序分析介紹以及應用

詳解Vivado時鐘的基礎知識

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部參考時鐘設計指南

Vivado時序約束中invert參數的作用和應用場景

Vivado 202x-Versal時鐘校準去歪斜的時序問題

Vivado 202x-Versal時鐘校準去歪斜的時序問題

評論