聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133590 -

IP

+關注

關注

5文章

1875瀏覽量

156347 -

時鐘

+關注

關注

11文章

1995瀏覽量

135178

發布評論請先 登錄

相關推薦

熱點推薦

Vivado時序約束中invert參數的作用和應用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號的有效邊沿或邏輯極性。

利用vivado實現對e200_opensource 蜂鳥E203一代的仿真

往下面找

雙擊打開Processor System Reset添加復位IP核

進行如圖修改,后確認。

點擊generate

同理,找到時鐘IP核:

先記得修改名字

改輸出時鐘值

再

發表于 10-31 06:14

E203移植genesys2(差分時鐘板)生成比特流文件全過程

在windows環境下實現移植流程,因為板子是差分時鐘,在最初移植的過程中時序報告一直出錯,經過調整分頻設置之后可以成功生成bit文件。本文章帶大家完成vivado階段所有工作,從源代碼到生成bit

發表于 10-27 07:16

采用xc7a200開發板移植蜂鳥E203

Vivado移植過程

本次板級驗證基于vivado.2020.02,完成工程建立,所用FPGA板型為:xc7a200tfbg484-2,主要挑幾個上板易錯點進行分享。

2.1 時鐘和復位IP

發表于 10-24 13:50

vcs和vivado聯合仿真

我們在做參賽課題的過程中發現,上FPGA開發板跑系統時,有時需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對添加了vivado

發表于 10-24 07:28

E203分享之DDR擴展方案實施流程(中)

的S00_AXI_ACLK、M00_AXI_ACLK,分別接系統頂層時鐘hfextclk、mig產生的用戶時鐘ui_clk,以此來實現跨時鐘域。

(2)例化DDR3模型(仿真的時候需要

發表于 10-24 07:25

Vivado浮點數IP核的握手信號

Vivado浮點數IP核的握手信號

我們的設計方案中,FPU計算單元將收到的三條數據和使能信號同步發給20多個模塊,同時只有一個模塊被時鐘使能,進行計算,但結果都會保留,發給數選。計

發表于 10-24 07:01

Vivado浮點數IP核的一些設置注意點

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一

發表于 10-24 06:25

如何在Vivado上仿真蜂鳥SOC,仿真NucleiStudio編譯好的程序

如標題所示,我們分享如何在Vivado上仿真蜂鳥SOC,仿真NucleiStudio編譯好的程序

具體步驟

1. 將蜂鳥soc移植到Vivado

只要將端口映射好,注意配置好時鐘和bank

發表于 10-21 11:08

AMD Vivado IP integrator的基本功能特性

我們還將帶您了解在 AMD Zynq UltraScale+ MPSoC 開發板與 AMD Versal 自適應 SoC 開發板上使用 IP integrator 時,兩種設計流程之間存在的差異。

LMK03318 具有單 PLL 的超低抖動時鐘發生器系列技術手冊

LMK03318器件是一款超低噪聲PLLATINUM?時鐘發生器,具有一個小數N頻率合成器,集成了VCO、靈活的時鐘分配和扇出,以及存儲在片上EEPROM中的引腳可選配置狀態。該器件可以為各種多千兆

黑芝麻智能跨域時間同步技術:消除多域計算單元的時鐘信任鴻溝

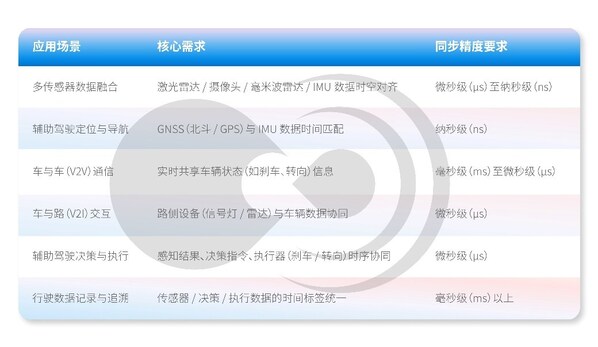

,并以黑芝麻智能武當 C1296 芯片為例,通過多方式同步實現多域高精度對齊,消除時鐘信任鴻溝的實測效果。 智能汽車的核心是通過多維度感知、實時決策和精準控制實現輔助駕駛與智能交互,而這一切的前提是?"時間基準一致",由于不同傳感器采集數據的頻率、機制不同,只有在時間

跨異步時鐘域處理方法大全

該方法只用于慢到快時鐘域的1bit信號傳遞。在Xilinx器件中,可以使用(* ASYNC_REG = "TRUE" *)標記,將兩個寄存器盡量靠近綜合,降低 亞穩態因導線延遲太大而傳播到第二個寄存器的可能性。

如何使用Vivado IP Integrator組裝具有多個時鐘域的設計

如何使用Vivado IP Integrator組裝具有多個時鐘域的設計

評論