時(shí)鐘周期約束,顧名思義,就是我們對(duì)時(shí)鐘的周期進(jìn)行約束,這個(gè)約束是我們用的最多的約束了,也是最重要的約束。

2020-11-19 11:44:00 6516

6516

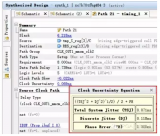

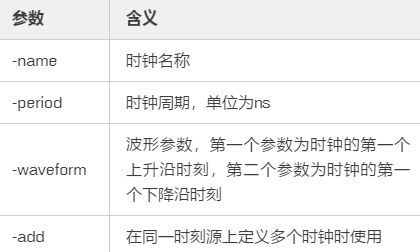

時(shí)序約束的目的就是告訴工具當(dāng)前的時(shí)序狀態(tài),以讓工具盡量?jī)?yōu)化時(shí)序并給出詳細(xì)的分析報(bào)告。一般在行為仿真后、綜合前即創(chuàng)建基本的時(shí)序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進(jìn)行最基本時(shí)序約束相關(guān)腳本。

2022-03-11 14:39:10 11063

11063 控制系統(tǒng)中補(bǔ)償環(huán)節(jié)經(jīng)常用到的三類誤差放大器,開關(guān)電源中通常稱為Type I,Type II,Type III。

2023-01-06 09:16:54 2825

2825 在FPGA設(shè)計(jì)中,時(shí)序約束的設(shè)置對(duì)于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的基礎(chǔ)知識(shí)。

2023-06-06 18:27:13 12757

12757

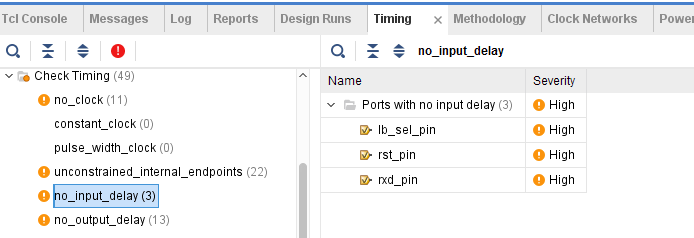

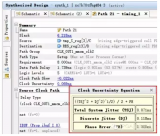

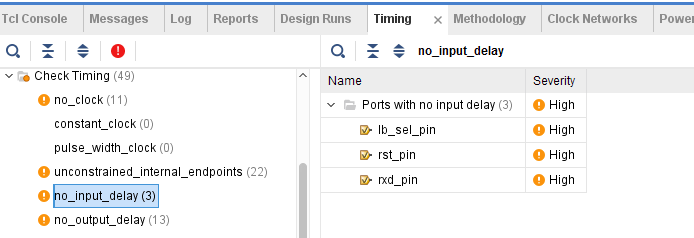

在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。

2023-06-12 17:29:21 4234

4234 前面幾篇FPGA時(shí)序約束進(jìn)階篇,介紹了常用主時(shí)鐘約束、衍生時(shí)鐘約束、時(shí)鐘分組約束的設(shè)置,接下來(lái)介紹一下常用的另外兩個(gè)時(shí)序約束語(yǔ)法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 3055

3055 可能無(wú)法滿足時(shí)序要求。 跨時(shí)鐘域信號(hào)的約束寫法 問題一: 沒有對(duì)設(shè)計(jì)進(jìn)行全面的約束導(dǎo)致綜合結(jié)果異常,比如沒有設(shè)置異步時(shí)鐘分組,綜合器對(duì)異步時(shí)鐘路徑進(jìn)行靜態(tài)時(shí)序分析導(dǎo)致誤報(bào)時(shí)序違例。 ??約束文件包括三類,建議用戶應(yīng)該將這三類約束

2023-08-01 09:18:34 3075

3075

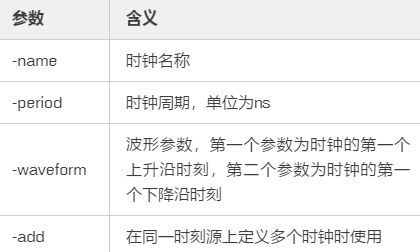

時(shí)鐘周期約束是用于對(duì)時(shí)鐘周期的約束,屬于時(shí)序約束中最重要的約束之一。

2023-08-14 18:25:51 1777

1777 在數(shù)字設(shè)計(jì)中,時(shí)鐘代表從寄存器(register)到寄存器可靠傳輸數(shù)據(jù)的時(shí)間基準(zhǔn)。

2024-01-04 09:16:09 5877

5877

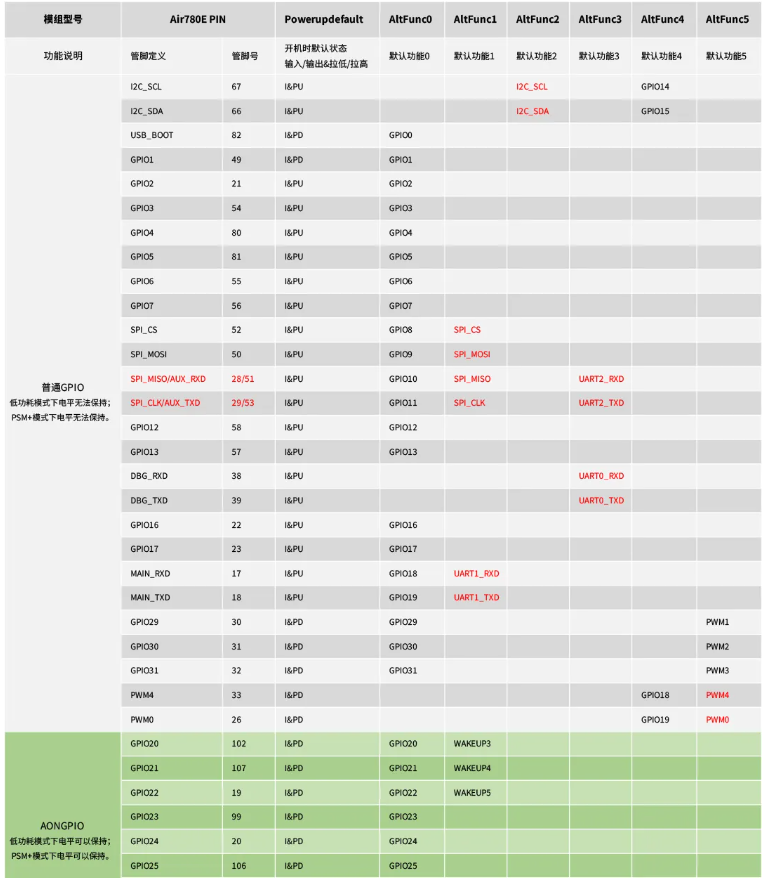

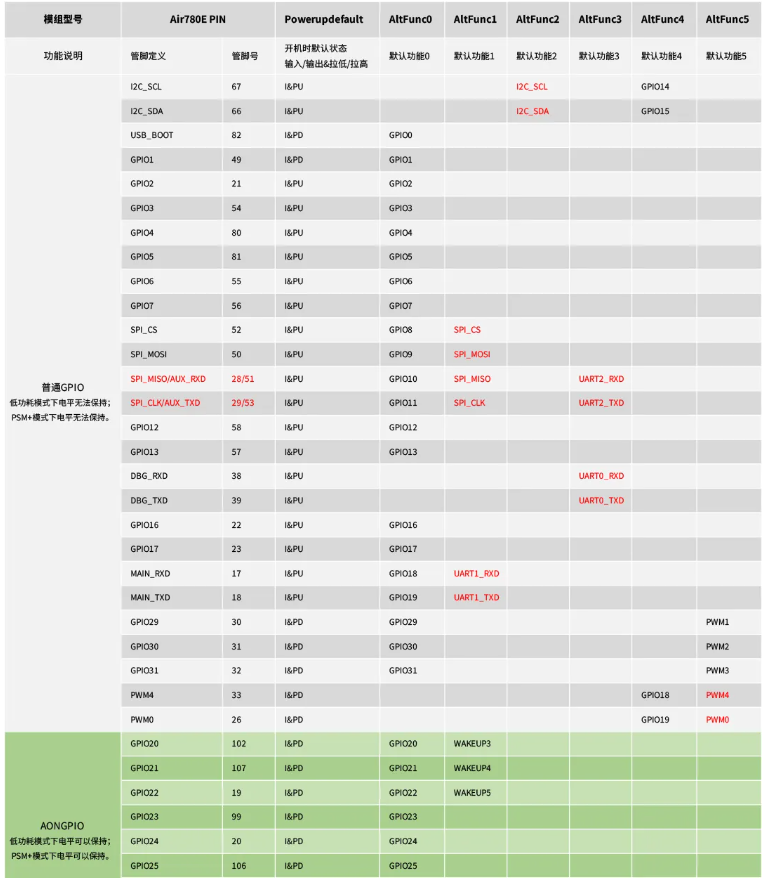

今天我們學(xué)習(xí)三類GPIO硬件設(shè)計(jì),這三類絕對(duì)是不可錯(cuò)過的,本文將把三類設(shè)計(jì)的重要性展示出來(lái):

2024-11-04 09:45:10 1978

1978

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要?jiǎng)?chuàng)建xdc文件設(shè)置時(shí)序約束。時(shí)序約束文件可以直接創(chuàng)建或添加已存在的約束文件,創(chuàng)建約束文件有兩種方式:Constraints Wizard和Edit Timing Constraints,在綜合后或?qū)崿F(xiàn)后都可以進(jìn)行創(chuàng)建。

2025-03-24 09:44:17 4561

4561

/ 177參考文獻(xiàn) / 178第6章 約束的管理 / 1796.1 基本時(shí)序理論 / 1796.2 兩類基本約束 / 1806.2.1 時(shí)鐘周期約束 / 1806.2.2 引腳分配 / 2016.3

2020-10-21 18:24:48

出于某種原因,Vivado忽略了我的約束文件,當(dāng)我嘗試在tcl控制臺(tái)中逐個(gè)輸入約束時(shí),我嘗試分配的每個(gè)端口都會(huì)出現(xiàn)以下錯(cuò)誤:set_property PACKAGE_PIN T19

2018-11-06 11:36:22

使用Vivado 2015.4我生成了兩個(gè)FIFO和一個(gè)Aurora Core。我收到與Vivado自動(dòng)生成的時(shí)序約束相關(guān)的嚴(yán)重警告。由于我的FIFO在整個(gè)設(shè)計(jì)中被多次使用,我需要一種讓Vivado

2018-11-02 11:30:10

(約束指令介紹)UG904 - Vivado Design Suite User Guide -Implementation UG906- Vivado Design Suite User Guide

2018-09-26 15:35:59

使用的是18.1版本的VIVADO。 這次的練習(xí)選擇的是ZYNQ的芯片,原本工程是工作在100MHz的時(shí)鐘,但是作為練習(xí),我們可以把時(shí)鐘調(diào)到一個(gè)極限的程度來(lái)進(jìn)行優(yōu)化。 首先,打開一個(gè)工程,更改一下時(shí)鐘頻率,使得工程

2018-08-22 11:45:54

開始新設(shè)計(jì)時(shí),最先需要選擇的參數(shù)是帶寬。根據(jù)應(yīng)用不同,有三類前端可供使用:基帶、帶通(或超奈奎斯特頻率,也稱窄帶)以及寬帶,如圖所示。基帶設(shè)計(jì)要求的帶寬是從DC(或低MHz區(qū))到奈奎斯特頻率(通常

2019-04-17 06:20:14

對(duì)電子產(chǎn)品的焊料是否有鉛無(wú)鉛非常關(guān)注,剛好工作中有遇見一個(gè)問題,我們自己研發(fā)的三類有源醫(yī)療器械中電路部分使用的是有鉛焊料,但是組裝完成后是完全密閉在內(nèi)部,不與人體的體液接觸,請(qǐng)哪個(gè)專家給指教下這樣的方案是否可行,是否有銘文規(guī)定三類醫(yī)療器械不能使用有鉛焊料等文件,謝謝

2022-11-29 14:20:54

;反面=>滴(印)膠(底面)=>貼裝元件=>烘干膠=>反面=>插元件=>波峰焊接 第三類 頂面采用穿孔元件, 底面采用表面貼裝元件. 工序: 滴(印)膠=>貼裝元件=>烘干膠=>反面=>插元件=>波峰焊接:

2018-11-26 17:04:00

約束優(yōu)化問題轉(zhuǎn)化為無(wú)約束優(yōu)化問題,從而使用無(wú)約束優(yōu)化算法。約束優(yōu)化問題大致分為三類:等式約束、不等式約束、等式+不等式約束。其數(shù)學(xué)模型為:等式約束s.t不等式約束s.t等式+不等式約束問題s.ts.t懲罰...

2021-08-17 08:09:26

在設(shè)計(jì)以太網(wǎng)中繼器時(shí),因?yàn)闆]有配置時(shí)鐘約束,導(dǎo)致中繼器工作不正常。后面根據(jù)手冊(cè)配置時(shí)鐘約束解決了此問題。

2016-10-07 18:51:24

FPGA的DCM模塊,40MHz時(shí)鐘輸入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。對(duì)40MHz時(shí)鐘添加了約束,系統(tǒng)不是會(huì)自動(dòng)對(duì)三個(gè)輸出時(shí)鐘進(jìn)行約束

2017-05-25 15:06:47

FPGA時(shí)序約束,總體來(lái)分可以分為3類,輸入時(shí)序約束,輸出時(shí)序約束,和寄存器到寄存器路徑的約束。其中輸入時(shí)序約束主要指的是從FPGA引腳輸入的時(shí)鐘和輸入的數(shù)據(jù)直接的約束。共分為兩大類:1、源同步系統(tǒng)

2015-09-05 21:13:07

Xilinx工具:vivado在該圖中,TX_CLK_i連接到pll_x1模塊的輸入時(shí)鐘。然后,pll_x1的輸出時(shí)鐘連接到ODDR。接下來(lái),ODDR的輸出引腳將連接到I / O引腳

2020-05-04 08:04:41

時(shí)鐘分組,再添加相應(yīng)的約束,例如:NET "clk_1" TNM_NET ="clk_syn";TIMESPEC "TS_clk_syn"

2017-03-09 14:43:24

秒(100 Mhz)關(guān)閉和打開一個(gè)LED,我這樣做是為了驗(yàn)證如何更改ZYNQ的時(shí)鐘頻率使用vivado的約束。這是我放在.xdc文件中生成不同的時(shí)鐘頻率set_property PACKAGE_PIN

2020-04-01 08:46:16

vivado默認(rèn)計(jì)算所有時(shí)鐘之間的路徑,通過set_clock_groups命令可禁止在所標(biāo)識(shí)的時(shí)鐘組之間以及一個(gè)時(shí)鐘組內(nèi)的時(shí)鐘進(jìn)行時(shí)序分析。 1.異步時(shí)鐘組約束聲明兩時(shí)鐘組之間為異步關(guān)系,之間不進(jìn)

2018-09-21 12:40:56

隨著我們?nèi)粘I钣闷纷兊迷絹?lái)越智能,設(shè)計(jì)工程師需要找到解決此類設(shè)備供電問題的可行途徑。而在物聯(lián)網(wǎng)(IoT)產(chǎn)品設(shè)計(jì)中,往往在設(shè)計(jì)周期的最后階段才會(huì)考慮電源問題。本文探討三類應(yīng)用的供電問題,以及低功耗微控制器在為聯(lián)網(wǎng)設(shè)備提供高效電源管理的重要性。

2021-03-02 06:39:13

耗材可大致分為三類:第一類是粉末類耗材,從三維打印技術(shù)的工作原理可以看出,其成型粉末需要具備材料成型性好、成型強(qiáng)度高、粉末粒徑較小、不易團(tuán)聚、滾動(dòng)性好、密度和孔隙率適宜、干燥硬化快等性質(zhì)。可選擇石英砂

2018-07-30 14:56:56

移動(dòng)終端中三類射頻電路的演進(jìn)方向詳解

2021-06-01 06:15:17

1、跨時(shí)鐘域信號(hào)的約束寫法 問題一:沒有對(duì)設(shè)計(jì)進(jìn)行全面的約束導(dǎo)致綜合結(jié)果異常,比如沒有設(shè)置異步時(shí)鐘分組,綜合器對(duì)異步時(shí)鐘路徑進(jìn)行靜態(tài)時(shí)序分析導(dǎo)致誤報(bào)時(shí)序違例。 約束文件包括三類,建議用戶應(yīng)該將

2022-11-15 14:47:59

大家好!~向大家請(qǐng)教個(gè)問題,這個(gè)穩(wěn)壓電源的一類二類三類是怎樣區(qū)分的呢?請(qǐng)大家?guī)兔獯鹣拢嘀x!~

2018-08-13 08:54:21

電話網(wǎng)上傳真三類機(jī)承受傳輸損傷能力的基本要求 YD/T 589 1996:

2009-08-20 12:10:14 14

14 LC振蕩器設(shè)計(jì)與調(diào)試中三類常見問題

對(duì)LC振蕩器設(shè)計(jì)與調(diào)試中的三類常見問題(不起振、不穩(wěn)定和缺少儀器)

2010-04-17 16:18:07 79

79 By Adam Taylor 在之前的博客中介紹了Vivado的基本時(shí)序約束,時(shí)序約束定義了系統(tǒng)頻率或自己所定義的時(shí)鐘頻率。為建立良好的時(shí)序約束,下一步是需要建立時(shí)鐘路徑之間關(guān)系的定義。這樣

2017-02-08 03:46:35 357

357 最近有些朋友在ISE中做的V7項(xiàng)目需要切換到vivado來(lái),但導(dǎo)入代碼后,導(dǎo)入約束時(shí),發(fā)現(xiàn)vivado不再支持UCF文件,如果手抄UCF約束到 VIVADO 的 XDC 約束,不僅浪費(fèi)時(shí)間,而且容易出錯(cuò),這里介紹一種方法可以實(shí)現(xiàn)兩種約束的切換。

2017-03-24 13:54:36 9459

9459

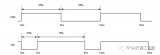

Vivado時(shí)鐘的兩大特性--時(shí)鐘延遲和時(shí)鐘的不確定性。

2017-11-17 11:38:01 6283

6283

Xilinx?的新一代設(shè)計(jì)套件 Vivado 中引入了全新的約束文件 XDC,在很多規(guī)則和技巧上都跟上一代產(chǎn)品 ISE 中支持的 UCF 大不相同,給使用者帶來(lái)許多額外挑戰(zhàn)。Xilinx 工具專家

2017-11-18 03:59:01 4097

4097 維修電工等電力作業(yè)人員在作業(yè)過程中遇到最多的相信就是TN式供電系統(tǒng),根據(jù)保護(hù)零線是否和工作零線分開, TN式供電系統(tǒng)又可分為三類:TN-C供電系統(tǒng), TN-S供電系統(tǒng), TN-C-S供電系統(tǒng)。下面我們就詳細(xì)的解釋一下這三類TN式供電系統(tǒng)。

2018-01-26 14:00:00 35006

35006 本文首先對(duì)錳酸鋰、磷酸亞鐵鋰、三元材料做了個(gè)簡(jiǎn)單的概述,其次對(duì)三類鋰電池材料特性進(jìn)行了對(duì)比,最后闡述了三類鋰電池材料的應(yīng)用。

2022-05-06 12:01:20 23600

23600 在機(jī)器學(xué)習(xí)(Machine learning)領(lǐng)域。主要有三類不同的學(xué)習(xí)方法:監(jiān)督學(xué)習(xí)(Supervised learning)、非監(jiān)督學(xué)習(xí)(Unsupervised learning)、半監(jiān)督學(xué)習(xí)(Semi-supervised learning)。

2018-05-07 09:09:01 15018

15018 介紹FPGA約束原理,理解約束的目的為設(shè)計(jì)服務(wù),是為了保證設(shè)計(jì)滿足時(shí)序要求,指導(dǎo)FPGA工具進(jìn)行綜合和實(shí)現(xiàn),約束是Vivado等工具努力實(shí)現(xiàn)的目標(biāo)。所以首先要設(shè)計(jì)合理,才可能滿足約束,約束反過來(lái)檢查

2018-06-25 09:14:00 7199

7199 維持嗎? 1、Vivado基本操作流程 2、時(shí)序基本概念 3、時(shí)序基本約束和流程 4、Baselining時(shí)序約束 5、CDC時(shí)序約束 6、I/O時(shí)序 7、例外時(shí)序約束 8、時(shí)序收斂?jī)?yōu)化技術(shù)

2018-08-06 15:08:02 722

722 該視頻演示了如何使用Vivado IP Integrator組裝具有多個(gè)時(shí)鐘域的設(shè)計(jì)。

它顯示了Vivado中的設(shè)計(jì)規(guī)則檢查和功能如何幫助用戶自動(dòng)執(zhí)行此流程。

2018-11-27 07:40:00 4293

4293 了解如何將Altera的SDC約束轉(zhuǎn)換為Xilinx XDC約束,以及需要更改或修改哪些約束以使Altera的約束適用于Vivado設(shè)計(jì)軟件。

2018-11-27 07:17:00 5883

5883 最近今年隨著小米的發(fā)展,目前小米音響主要分為藍(lán)牙音箱、智能音箱、擴(kuò)音器三類。接下里我會(huì)從小米音響的優(yōu)點(diǎn)與缺點(diǎn)兩方面說一下小米音響。

2019-01-02 11:10:58 32688

32688 時(shí)鐘域之間存在單位和多位混合的跨時(shí)鐘域路徑,那么對(duì)于單位的跨時(shí)鐘域路徑要明確的對(duì)每一條路徑設(shè)置偽路徑來(lái)約束,對(duì)于多位的跨時(shí)鐘域路徑,使用set_max_delay –datapath_only 和 set_bus_skew約束。如果時(shí)鐘是同步的,不需要任何約束。vivado的靜態(tài)時(shí)鐘分析工具會(huì)自動(dòng)的設(shè)定路徑的時(shí)序。

2019-07-15 15:35:23 7191

7191 由國(guó)家的復(fù)旦大學(xué)電子學(xué)院的張教授,帶領(lǐng)種團(tuán)隊(duì)人員,做研發(fā)的第三類存儲(chǔ)技術(shù),實(shí)現(xiàn)了最顛覆性的一次飛躍,開創(chuàng)第三類的存儲(chǔ)技術(shù),它的速度要比U盤快10000倍左右。

2019-10-09 14:09:17 948

948 XDC 是 Xilinx Design Constraints 的簡(jiǎn)寫,但其基礎(chǔ)語(yǔ)法來(lái)源于業(yè)界統(tǒng)一的約束規(guī)范SDC。XDC 在本質(zhì)上就是 Tcl 語(yǔ)言,但其僅支持基本的 Tcl 語(yǔ)法如變量、列表

2020-01-30 17:29:00 10876

10876 首先來(lái)看什么是時(shí)序約束,泛泛來(lái)說,就是我們告訴軟件(Vivado、ISE等)從哪個(gè)pin輸入信號(hào),輸入信號(hào)要延遲多長(zhǎng)時(shí)間,時(shí)鐘周期是多少,讓軟件PAR(Place and Route)后的電路能夠

2020-01-28 17:34:00 4750

4750

這是我國(guó)首個(gè)應(yīng)用人工智能技術(shù)的三類器械過審。而人工智能三類器械過審的通過,對(duì)于醫(yī)療AI行業(yè)來(lái)說是一件里程碑的事件。

2020-01-16 13:45:50 2992

2992 上面我們講的都是xdc文件的方式進(jìn)行時(shí)序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進(jìn)行時(shí)序約束:時(shí)序約束編輯器(Edit Timing Constraints )和時(shí)序約束向?qū)В–onstraints Wizard)。兩者都可以在綜合或?qū)崿F(xiàn)后的Design中打開。

2020-03-08 17:17:00 20443

20443

需要進(jìn)行故障診斷和排除的三類最常見的光伏系統(tǒng)問題與面板、負(fù)載和逆變器有關(guān)。

2020-03-15 16:37:00 4988

4988 疫情大考之后,國(guó)內(nèi)首張AI影像輔助診斷領(lǐng)域三類證近日迎來(lái)破局。獲悉,6月12日,國(guó)家藥品監(jiān)督管理局發(fā)布消息,安德醫(yī)智旗下BioMind“天醫(yī)智”的顱內(nèi)腫瘤磁共振影像輔助診斷軟件通過了NMPA三類醫(yī)療器械審批。

2020-06-16 16:33:34 1599

1599 Vivado IDE約束管理器將任何已編輯的約束保存回XDC文件中的原始位置,但不會(huì)保存在Tcl腳本中。 任何新約束都保存在標(biāo)記為目標(biāo)的XDC文件的末尾。

2020-11-13 10:53:38 5530

5530

Timing Report中提示warning,并不會(huì)導(dǎo)致時(shí)序錯(cuò)誤,這也會(huì)讓很多同學(xué)誤以為這個(gè)約束可有可無(wú)。 但其實(shí)這種想法是不對(duì)的,比如在很多ADC的設(shè)計(jì)中,輸出的時(shí)鐘的邊沿剛好是數(shù)據(jù)的中心位置,而如果我們不加延遲約束,則Vivado會(huì)默認(rèn)時(shí)鐘和數(shù)據(jù)是對(duì)齊的。 對(duì)

2020-11-14 10:34:35 4075

4075

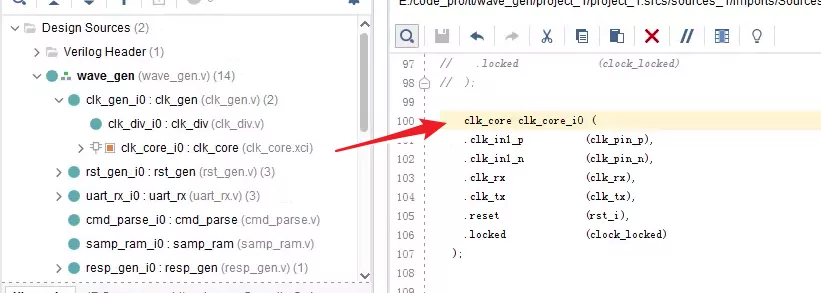

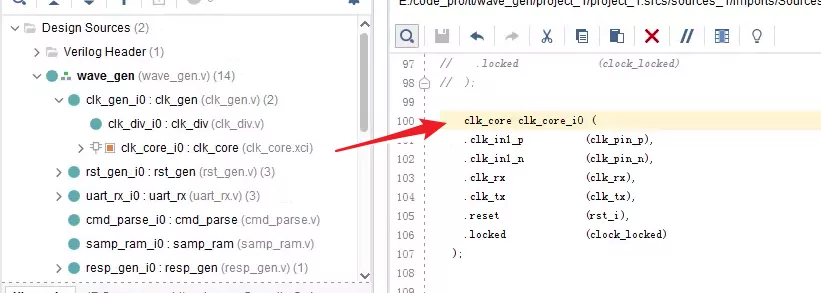

約束衍生時(shí)鐘 系統(tǒng)中有4個(gè)衍生時(shí)鐘,但其中有兩個(gè)是MMCM輸出的,不需要我們手動(dòng)約束,因此我們只需要對(duì)clk_samp和spi_clk進(jìn)行約束即可。約束如下

2020-11-17 16:28:05 3234

3234

1 I/O延遲約束介紹 要在設(shè)計(jì)中精確建模外部時(shí)序,必須為輸入和輸出端口提供時(shí)序信息。Xilinx Vivado集成設(shè)計(jì)環(huán)境(IDE)僅在FPGA邊界內(nèi)識(shí)別時(shí)序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 6236

6236 對(duì)工業(yè)機(jī)器人來(lái)說,主要有三類編程方法:在線編程、離線編程以及自主編程三類。

2020-11-10 17:47:25 21882

21882 create_clock:和其他FPGA EDA tool一樣,在vivado中timing約束越全越好,越細(xì)越好,而place約束可以很粗略或者省略調(diào)。約束中最常用的語(yǔ)句就是

2021-01-12 17:31:39 21

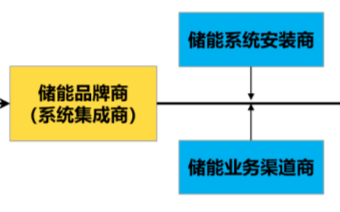

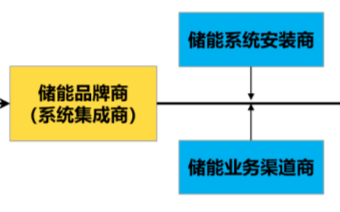

21 ? ? 摘要 國(guó)內(nèi)儲(chǔ)能市場(chǎng)中主要有三類玩家,第一類是儲(chǔ)能品牌商,第二類為鋰電池企業(yè),第三類為從光伏、風(fēng)電等領(lǐng)域跨界而來(lái)的企業(yè)。 在全球新能源浪潮下,“新能源+儲(chǔ)能”將是能源結(jié)構(gòu)調(diào)整戰(zhàn)略中重要的組合拳

2021-02-11 09:33:00 5137

5137

電子發(fā)燒友網(wǎng)為你提供智能設(shè)備三類應(yīng)用的供電問題資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-03 08:54:34 6

6 愚人節(jié),醫(yī)療AI也有重磅消息。 雷鋒網(wǎng)《醫(yī)健AI掘金志》消息,4月1日,醫(yī)療AI公司深睿醫(yī)療和推想科技分別宣布,獲得自己的第二張國(guó)內(nèi)NMPA三類證——肺炎CT影像輔助分診與評(píng)估軟件。 目前,這是國(guó)內(nèi)

2021-04-07 10:51:08 3999

3999

很對(duì)人在使用Vivado時(shí)喜歡使用多個(gè)約束文件對(duì)整個(gè)工程進(jìn)行約束,同時(shí)Vivado允許設(shè)計(jì)者使用一個(gè)或多個(gè)約束文件。雖然使用一個(gè)約束文件對(duì)于一個(gè)完整的編譯流程來(lái)說看似更方便,但是在一些情況下,這會(huì)

2021-10-13 16:56:54 7907

7907 Vivado下set_multicycle_path的使用說明 vivado下多周期路徑約束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 對(duì)于7系列FPGA,需要對(duì)GT的這兩個(gè)時(shí)鐘手工約束:對(duì)于UltraScale FPGA,只需對(duì)GT的輸入時(shí)鐘約束即可,Vivado會(huì)自動(dòng)對(duì)這兩個(gè)時(shí)鐘約束。

2022-02-16 16:21:36 2136

2136

運(yùn)轉(zhuǎn)中的檢查項(xiàng)目有三類軸承的滾動(dòng)聲、振動(dòng)、溫度、潤(rùn)滑的狀態(tài)等,具體情況如下。

2022-05-18 10:25:47 1179

1179 【問題8.1】 VIVADO的時(shí)鐘約束向?qū)Вo(wú)法找到時(shí)鐘,如下圖所示,位置1中應(yīng)該要識(shí)別出時(shí)鐘。

2022-06-10 06:28:34 2746

2746

XDC約束可以用一個(gè)或多個(gè)XDC文件,也可以用Tcl腳本實(shí)現(xiàn);XDC文件或Tcl腳本都要加入到工程的某個(gè)約束集(set)中;雖然一個(gè)約束集可以同時(shí)添加兩種類型約束,但是Tcl腳本不受Vivado工具管理,因此無(wú)法修改其中的約束;

2022-06-30 11:27:23 5420

5420 FPGA端掛載DDR時(shí),對(duì)FPGA引腳的約束和選擇并不是隨意的,有一定的約束規(guī)則,一般可以通過利用vivado工具中的pin assignment去選擇合適的位置輔助原理圖設(shè)計(jì)。

2022-07-03 17:20:44 6346

6346 時(shí)鐘周期約束:?時(shí)鐘周期約束,顧名思義,就是我們對(duì)時(shí)鐘的周期進(jìn)行約束,這個(gè)約束是我們用的最多的約束了,也是最重要的約束。

2022-08-05 12:50:01 5047

5047 文中,作者結(jié)合電化學(xué)表征及TEM表征提出了三類可以促進(jìn)催化降解性能的原電池結(jié)構(gòu):第一類原電池由非晶組織中的富鐵團(tuán)簇和貧鐵團(tuán)簇組成的;第二類原電池由硼與非晶組織組成;第三類原電池由不同的晶粒組成。

2022-08-16 10:21:38 1551

1551 提到位置約束,我們會(huì)想到手工布局的方式,即畫Pblock,將指定模塊放入相應(yīng)Pblock內(nèi),這既是面積約束又是位置約束,但顯然這種約束是較為具體的位置約束。這種方式需要工程師有一定的經(jīng)驗(yàn),有時(shí)還需要

2022-11-17 11:47:46 3587

3587 數(shù)字設(shè)計(jì)中的時(shí)鐘與約束 本文作者 IClearner 在此特別鳴謝 最近做完了synopsys的DC workshop,涉及到時(shí)鐘的建模/約束,這里就來(lái)聊聊數(shù)字中的時(shí)鐘(與建模)吧。主要內(nèi)容如下所示

2023-01-28 07:53:00 4179

4179

今天介紹的是vivado的三種常用IP核:時(shí)鐘倍頻(Clocking Wizard),實(shí)時(shí)仿真(ILA),ROM調(diào)用(Block Memory)。

2023-02-02 10:14:01 5002

5002 本文介紹上述三類互連設(shè)計(jì)的各種技巧,內(nèi)容涉及器件安裝方法、布線的隔離以及減少引線電感的措施等等。

2023-03-09 12:30:45 894

894 隨著自由曲面光學(xué)元件的廣泛應(yīng)用,其相應(yīng)的制造技術(shù)得到了廣泛的發(fā)展。針對(duì)不同口徑、不同類型、不同材質(zhì)的自由曲面光學(xué)元件,其相應(yīng)的加工方法根據(jù)加工原理可以分為三類。

2023-03-22 14:52:35 3222

3222 當(dāng)設(shè)計(jì)存在多個(gè)時(shí)鐘時(shí),根據(jù)時(shí)鐘的相位和頻率關(guān)系,分為同步時(shí)鐘和異步時(shí)鐘,這兩類要分別討論其約束

2023-04-06 14:34:28 1679

1679

示波器大致可分為模擬、數(shù)字和組合三類。

2023-04-19 16:19:06 2200

2200 很多人詢問關(guān)于約束、時(shí)序分析的問題,比如:如何設(shè)置setup,hold時(shí)間?如何使用全局時(shí)鐘和第二全局時(shí)鐘(長(zhǎng)線資源)?如何進(jìn)行分組約束?如何約束某部分組合邏輯?如何通過約束保證異步時(shí)鐘域之間

2023-05-29 10:06:56 1537

1537

有關(guān)穩(wěn)壓器的知識(shí),穩(wěn)壓器的三類常見故障問題,一類是輸出電壓不正常,一類是不穩(wěn)壓,第三類是開機(jī)無(wú)輸出、無(wú)電壓指示或無(wú)啟動(dòng)以及過壓或欠壓保護(hù),下面具體來(lái)了解下。

2023-06-09 17:48:56 4440

4440 FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

今天介紹一下,如何在Vivado中添加時(shí)序約束,Vivado添加約束的方法有3種:xdc文件、時(shí)序約束向?qū)В–onstraints Wizard)、時(shí)序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 6081

6081

Vivado綜合默認(rèn)是timing driven模式,除了IO管腳等物理約束,建議添加必要的時(shí)序約束,有利于綜合邏輯的優(yōu)化,同時(shí)綜合后的design里面可以評(píng)估時(shí)序。

2023-07-03 09:03:19 1424

1424 幫到不經(jīng)常看群消息的小伙伴,另一方面也算是我們的技術(shù)積累。 Q:Vivado的Implementation階段約束報(bào)警告? ? [Vivado?12-627]?No?clocks?matched

2023-08-08 14:10:48 2217

2217 電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:使用約束.pdf》資料免費(fèi)下載

2023-09-13 15:48:39 2

2 電子發(fā)燒友網(wǎng)站提供《EPS消防應(yīng)急電源常見三類質(zhì)量問題.pdf》資料免費(fèi)下載

2023-11-14 10:11:59 0

0 穩(wěn)壓電源一類、二類和三類是指按照供電設(shè)備的直流輸出偏差范圍和抗干擾能力對(duì)穩(wěn)壓電源進(jìn)行分類的方法。下面將詳細(xì)介紹穩(wěn)壓電源一類、二類和三類的區(qū)別。 一、穩(wěn)壓電源的概念和分類: 穩(wěn)壓電源是一種將輸入電流

2023-12-28 17:54:43 13744

13744 變壓器是一種常見的電氣設(shè)備,主要用于改變交流電壓或電流的大小。根據(jù)用途的不同,變壓器可以分為以下三類:電力變壓器、儀用變壓器和特殊用途變壓器。本文將對(duì)這三類變壓器進(jìn)行詳細(xì)的介紹。 一、電力變壓器

2024-01-04 16:29:27 5754

5754 數(shù)控系統(tǒng)是數(shù)控機(jī)床的核心部分,它負(fù)責(zé)接收加工程序,進(jìn)行數(shù)據(jù)處理和運(yùn)算,控制機(jī)床各軸的運(yùn)動(dòng),實(shí)現(xiàn)對(duì)工件的加工。根據(jù)數(shù)控系統(tǒng)的結(jié)構(gòu)和功能,我們可以將其分為三類類型:開環(huán)控制系統(tǒng)、閉環(huán)控制系統(tǒng)和半閉環(huán)控制

2024-07-01 11:06:43 4457

4457 電路的兩類約束通常指的是電氣約束和物理約束。這兩類約束在電路設(shè)計(jì)和分析中起著至關(guān)重要的作用。 一、電氣約束 電氣約束的概念 電氣約束是指在電路設(shè)計(jì)和分析中,需要遵循的電氣原理和規(guī)律。這些原理和規(guī)律

2024-08-25 09:34:51 2556

2556 有時(shí)我們對(duì)時(shí)序約束進(jìn)行了一些調(diào)整,希望能夠快速看到對(duì)應(yīng)的時(shí)序報(bào)告,而又不希望重新布局布線。這時(shí),我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時(shí)序約束。如果調(diào)整

2024-10-24 15:08:40 1602

1602

今天教大家一些關(guān)于硬件設(shè)計(jì)的的技巧,只要掌握好三類GPIO,輕松玩好硬件設(shè)計(jì)。

2024-11-05 12:22:49 1477

1477

的輸出,對(duì)于Ultrascale和Ultrascale+系列的器件,定時(shí)器會(huì)自動(dòng)地接入到GT的輸出。 1.2 約束設(shè)置格式 主時(shí)鐘約束使用命令create_clock進(jìn)行創(chuàng)建,進(jìn)入Timing

2024-11-29 11:03:42 2322

2322

Vivado中時(shí)序分析工具默認(rèn)會(huì)分析設(shè)計(jì)中所有時(shí)鐘相關(guān)的時(shí)序路徑,除非時(shí)序約束中設(shè)置了時(shí)鐘組或false路徑。使用set_clock_groups命令可以使時(shí)序分析工具不分析時(shí)鐘組中時(shí)鐘的時(shí)序路徑,使用set_false_path約束則會(huì)雙向忽略時(shí)鐘間的時(shí)序路徑

2025-04-23 09:50:28 1079

1079

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論