作者:Mculover666 1.實驗目的 用HDL語言+Vivado創建一個掛載在AXI總線上的自定義IP核 2.實驗步驟 2.1.創建一個新的項目 ? ? 2.2.調用Create

2020-12-21 16:34:14 4566

4566

Xilinx的FIR IP核屬于收費IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個人學習,現在網絡上流傳的license破解文件在破解Vivado的同時也破解

2025-03-01 14:44:19 2709

2709

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個發展趨勢。許多公司推薦使用現成的或經過測試的宏功能模塊、IP核,用來增強

2011-07-06 14:15:52

你好,我在使用Xilinx網站的IP核時遇到了一些問題。我已經下載了Vivado Webpack,也為此同時下載了IP-Core的許可證。Vivado Webpack工作正常,但我看不到我下載

2018-12-24 13:50:01

turbo 譯碼器IP核沒有輸出,不知道哪里出了問題,有經驗的小伙伴幫忙看看啊

搭建了turbo 譯碼器IP核測試工程,用Matlab產生的數據源,調用turbo編碼器生成編碼數據,將編碼后的數據給

2025-06-23 17:39:24

發生IP核鎖定,一般是Vivado版本不同導致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態報告 Report -》 Report IP Status 2)點擊

2021-01-08 17:12:52

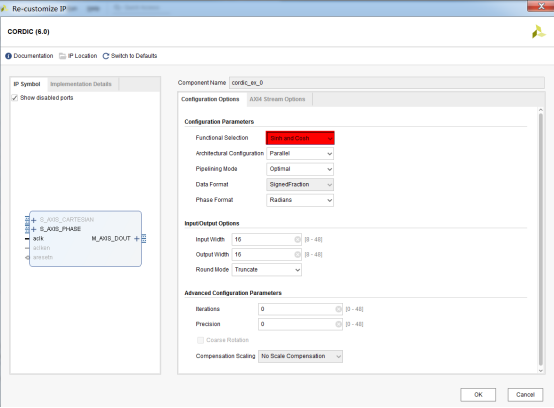

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一個IP核實

2025-10-24 06:25:22

Vivado浮點數IP核的握手信號

我們的設計方案中,FPU計算單元將收到的三條數據和使能信號同步發給20多個模塊,同時只有一個模塊被時鐘使能,進行計算,但結果都會保留,發給數選。計算單元還需接受

2025-10-24 07:01:36

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

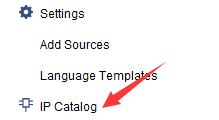

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:39:13

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:40:28

vivado的三速以太網IP核接口太多了,完全不知道應該怎么用,哪位大佬能發我一份設計或者仿真嗎?簡單的就好

2021-04-15 12:58:00

vivado中,怎么將e203內核源代碼封裝成ip核,并添加總線?

2025-11-10 07:22:49

vivado導入其他版本的項目的時候,IP核被鎖,無法解開,請問該如何解決。

使用軟件:vivado 2019.2

導入項目使用版本:vivado 2018

2024-11-08 21:29:58

請教一下,vivado怎么把帶ip核的工程進行封裝,保證代碼不可見,可以通過端口調用。我嘗試了以下方法,ippackage,如果要在另一個程序里調用,也要提供源代碼;另一個方法是將網表文件edf文件與端口聲明結合,這種方法只能實現不帶ip核的封裝

2017-07-14 09:18:30

vivado三種常用IP核的調用當前使用版本為vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點

2021-07-29 06:07:16

將程序從低版本的vivado搬移到高版本的vivado的時,直接在高版本的vivado下升級軟核中的各個IP后,在綜合過程中報錯。在低版本的vivado平臺下,原程序已經完成編譯。

2020-11-14 20:57:13

在vivado生成ip核后缺少一大片文件,之前都是正常的,殺毒軟件也一直沒有開,突然就變成這樣了,還請大神告知是怎么回事?

2021-05-18 20:34:08

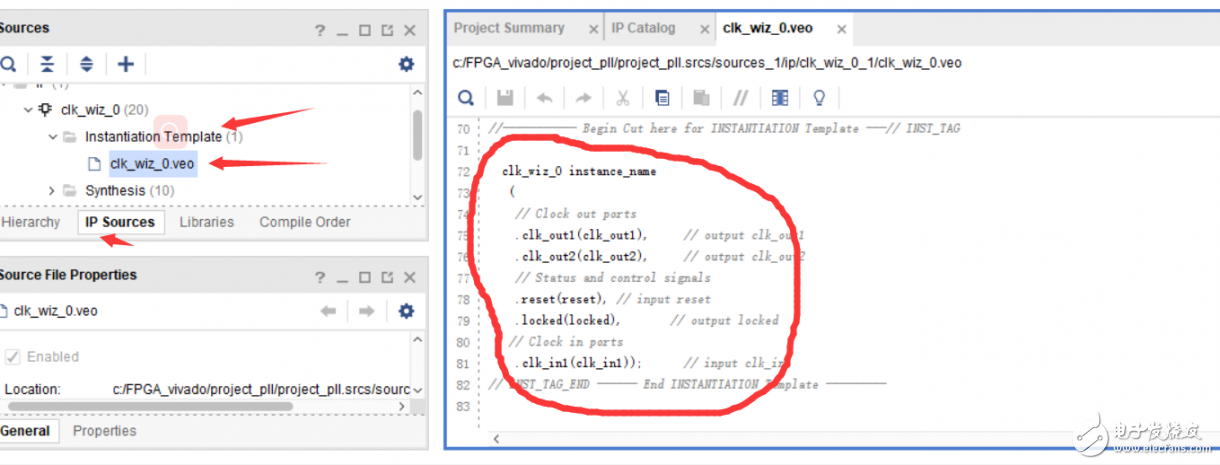

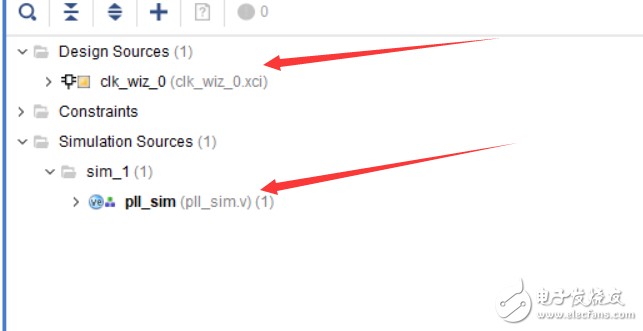

本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

2021-03-02 07:22:13

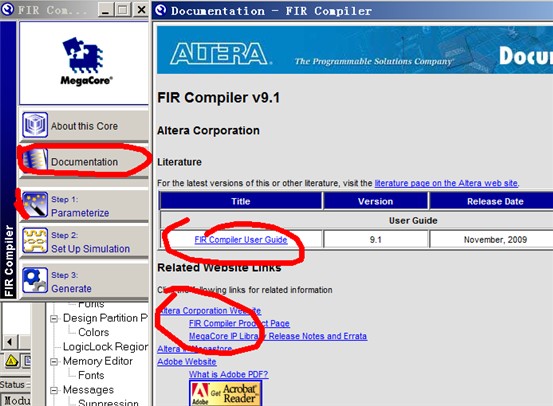

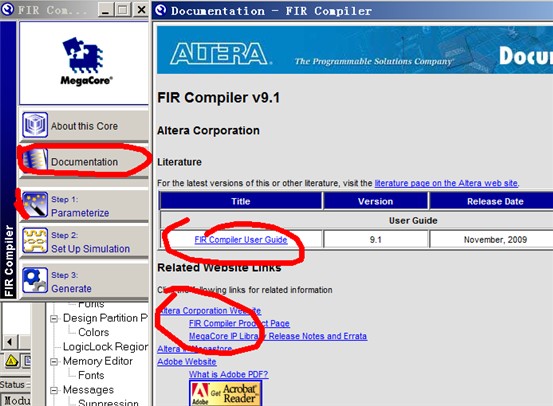

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

BRAM IP核包括哪幾種類型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 1.使用 (1)首先建立工程,這個就不

2019-06-03 09:09:51

用vivado2019.2建立工程,工程中調用cordic IP核進行atan求解,功能仿真時正常且滿足要求;綜合時正常;實現時報錯提示多重驅動。

如果經cordic計算后的輸出值不用于后續的操作

2023-06-06 17:17:37

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

為什么vivado2016調用MIG ip核會收到嚴重警告呢?這個critical warning會有影響嗎,要怎么解決呢?

2021-10-18 09:41:21

本例程主要使用Vivado 調用ROM IP核,用含有正弦曲線的.coe文件初始化ROM,最終通過仿真實現波形的顯示 一、首先建立工程 二、選擇芯片的型號 我

2021-01-08 17:16:43

請問我修改完MIG IP核以后,該如何進行更新呢?搗鼓了半天,要么更新為源代碼,要么就是提示我自己添加的端口不存在

2018-11-12 19:46:15

請問有哪位大神,可以幫忙破解一個vivado的IP核。不勝感激,聯系QQ397679468

2017-11-24 09:30:30

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規模的設計應用,適宜的IP核對開發能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調用這些模塊

2024-04-29 21:01:16

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

%91/vivado2016-%E8%B0%83%E7%94%A8MIG-ip%E6%A0%B8%E4%B8%A5%E9%87%8D%E8%AD%A6%E5%91%8A-Project-1-19/m-p/884989鏈接不管用的話就按照下圖自己找吧。回復: vivado2016 調用MIG ip核

2021-07-28 07:16:27

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

如何使用這個用IP核生成的xdc文件?是否有任何標準的方法來使用它們擺脫crtical警告?非常感謝。以上來自于谷歌翻譯以下為原文When we create some IP cores

2019-03-26 12:29:31

IP實例之一也不會點亮按鈕。也許我需要以某種方式同時選擇兩者?我瀏覽了用戶指南,找不到任何有關如何更新內核的信息。我確實看到了一些通過Vivado / tcl進行升級的替代方案作為一種解決方法,如果

2019-11-04 09:26:19

的經驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現在有一些經驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

`玩轉Zynq連載21——Vivado中IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https://pan.baidu.com

2019-09-04 10:06:45

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-16 11:42:55

`錯誤提示截圖放在二樓,用vivado14.4寫了個1×8和8×8矩陣相乘的程序,調用了64個ip核乘法器,IO口用的有些多。綜合和實現網表都能成功,就是仿真總是提示這兩個錯誤,仔細檢查了幾遍程序

2020-04-26 19:21:25

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 1.使用 (1)首先建立工程,這個就不

2013-01-16 11:09:00 84064

84064

本文基于xilinx 的IP核設計,源于音頻下采樣這一需求。 創建vivado工程 1. 首先打開vivado,創建一個新的project(勾選create project subdirectory

2017-02-08 02:25:09 5883

5883

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

在linux系統上實現vivado調用VCS仿真教程 作用:vivado調用VCS仿真可以加快工程的仿真和調試,提高效率。 前期準備:確認安裝vivado軟件和VCS軟件 VCS軟件最好安裝

2018-07-05 03:30:00 12369

12369

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10744

10744 的IP工程,缺省情況下,IP工程的名字為magaged_ip_project。在這個工程中生成所需要的IP,之后把IP添加到FPGA工程中。Xilinx推薦使用第二種方法,尤其是設計中調用的IP較多時或者采用團隊設計時。

2017-11-18 04:22:58 6145

6145 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-28 15:49:58 2339

2339 在給別人用自己的工程時可以封裝IP,Vivado用封裝IP的工具,可以得到像xilinx的ip一樣的可以配置參數的IP核,但是用其他工程調用后發現還是能看到源文件,如何將工程源文件加密,暫時沒有找到方法,如果知道還請賜教。

2018-06-26 11:33:00 8932

8932 大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 本人需要利用Vivado軟件中的DDS核生成一個正弦信號。由于后期還要生成線性調頻信號,如果直接編寫代碼生成比特流文件下載到板子上進行驗證會使工作的效率大大下降,所有想利用Vivado軟件功能仿真,這樣可以極大的提高效率。Vivado軟件自帶仿真功能,不需要對IP核進行特別的處理,所以很方便。

2018-07-13 08:32:00 10266

10266 第二項是器件添加,只有選擇了相應的器件,你的IP核才能在那個器件里被使用。單擊器件,右鍵——Add——Add Family Explicitiy,于是便可以選擇要適用的器件系列了。

2018-11-12 14:31:16 11311

11311 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,這是同步時序電路的關鍵,這時就需要使用到時鐘向導IP,下面就介紹一下在vivado中進行PL開發時調用IP的方法。

2018-12-22 15:14:38 10894

10894 ,發現Modelsim10.5的版本也是可以使用的。筆者嘗試過Modelsim10.4,發現該版本不支持。所以需要使用Vivado2017.3來調用Modelsim的工程師,需要選擇正確的Modelsim版本。否者將調用失敗。

2019-03-30 09:51:46 18140

18140

.coe格式的數據文件簡介 在Vivado中,對rom進行初始化的文件是.coe文件.它的格式如下: memory_initialization_radix=10

2020-11-20 15:01:24 7939

7939

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

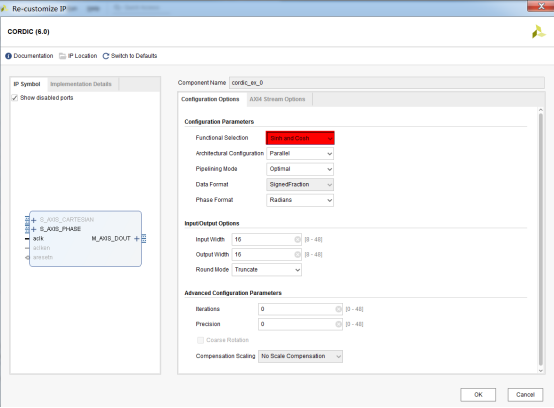

13270 由于Verilog/Vhdl沒有計算exp指數函數的庫函數,所以在開發過程中可利用cordic IP核做exp函數即e^x值;但前提要保證輸入范圍在(-pi/4—pi/4)。在cordic核中e^x = sinh + cosh所以在配置cordic時點選sinh and cosh即可 如下圖

2022-07-25 16:51:14 5458

5458

Vivado2017.2 中BRAM版本為 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5種類型:Single-port RAM

2021-03-10 06:15:56 19

19 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有

2021-03-22 10:31:16 5360

5360 本次使用Vivado調用DDS的IP進行仿真,并嘗試多種配置方式的區別,設計單通道信號發生器(固定頻率)、Verilog查表法實現DDS、AM調制解調、DSB調制解調、可編程控制的信號發生器(調頻調相)。

2021-04-27 16:33:06 8131

8131

vivado提供了DDS IP核可以輸出正余弦波形,配置方法如下

2021-04-27 15:52:10 12327

12327

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。

2021-04-27 15:45:12 25681

25681

Vivado調用Questa Sim或ModelSim仿真中存在的一些自動化問題的解決方案。 Vivado調用Questa Sim仿真中存在的一些問題 首先說明一下Modelsim與Questa

2021-09-02 10:12:06 10120

10120

IP核目前的IP設計已成為目前FPGA設計的主流方法之一,應用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數據塊。IP核在SoC中的集成方式及應用場景,芯片設計中的IP核具有特定功能的可復用的標準性和可交易性,已經成為集成電路設計技術的核心與精華。

2021-10-01 09:08:00 3100

3100 本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用

2022-03-16 14:14:19 2713

2713

在FPGA實際的開發中,官方提供的IP并不是適用于所有的情況,需要根據實際修改,或者是在自己設計的IP時,需要再次調用時,我們可以將之前的設計封裝成自定義IP,然后在之后的設計中繼續使用此IP。因此本次詳細介紹使用VIvado來封裝自己的IP,并使用IP創建工程。

2022-04-21 08:58:05 7941

7941 在本篇博文中,我們將學習如何導出 IP 以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運行工程。

2022-07-08 09:34:00 4213

4213 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 4676

4676 移植之后,.v和.vhd代碼保持不變,但ISE和vivado的ip核是不一樣的,有很多都不一樣,這里我遇到的是其中一個 : DDS

2022-09-05 15:46:26 5010

5010 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

2023-02-02 10:14:01 5002

5002 有一天使用Vivado調用questasim(modelsim估計也一樣),仿真報錯

2023-05-08 17:12:56 5357

5357 最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 4032

4032

使用VCS仿真Vivado里面的IP核時,如果Vivado的IP核的仿真文件只有VHDL時,仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 3576

3576

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

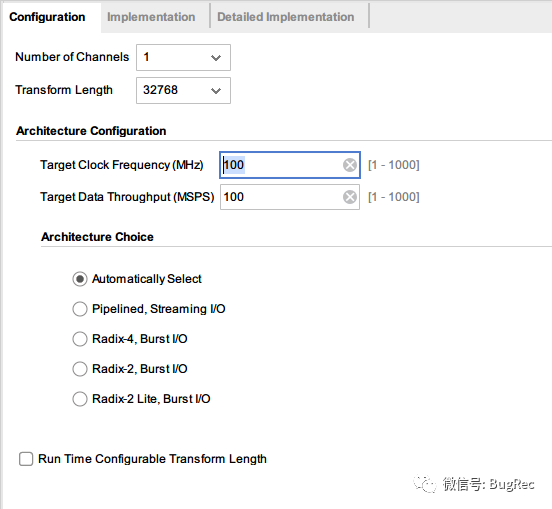

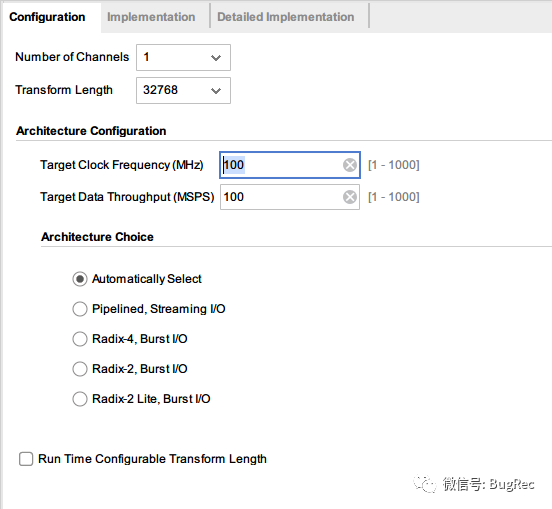

這里做最簡單的設置,打開Vivado,點開IP Catalog,找到FFT IP核。

2023-06-19 14:38:50 3580

3580

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調用Modelsim進行仿真,下面將介紹如何對vivado進行配置并調用Modelsim進行仿真,在進行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 5396

5396

DDS(Direct Digital Frequency Synthesizer) 直接數字頻率合成器,本文主要介紹如何調用Xilinx的DDS IP核生成某一頻率的Sin和Cos信號。

2023-07-24 11:23:29 8502

8502

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 3014

3014

Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

2023-09-17 15:37:31 3220

3220

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5640

5640

電子發燒友App

電子發燒友App

評論