隨著 AMD Spartan UltraScale+ 系列現已投入量產,解鎖其功能集的最快途徑便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南資源。該集成型設計套件能通過一鍵式時序收斂,將設計從 RTL 階段推進到硬件階段,從而幫助縮短迭代周期。讓我們來看看該設計套件提供的功能特性。

統一流程,減少迭代次數

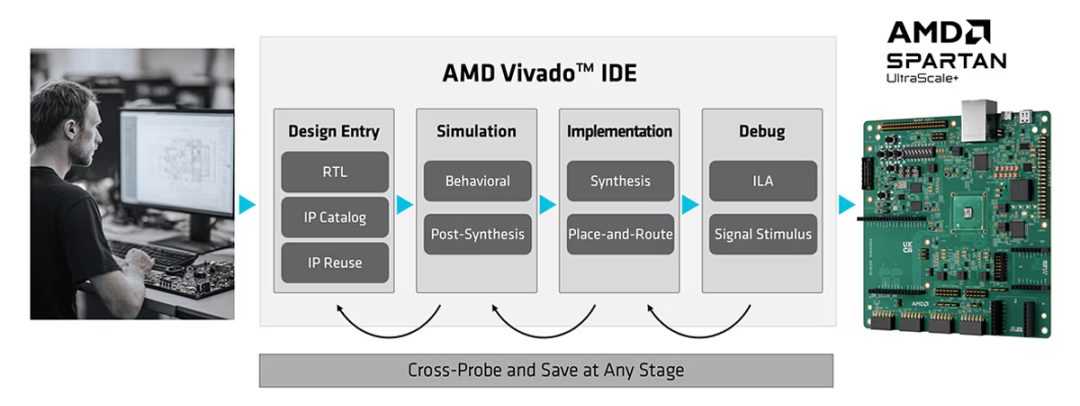

Vivado 工具流程將仿真、綜合、實現、時序分析和調試整合到單個工具鏈中——并集成了流程的每個階段:

通過多種途徑的設計輸入:RTL 導入、通過 IP Integrator 進行基于塊的設計,或使用 AMD Vitis 統一軟件平臺導入使用 C/C++ 或 MathWorks開發的 IP。

仿真:使用XSIM在 RTL、綜合后和布局布線后進行功能驗證,以及硬件協同仿真。

綜合與布局布線:內置的免許可綜合功能與布局布線協同工作,助力實現 QoR 目標,包括引導流程和機器學習驅動算法,以快速滿足時序收斂要求。

調試:使用ChipScope以系統內硬件速度采集和分析信號——直接在 Vivado 工具環境進行。

典型的設計循環可從 RTL 或基于 IP 的輸入開始,通常使用 Vivado 工具中的HDL 模板來創建計數器、狀態機和其他常見結構,然后通過仿真進行驗證。在實現之前,約束向導和I/O 規劃查看器可幫助確認時鐘、I/O 布局和約束分組。設計檢查點支持在任何階段暫停和恢復綜合或布局布線。隨著 PCB 設計的演進,后期更改(例如 I/O 交換或引腳重新分配)可以通過增量編譯高效處理。

快速迭代對于小型 FPGA 設計至關重要,每天進行多次迭代是常態,因此集成型流程避免了管理來自不同工具的中間文件的需求。面向 Spartan UltraScale+ 的 Vivado 設計套件教程視頻演示了如何在一個項目中構建、仿真和實現完整的設計。

一鍵式時序收斂

要在一鍵式流程中滿足時序要求而無需手動調整 RTL,這是 FPGA 設計人員面臨的一個常見挑戰。為了滿足 FMAX(最大工作頻率)目標而進行多次設計變更,一直是導致項目延誤的常見原因。猜測哪些布局布線方案可能會改善 FMAX,然后等待數小時才能看到結果,并期盼獲得更好的結果,這些過程可能會陷入“無休止”的循環。

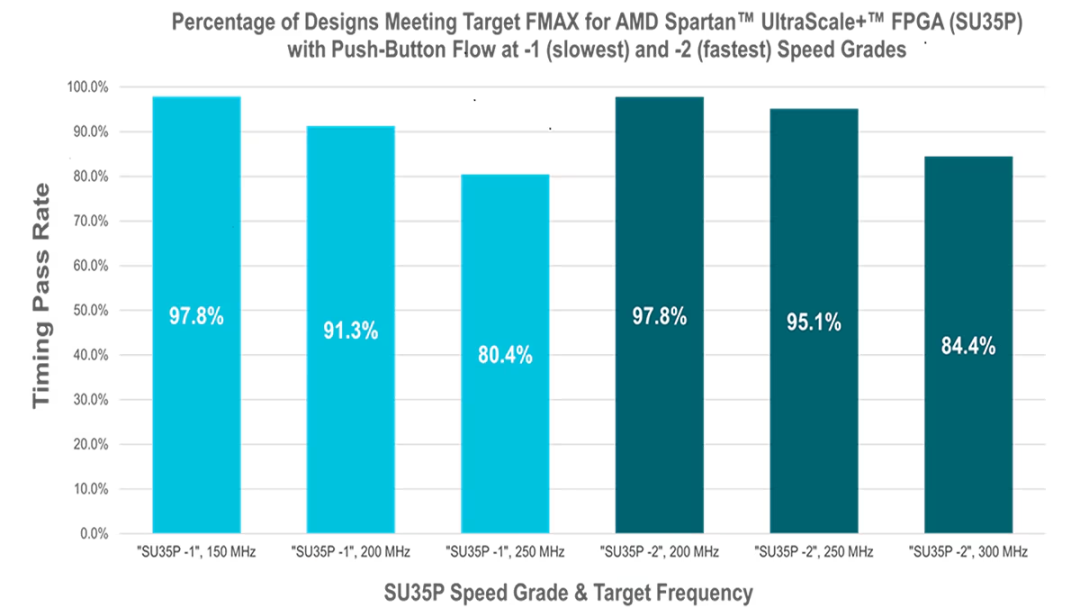

Vivado 設計套件經過多個版本的調優,以滿足最復雜 FPGA 和自適應 SoC 的 FMAX目標。Vivado 設計套件 2025.1 版本和 Spartan UltraScale+ SU35P FPGA 結合使用時采用一鍵式流程,可在至高 250 MHz 的頻率下實現平均 92% 的通過率1,無需任何設計變動,從而消除了為滿足時序要求而反復試驗的周期。設計人員可以依賴基于約束的流程、自動管道化和預優化的布局布線策略,無需深厚的工具專業知識或手動調優。

廣泛、優化的 IP 產品組合助力快速開發

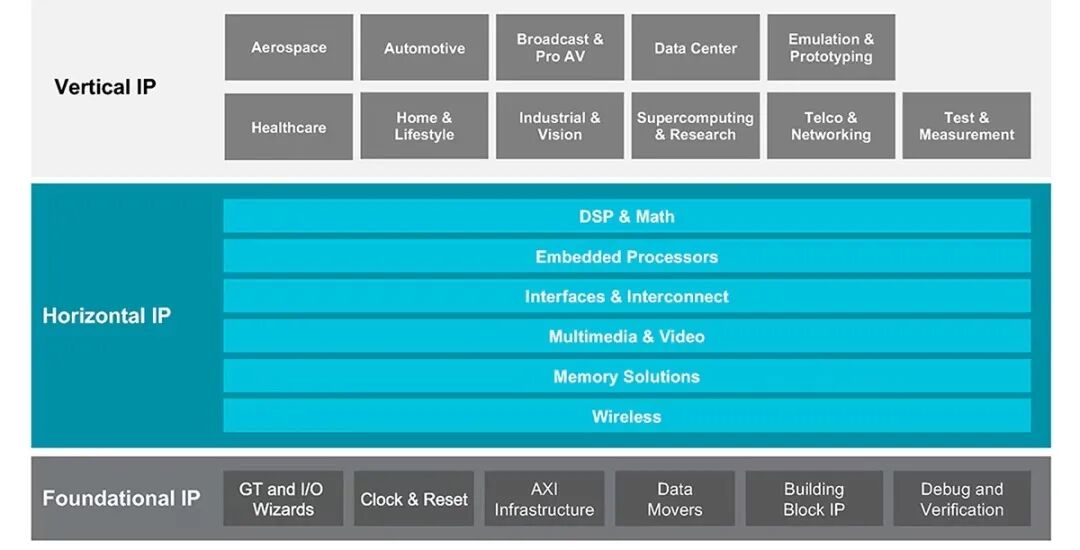

IP 復用是加速設計的關鍵,Vivado IP 編目提供了顯著的領先優勢——近 400 個預驗證的軟核,使您能夠快速構建基礎架構并專注于IP 差異化。Spartan UltraScale+ 高密度器件中新的硬塊(包括 LPDDR4x/5 內存控制器和 PCIeGen4 )可助力進一步加速設計收斂,提供交鑰匙性能。通過消除對可編程邏輯的需求,高端器件中的硬 IP 預計可將整體能效提升至多 60%2。

在 Vivado IP 目錄中,您可以探索和實例化各種 IP——從基礎組件到水平子系統(如 DSP、接口和內存控制器),一直到針對工業、汽車、視覺和其他市場的應用量身定制的垂直 IP。

利用 VivadoIP Integrator這一通過 AXI 互連自動化簡化組裝的圖形界面,能將硬 IP、軟 IP 和自定義 RTL 相結合。

準備開始了嗎

Spartan UltraScale+ 器件現已投入量產,AMD Vivado 設計套件的完全支持現已開放免費下載。無論您是 Vivado 工具新手、Spartan UltraScale+ 系列新手,還是兩者兼而有之,專用資源頁面都包含教程、視頻、參考設計和文檔,助您快速上手。

1. 基于 AMD 在 2025 年 7 月進行的最差負時序裕量測試,針對 AMD Vivado 設計套件 2025.1 版和 Spartan UltraScale+ SU35P FPGA,分別在 -1(最慢)速度等級(150MHz -250Mhz)下對 46 個設計,以及在 -2(最快)速度等級(200MHz – 250Mhz)下對 41 個設計進行了測試。結果因器件、設計、配置和其他因素而有所不同。 (VIV-018)

2. 預測基于 AMD 在 2024 年 1 月進行的內部分析,使用基于 AMD Artix UltraScale+ AU7P FPGA 邏輯規模計數的總功耗計算(靜態功耗加動態功耗),借助 Xilinx 功耗估算器 (XPE) 工具 2023.1.2 版本,估算 AMD Spartan UltraScale+ SU200P FPGA 與 AMD Artix 7 7A200T FPGA 的總功耗對比。總功耗接口結果可能會在最終產品發布后,因配置、設計、使用和其他因素而有所不同。(SUS-006)

2025 年超威半導體公司版權所有。保留所有權利。AMD、AMD Arrow 標識、Spartan、UltraScale+、Vivado 及其組合為超威半導體公司的商標。PCIe 是 PCI-SIG 公司的注冊商標。本文中使用的其他產品名稱僅用于識別目的,可能是其各自所有者的商標。特定 AMD 技術可能需要第三方的支持或激活。支持的特性可能因操作系統而異。請與系統制造商確認具體特性。任何技術或產品都無法做到完全安全。

-

amd

+關注

關注

25文章

5692瀏覽量

140105 -

仿真

+關注

關注

55文章

4498瀏覽量

138418 -

Vivado

+關注

關注

19文章

858瀏覽量

71200

原文標題:Vivado 用于 Spartan UltraScale+:快速設計由此開始

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AMD Power Design Manager 2025.2版本現已發布

全新AMD Vitis統一軟件平臺2025.2版本發布

AMD Vivado Design Suite 2025.2版本現已發布

FPGA初學者求助

AMD Vivado IP integrator的基本功能特性

新一代嵌入式開發平臺 AMD嵌入式軟件和工具2025.1版現已推出

AMD 2025.1版嵌入式軟件和工具的新增功能

AMD Power Design Manager 2025.1現已推出

全新AMD Vitis統一軟件平臺2025.1版本發布

AMD Spartan UltraScale+ FPGA 開始量產出貨

AMD Vivado Design Suite 2025.1現已推出

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

Helix QAC 2025.1 重磅發布!MISRA C:2025? 100%覆蓋

英特爾OpenVINO 2025.1版本發布

代碼靜態測試工具Perforce QAC 2025.1新特性

AMD Vivado設計套件2025.1版本的功能特性

AMD Vivado設計套件2025.1版本的功能特性

評論