?在FPGA的時序約束中,主時鐘約束是第一步就要做的,主時鐘通常有兩種情形:一種是時鐘由外部時鐘源提供,通過時鐘引腳進入FPGA,該時鐘引腳綁定的時鐘為主時鐘:另一種是高速收發器(GT)的時鐘RXOUTCLK或TXOUTCLK。對于7系列FPGA,需要對GT的這兩個時鐘手工約束:對于UltraScale FPGA,只需對GT的輸入時鐘約束即可,Vivado會自動對這兩個時鐘約束。

??對于進入到IP Core(比如MMCM)的主時鐘,只有我們在IP Core中指定了時鐘頻率,那么Vivado會自動產生一個約束文件來約束該輸入的主時鐘。

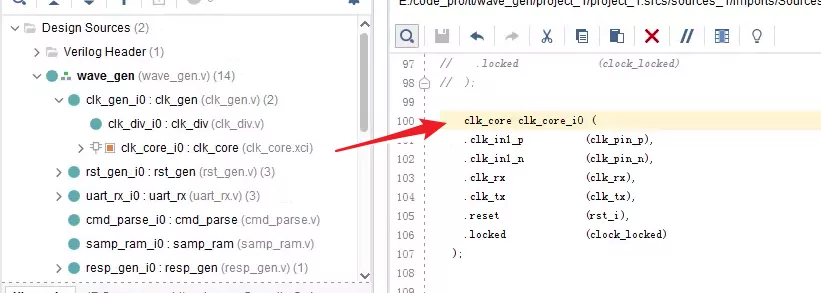

??我們以Vivado自帶的wave_gen工程為例,該工程中輸入一對差分的時鐘信號,進入到MMCM中,我們無需再對這個主時鐘添加約束。

可以看到,綜合后這個時鐘已經被約束了:

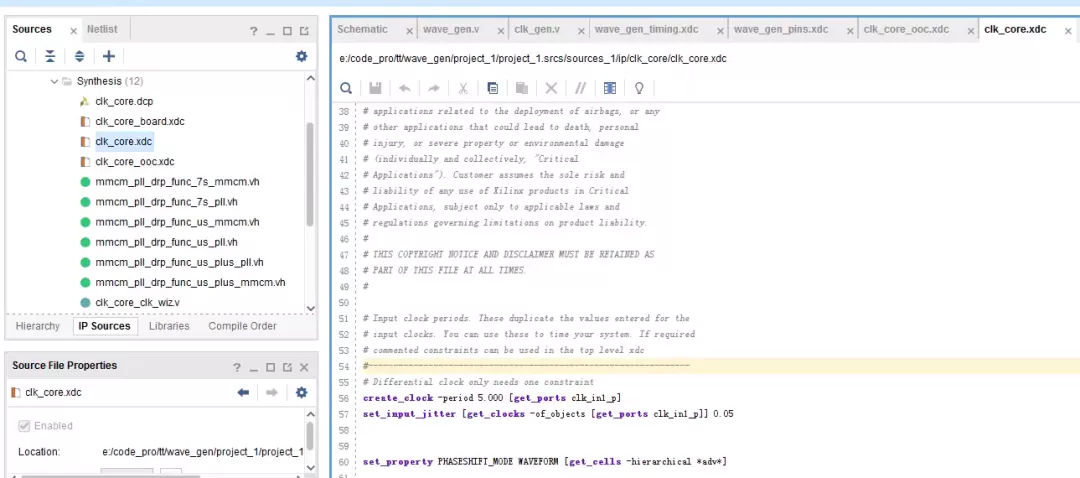

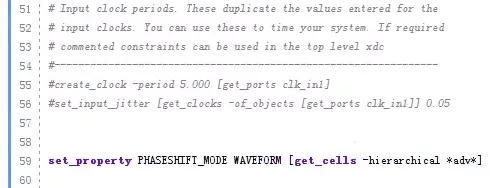

這是因為該ip生成的xdc文件中,已經包含了對這個主時鐘的約束,如下圖:

所以很多同學可能誤以為只要是進了IP Core的主時鐘,都不需要再手動添加約束了。

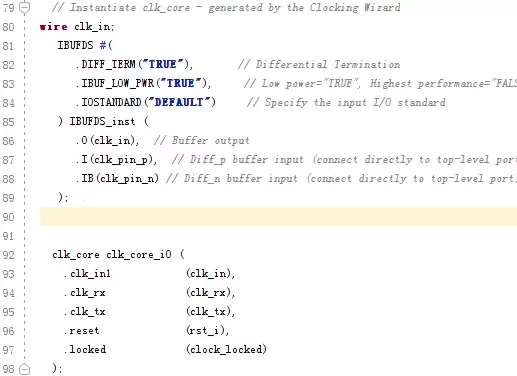

??但如果收入的差分時鐘先經過了IBUFDS,然后再以單獨的形式進入了MMCM:

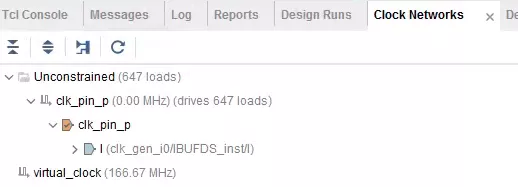

綜合后,可以看到該時鐘是沒有被約束的:

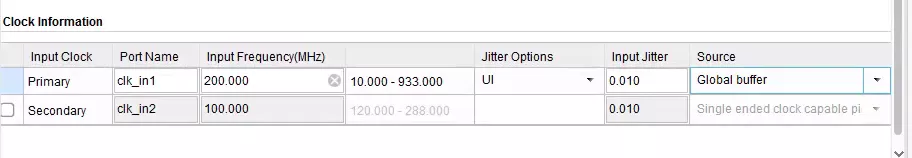

此時由于輸入時鐘并非來自管腳,所以Source選擇為Global Buffer

再看剛剛的clk_core.xdc文件,已經沒有產生主時鐘的約束了:

為什么會沒有這個約束了呢?因為輸入的時鐘并非來自管腳,IP Core并不知道從哪個pin輸入的,所以就無法添加主時鐘的約束,此時就需要我們再手動添加約束。

審核編輯:符乾江

-

FPGA

+關注

關注

1663文章

22483瀏覽量

638627 -

Vivado

+關注

關注

19文章

860瀏覽量

71345

發布評論請先 登錄

輸入引腳時鐘約束_Xilinx FPGA編程技巧-常用時序約束詳解

系統c盤滿了怎么清理不需要文件

開源RISC-V處理器(蜂鳥E203)學習(二)修改FPGA綜合環境(移植到自己的Xilinx FPGA板卡)

E203移植genesys2(差分時鐘板)生成比特流文件全過程

采用xc7a200開發板移植蜂鳥E203

時序約束問題的解決辦法

關于綜合保持時間約束不滿足的問題

如何判斷電能質量在線監測裝置時鐘模塊需要進行手動校準?

光纖線需不需要套管

使用stm32u575rg通過spi讀取外置adc的數據,如何設置才能讓spi不需要中斷重啟持續讀取數據?

FPGA時序約束之設置時鐘組

進入IP Core的時鐘,都不需要再手動添加約束嗎

進入IP Core的時鐘,都不需要再手動添加約束嗎

評論