先給大家簡(jiǎn)單快速地介紹一下 Vivado 集成設(shè)計(jì)環(huán)境,即 IDE。當(dāng)打開 Vivado 工程后,會(huì)有一個(gè)工程概要,向您介紹工程的設(shè)置、警告和錯(cuò)誤信息以及工程的一般狀態(tài)。

2012-04-25 09:00:43 7233

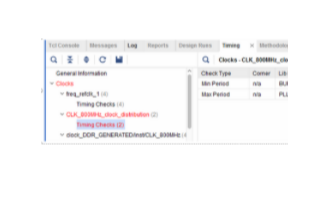

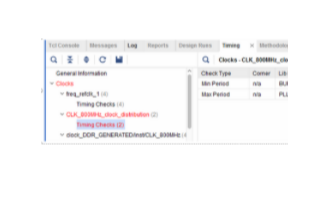

7233 路徑分析問題作一介紹: 1、時(shí)鐘網(wǎng)絡(luò)分析 時(shí)鐘網(wǎng)絡(luò)反映了時(shí)鐘從時(shí)鐘引腳進(jìn)入FPGA后在FPGA內(nèi)部的傳播路徑。 報(bào)告時(shí)鐘網(wǎng)絡(luò)命令可以從以下位置運(yùn)行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 10164

10164 Vivado Simulator基本操作 Vivado Simulator是一款硬件描述語言事件驅(qū)動(dòng)的仿真器,支持功能仿真和時(shí)序仿真,支持VHDL、Verilog、SystemVerilog和混合

2020-12-31 10:02:10 10354

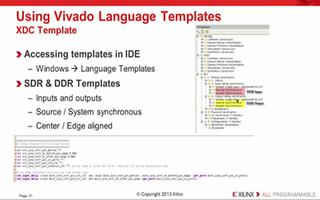

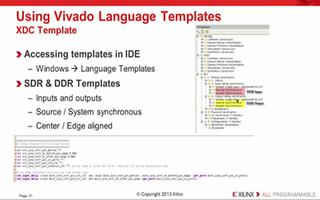

10354 時(shí)序約束的目的就是告訴工具當(dāng)前的時(shí)序狀態(tài),以讓工具盡量?jī)?yōu)化時(shí)序并給出詳細(xì)的分析報(bào)告。一般在行為仿真后、綜合前即創(chuàng)建基本的時(shí)序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進(jìn)行最基本時(shí)序約束相關(guān)腳本。

2022-03-11 14:39:10 11063

11063 在Vitis完成這個(gè)過程的底層,實(shí)際調(diào)用的是Vivado。Vitis會(huì)指定默認(rèn)的Vivado策略來執(zhí)行綜合和實(shí)現(xiàn)的步驟。當(dāng)默認(rèn)的Vivado策略無法達(dá)到預(yù)期的時(shí)序要求時(shí),我們需要在Vivado中分析

2022-08-02 08:03:38 1821

1821

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要?jiǎng)?chuàng)建xdc文件設(shè)置時(shí)序約束。時(shí)序約束文件可以直接創(chuàng)建或添加已存在的約束文件,創(chuàng)建約束文件有兩種方式:Constraints Wizard和Edit Timing Constraints,在綜合后或?qū)崿F(xiàn)后都可以進(jìn)行創(chuàng)建。

2025-03-24 09:44:17 4561

4561

學(xué)習(xí)。個(gè)人學(xué)習(xí)的時(shí)候可以根據(jù)實(shí)際情況選擇最高至Vivado2019.1。(從Vivado2019.2開始,PS開發(fā)使用Vitis,沒有SDK了)第1章 FPGA技術(shù)分析 / 11.1 FPGA內(nèi)部結(jié)構(gòu)

2020-10-21 18:24:48

Vivado運(yùn)行Report Timing Summary時(shí),只顯示各個(gè)子項(xiàng)目最差的十條路徑,很可能并不包含你最關(guān)心的路近,這個(gè)時(shí)候顯示指定路徑的時(shí)序報(bào)告就顯得很重要了,下面就簡(jiǎn)單介紹一下

2021-01-15 16:57:55

的。來獲取關(guān)于原始的 ISE 設(shè)計(jì)套件以及 Xilinx 在 Vivado 中對(duì)這些開發(fā)工具做改進(jìn)的理由的討論。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的設(shè)備,但是

2021-01-08 17:07:20

嗨,您能告訴我與vivado時(shí)序分析相關(guān)的用戶指南嗎?謝謝

2020-03-16 08:14:45

vivado綜合后時(shí)序為例主要是有兩種原因?qū)е拢?1,太多的邏輯級(jí)

2,太高的扇出

分析時(shí)序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

2025-10-30 06:58:47

vivado軟件的安裝教程以及license

2023-12-21 19:50:00

轉(zhuǎn)自:VIVADO時(shí)序分析練習(xí)時(shí)序分析在FPGA設(shè)計(jì)中是分析工程很重要的手段,時(shí)序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習(xí)VIVADO軟件時(shí)序分析的筆記,小編這里

2018-08-22 11:45:54

1、FPGA中的時(shí)序約束--從原理到實(shí)例 基本概念 建立時(shí)間和保持時(shí)間是FPGA時(shí)序約束中兩個(gè)最基本的概念,同樣在芯片電路時(shí)序分析中也存在。 電路中的建立時(shí)間和保持時(shí)間其實(shí)跟生活中的紅綠燈很像

2022-11-15 15:19:27

關(guān)于靜態(tài)分析和時(shí)序約束的文章

2014-07-17 12:12:35

設(shè)計(jì)的驗(yàn)證平臺(tái),以此來提高工作效率。論文介紹了FF-DX地址計(jì)算部件的時(shí)序建模和靜態(tài)時(shí)序分析方法。在靜態(tài)時(shí)序分析之后,將SDF文件中的延時(shí)信息反標(biāo)到邏輯網(wǎng)表中,通過動(dòng)態(tài)時(shí)序驗(yàn)證進(jìn)一步保證設(shè)計(jì)的時(shí)序收斂

2011-12-07 17:40:14

關(guān)于時(shí)序邏輯等效性的RTL設(shè)計(jì)和驗(yàn)證流程介紹。

2021-04-28 06:13:14

今天給大俠帶來FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂,話不多說,上貨。

這里超鏈接一篇之前的STA的文章,僅供各位大俠參考。

FPGA STA(靜態(tài)時(shí)序分析)

什么是靜態(tài)時(shí)序分析?靜態(tài)時(shí)序分析就是

2024-06-17 17:07:28

FPGA時(shí)序分析系統(tǒng)時(shí)序基礎(chǔ)理論對(duì)于系統(tǒng)設(shè)計(jì)工程師來說,時(shí)序問題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫窗口越來越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整

2012-08-11 17:55:55

約束文件(XDC文件),它包含用于時(shí)序分析的“create_clock”和“set_input_jitter”約束。在ISE 14.7和Spartan-3 FPGA中,我可以使用稱為“時(shí)鐘向?qū)А钡腎P來

2019-08-02 09:54:40

本手冊(cè)通過一個(gè)示例工程,講解了使用 TD 和 Vivado 下時(shí)序約束的對(duì)比,詳細(xì)對(duì)比了時(shí)序約束的命令、時(shí)序約束結(jié)果的展示以及部分時(shí)序路徑。

2022-10-27 06:21:47

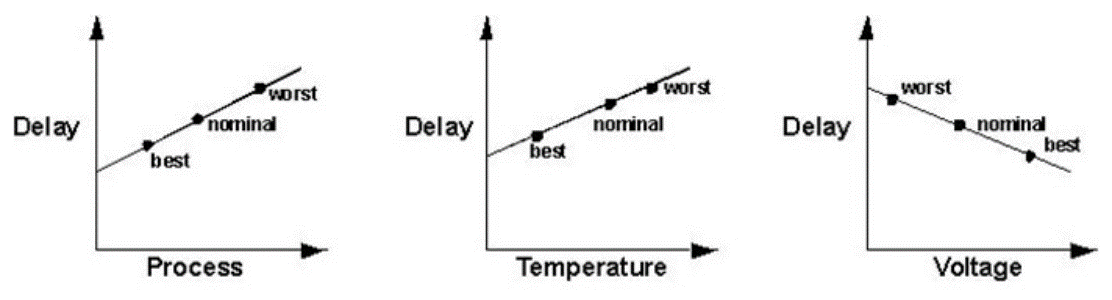

嗨,我們正在嘗試使用Vivado工具鏈?zhǔn)謩?dòng)路由FPGA,并想知道應(yīng)該使用什么工具來手動(dòng)路由Virtex 7 FPGA。還可以在Vivado時(shí)序分析器工具中指定溫度和電壓值來估算設(shè)計(jì)時(shí)序嗎?我們將如

2018-10-25 15:20:50

`基于 FPAGxilinx vivado 仿真模式介紹本文介紹一下xilinx的開發(fā)軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。分別為:1. run

2018-01-24 11:06:12

靜態(tài)時(shí)序分析STA是什么?靜態(tài)時(shí)序分析STA的優(yōu)點(diǎn)以及缺點(diǎn)分別有哪些呢?

2021-11-02 07:51:00

Cadence高速PCB的時(shí)序分析:列位看觀,在上一次的連載中,我們介紹了什么是時(shí)序電路,時(shí)序分析的兩種分類(同步和異步),并講述了一些關(guān)于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 時(shí)序約束與時(shí)序分析 ppt教程

本章概要:時(shí)序約束與時(shí)序分析基礎(chǔ)常用時(shí)序概念QuartusII中的時(shí)序分析報(bào)告

設(shè)置時(shí)序約束全局時(shí)序約束個(gè)別時(shí)

2010-05-17 16:08:02 0

0 在討論時(shí)序邏輯電路的分析與設(shè)計(jì)之前,讓我們先回顧一下在第四章中介紹過的時(shí)序電路結(jié)構(gòu)框圖和一些相關(guān)術(shù)語。時(shí)序電路的結(jié)構(gòu)框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 精確概述Chroma 80611 是一個(gè) 時(shí)序/噪聲分析儀模塊,作為 Chroma POWER PRO III 電源供應(yīng)器自動(dòng)測(cè)試系統(tǒng) 的專用擴(kuò)展卡或子系統(tǒng)。它無法獨(dú)立工作,必須通過 GPIB 總線

2025-11-04 10:31:55

介紹了采用STA (靜態(tài)時(shí)序分析)對(duì)FPGA (現(xiàn)場(chǎng)可編程門陣列)設(shè)計(jì)進(jìn)行時(shí)序驗(yàn)證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時(shí)序約束。針對(duì)時(shí)序不滿足的情況,提出了幾種常用的促進(jìn) 時(shí)序收斂的方

2011-05-27 08:58:50 70

70 討論了靜態(tài)時(shí)序分析算法及其在IC 設(shè)計(jì)中的應(yīng)用。首先,文章討論了靜態(tài)時(shí)序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時(shí)的因素。最后通過一個(gè)完整的IC 設(shè)計(jì)

2011-12-20 11:03:16 95

95 DDR_SDRAM介紹和時(shí)序圖,DDR_SDRAM介紹和時(shí)序圖

2016-02-23 11:58:38 7

7 基于時(shí)序路徑的FPGA時(shí)序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 繼續(xù)介紹vivado+zedboard入門實(shí)例。均為參照教程實(shí)際操作驗(yàn)證成功的實(shí)例,在此拿出來與大家分享。由于教程中步驟已經(jīng)非常清晰,本文只是簡(jiǎn)單介紹實(shí)例以及試驗(yàn)時(shí)的修正記錄,具體的教程及個(gè)人實(shí)現(xiàn)

2017-02-09 05:59:30 1031

1031 此篇文章里,我們將通過使用InTime來檢驗(yàn)Vivado 2017.1和Vivado2016.4之間的性能對(duì)比。 概要:分別進(jìn)行了3個(gè)Vivado 2017.1對(duì)Vivado2016.4的性能測(cè)試

2018-07-04 11:23:00 10852

10852

高速數(shù)字電路互連時(shí)序模型與布線長(zhǎng)度分析 高速電路設(shè)計(jì)領(lǐng)域,關(guān)于布線有一種幾乎是公理的認(rèn)識(shí),即等長(zhǎng)走線,認(rèn)為走線只要等長(zhǎng)就一定滿足時(shí)序需求,就不會(huì)存在時(shí)序問題。本文對(duì)常用高速器件的互連時(shí)序建立模型,并

2017-10-15 10:24:53 1

1 過程必須以滿足XDC中的約束為目標(biāo)來進(jìn)行。那么: 如何驗(yàn)證實(shí)現(xiàn)后的設(shè)計(jì)有沒有滿足時(shí)序要求? 如何在開始布局布線前判斷某些約束有沒有成功設(shè)置? 如何驗(yàn)證約束的優(yōu)先級(jí)? 這些都需要用到Vivado中的靜態(tài)時(shí)序分析工具。

2017-11-17 18:03:55 39395

39395

時(shí)序分析基本概念介紹——時(shí)序庫Lib。用于描述物理單元的時(shí)序和功耗信息的重要庫文件。lib庫是最基本的時(shí)序庫,通常文件很大,分為兩個(gè)部分。

2017-12-15 17:11:43 13739

13739

時(shí)序分析基本概念介紹——Timing Arc

2018-01-02 09:29:04 25530

25530

在實(shí)際工程中,如何利用好這一工具仍值得考究。本文將介紹使用Vivado HLS時(shí)的幾個(gè)誤區(qū)。

2018-01-10 14:33:02 20579

20579

這個(gè)培訓(xùn)將會(huì)深度介紹適于Xililnx 可編程門陣列的HDL代碼風(fēng)格, 產(chǎn)生和驗(yàn)證時(shí)序約束的正確方法, 和如何利用分析和布局規(guī)劃工具分配時(shí)鐘和管腳,產(chǎn)生物理約束以達(dá)到最大設(shè)計(jì)性能. 對(duì)于初次從事FPGA設(shè)計(jì)或使用Vivado軟件的工程師, 我們推薦觀看這個(gè)錄像.

2018-05-23 15:47:00 5021

5021

本文介紹一下xilinx的開發(fā)軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。 分別為: 1. run behavioral simulation-----行為級(jí)仿真,行為

2018-05-29 13:46:52 9080

9080 維持嗎? 1、Vivado基本操作流程 2、時(shí)序基本概念 3、時(shí)序基本約束和流程 4、Baselining時(shí)序約束 5、CDC時(shí)序約束 6、I/O時(shí)序 7、例外時(shí)序約束 8、時(shí)序收斂?jī)?yōu)化技術(shù)

2018-08-06 15:08:02 722

722 今天我們要介紹的時(shí)序分析概念是ETM。全稱extracted timing model。這是在層次化設(shè)計(jì)中必須要使用的一個(gè)時(shí)序模型文件。由block owner產(chǎn)生,在頂層設(shè)計(jì)使用。

2018-09-24 19:30:00 19282

19282

平時(shí)用得可能比較少,是PT產(chǎn)生的一個(gè)spice信息文件,可以用來和HSPICE做correlation。我們平時(shí)使用PT做得是gate level的時(shí)序分析,如果想做transistor level的時(shí)序分析,那可以采用HSPICE做電路仿真。

2018-09-23 16:52:00 7364

7364 UltraFast設(shè)計(jì)方法對(duì)您在Vivado Design Suite中的成功至關(guān)重要。

介紹UltraFast for Vivado并了解可用的材料,以幫助您在整個(gè)設(shè)計(jì)周期中應(yīng)用UltraFast方法

2018-11-20 06:48:00 2980

2980 了解Vivado設(shè)計(jì)套件中的一些廣泛的設(shè)計(jì)分析功能,旨在識(shí)別可能影響性能的設(shè)計(jì)中的問題區(qū)域。

2018-11-27 07:10:00 5457

5457 了解report_design_analysis,這是一個(gè)新的Vivado報(bào)告命令,可以獨(dú)特地了解時(shí)序和復(fù)雜性特征,這些特性對(duì)于分析時(shí)序收斂問題很有價(jià)值。

2018-11-26 07:01:00 4107

4107 今天我們要介紹的時(shí)序分析概念是Combinational logic. 中文名組合邏輯單元。這是邏輯單元的基本組成器件。比如我們常見的and, or, not, nand,nor等門電路。

2019-05-14 17:27:07 6312

6312

時(shí)序分析是以分析時(shí)間序列的發(fā)展過程、方向和趨勢(shì),預(yù)測(cè)將來時(shí)域可能達(dá)到的目標(biāo)的方法。此方法運(yùn)用概率統(tǒng)計(jì)中時(shí)間序列分析原理和技術(shù),利用時(shí)序系統(tǒng)的數(shù)據(jù)相關(guān)性,建立相應(yīng)的數(shù)學(xué)模型,描述系統(tǒng)的時(shí)序狀態(tài),以預(yù)測(cè)未來。

2019-11-15 07:02:00 3430

3430

關(guān)于Vivado Dashboard的功能可閱讀這篇文章(Vivado 2018.3這個(gè)Gadget你用了嗎)Vivado 2019.1的Dashboard功能進(jìn)一步增強(qiáng)。

2019-06-12 14:49:24 9205

9205

此次研討會(huì)為該系列的第一期,旨在深入剖析 Vivado 高速時(shí)序收斂技術(shù)。另外我們還將總結(jié)高速設(shè)計(jì)面臨的挑戰(zhàn),介紹設(shè)計(jì)分析、設(shè)計(jì)向?qū)?b class="flag-6" style="color: red">以及設(shè)計(jì)復(fù)雜性和擁塞的分析方法。

2019-07-31 17:54:28 2682

2682 交互式時(shí)鐘域的交叉分析:該功能支持設(shè)計(jì)人員在設(shè)計(jì)早期階段調(diào)試CDC問題。結(jié)合Vivado設(shè)計(jì)套件的交互式時(shí)序分析和交叉探測(cè)特性,CDC分析功能可提供強(qiáng)大的時(shí)序分析和調(diào)試功能,并加速產(chǎn)品上市進(jìn)程。

2019-08-01 09:14:54 2524

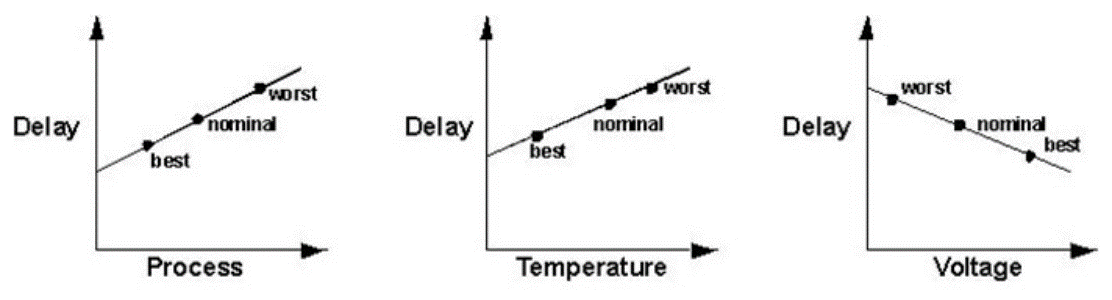

2524 即便是同一種FF,在同一個(gè)芯片上不同操作條件下的延時(shí)都不盡相同,我們稱這種現(xiàn)象為OCV(on-chip variation)。OCV表示的是芯片內(nèi)部的時(shí)序偏差,雖然很細(xì)小,但是也必須嚴(yán)格考慮到時(shí)序分析中去。

2019-07-25 11:22:30 5412

5412

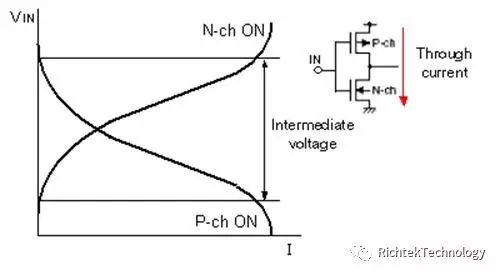

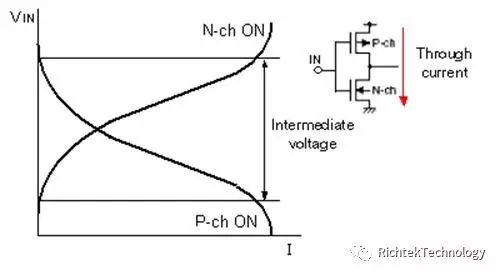

當(dāng)使用多組電源時(shí),每一組的使能信號(hào)、Power Good信號(hào)都需要進(jìn)行處理,這活也實(shí)在是麻煩,所以,高度集成化的系統(tǒng)級(jí)電源管理器件(PMIC)會(huì)把這部分功能也集成起來,以便簡(jiǎn)化設(shè)計(jì)工作,有的芯片甚至可以有多種不同的時(shí)序可供選擇,從而可以擴(kuò)大器件的適用范疇。

2019-10-10 14:48:27 6968

6968

上面我們講的都是xdc文件的方式進(jìn)行時(shí)序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進(jìn)行時(shí)序約束:時(shí)序約束編輯器(Edit Timing Constraints )和時(shí)序約束向?qū)В–onstraints Wizard)。兩者都可以在綜合或?qū)崿F(xiàn)后的Design中打開。

2020-03-08 17:17:00 20443

20443

BY Hemang Divyakant Parikh 有多種類型的時(shí)序違例可歸類為脈沖寬度違例。 - 最大偏差違例(詳見 此處 ) - 最小周期違例(本文詳解之重點(diǎn))。 - 最大周期違例 - 低

2020-11-19 13:48:45 6884

6884

1 I/O延遲約束介紹 要在設(shè)計(jì)中精確建模外部時(shí)序,必須為輸入和輸出端口提供時(shí)序信息。Xilinx Vivado集成設(shè)計(jì)環(huán)境(IDE)僅在FPGA邊界內(nèi)識(shí)別時(shí)序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 6236

6236 靜態(tài)時(shí)序分析是檢查芯片時(shí)序特性的一種方法,可以用來檢查信號(hào)在芯片中的傳播是否符合時(shí)序約束的要求。相比于動(dòng)態(tài)時(shí)序分析,靜態(tài)時(shí)序分析不需要測(cè)試矢量,而是直接對(duì)芯片的時(shí)序進(jìn)行約束,然后通過時(shí)序分析工具給出

2020-11-11 08:00:00 67

67 本文檔的主要內(nèi)容詳細(xì)介紹的是華為FPGA硬件的靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)包括了:靜態(tài)時(shí)序分析一概念與流程,靜態(tài)時(shí)序分析一時(shí)序路徑,靜態(tài)時(shí)序分析一分析工具

2020-12-21 17:10:54 22

22 時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文檔的主要內(nèi)容詳細(xì)介紹的是時(shí)序分析的靜態(tài)分析基礎(chǔ)教程。

2021-01-14 16:04:00 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是時(shí)序分析的Timequest教程免費(fèi)下載。

2021-01-14 16:04:00 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是時(shí)序分析的Timequest教程免費(fèi)下載。

2021-01-14 16:04:00 15

15 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的時(shí)序分析的優(yōu)化策略詳細(xì)說明。

2021-01-14 16:03:59 17

17 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的時(shí)序分析的優(yōu)化策略詳細(xì)說明。

2021-01-14 16:03:59 19

19 在Vivado中分析時(shí)序問題的原因(不在本篇中詳細(xì)討論), 并根據(jù)時(shí)序失敗的原因調(diào)整Vivado各個(gè)步驟的選項(xiàng)。有時(shí)我們也需要調(diào)整Vivad

2021-07-28 10:12:47 2858

2858

VIVADO中時(shí)序報(bào)告中WNS,WHS,TNS,THS含義運(yùn)行“report_timing”或“report_timing_summary”命令后,會(huì)注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 29249

29249

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 關(guān)于紅外通信原理時(shí)序圖介紹,幫助單片機(jī)寫代碼程序

2022-06-26 09:25:11 0

0 組合邏輯和時(shí)序邏輯電路是數(shù)字系統(tǒng)設(shè)計(jì)的奠基石,其中組合電路包括多路復(fù)用器、解復(fù)用器、編碼器、解碼器等,而時(shí)序電路包括鎖存器、觸發(fā)器、計(jì)數(shù)器、寄存器等。 在本文中,小編簡(jiǎn)單介紹關(guān)于時(shí)序電路的類型和特點(diǎn)等相關(guān)內(nèi)容。

2022-09-12 16:44:00 10673

10673

前言 在上篇文章里《時(shí)序分析基本概念(一)——建立時(shí)間》,我們向大家介紹了建立時(shí)間的基本概念和計(jì)算方法。

2022-10-09 11:59:45 5211

5211 關(guān)于電磁干擾的標(biāo)準(zhǔn)、成因以及緩解技術(shù)的介紹

2022-10-28 12:00:16 0

0 【時(shí)序分析的原理】章節(jié)中,我們介紹了很多原理性的東西,而在本章節(jié),我們將為大家介紹在解決具體問題時(shí)該如何向時(shí)序分析工具表述清楚我們的意圖,從而啟動(dòng)其強(qiáng)大的邏輯錐求解功能來得出我們所關(guān)心的時(shí)序分析報(bào)告。

2022-12-28 15:18:38 5209

5209 系統(tǒng)性的掌握技術(shù)開發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。本次帶來Vivado系列,Vivado開發(fā)軟件開發(fā)設(shè)計(jì)流程。話不多說,上貨。

2023-02-21 09:16:44 5063

5063 前面幾篇文章已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束基礎(chǔ)知識(shí)以及常用的時(shí)序約束命令,相信大家已經(jīng)基本掌握了時(shí)序約束的方法。

2023-06-23 17:44:00 4086

4086

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會(huì)提供時(shí)序報(bào)告,以方便開發(fā)者判斷自己的工程時(shí)序是否滿足時(shí)序要求。

2023-06-23 17:44:00 2986

2986

今天介紹一下,如何在Vivado中添加時(shí)序約束,Vivado添加約束的方法有3種:xdc文件、時(shí)序約束向?qū)В–onstraints Wizard)、時(shí)序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 6081

6081

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會(huì)提供時(shí)序報(bào)告,以方便開發(fā)者判斷自己的工程時(shí)序是否滿足時(shí)序要求。

2023-06-26 15:29:05 2343

2343

向量和動(dòng)態(tài)仿真 。本文將介紹靜態(tài)時(shí)序分析的基本概念和方法,包括時(shí)序約束,時(shí)序路徑,時(shí)序裕量,setup檢查和hold檢查等。 時(shí)序路徑 同步電路設(shè)計(jì)中,時(shí)序是一個(gè)主要的考慮因素,它影響了電路的性能和功能。為了驗(yàn)證電路是否能在最

2023-06-28 09:38:57 2402

2402

今天要介紹的時(shí)序分析基本概念是lookup table。中文全稱時(shí)序查找表。

2023-07-03 14:30:34 2617

2617

今天我們要介紹的時(shí)序分析概念是 **min pulse width** ,全稱為最小脈沖寬度檢查。這也是一種非常重要的timing arc check,經(jīng)常用在時(shí)序器件或者memory上面。

2023-07-03 14:54:11 4954

4954

今天我們要介紹的時(shí)序分析概念是clock gate。 clock gate cell是用data signal控制clock信號(hào)的cell,它被頻繁地用在多周期的時(shí)鐘path,可以節(jié)省功耗。

2023-07-03 15:06:03 4536

4536

今天我們要介紹的時(shí)序分析概念是 **AOCV** 。全稱Stage Based Advanced OCV。我們知道,在OCV分析過程中,我們會(huì)給data path,clock path上設(shè)定單一的timing derate值。

2023-07-03 16:29:05 3153

3153

??本文主要介紹了靜態(tài)時(shí)序分析 STA。

2023-07-04 14:40:06 2047

2047

今天要介紹的時(shí)序分析基本概念是Latency, 時(shí)鐘傳播延遲。主要指從Clock源到時(shí)序組件Clock輸入端的延遲時(shí)間。

2023-07-04 15:37:08 4569

4569

今天我們要介紹的時(shí)序分析基本概念是MMMC分析(MCMM)。全稱是multi-mode, multi-corner, 多模式多端角分析模式。這是在先進(jìn)工藝下必須要使用的一種時(shí)序分析模式。

2023-07-04 15:40:13 3999

3999

今天要介紹的時(shí)序分析基本概念是skew,我們稱為偏差。

2023-07-05 10:29:37 5173

5173

今天要介紹的時(shí)序分析基本概念是Slew,信號(hào)轉(zhuǎn)換時(shí)間,也被稱為transition time。

2023-07-05 14:50:53 5365

5365

今天我們要介紹的時(shí)序基本概念是Timing arc,中文名時(shí)序弧。這是timing計(jì)算最基本的組成元素,在昨天的lib庫介紹中,大部分時(shí)序信息都以Timing arc呈現(xiàn)。

2023-07-06 15:00:02 5603

5603

今天我們要介紹的時(shí)序分析概念是Critical Path。全稱是關(guān)鍵路徑。

2023-07-07 11:27:17 2239

2239

今天主要介紹的時(shí)序概念是時(shí)序庫lib,全稱liberty library format(以? lib結(jié)尾),

2023-07-07 17:15:00 4863

4863

今天我們要介紹的時(shí)序分析命令是uncertainty,簡(jiǎn)稱時(shí)鐘不確定性。

2023-07-07 17:23:46 4508

4508

有些時(shí)候在寫完代碼之后呢,Vivado時(shí)序報(bào)紅,Timing一欄有很多時(shí)序問題。

2024-01-05 10:18:36 4035

4035 有時(shí)我們對(duì)時(shí)序約束進(jìn)行了一些調(diào)整,希望能夠快速看到對(duì)應(yīng)的時(shí)序報(bào)告,而又不希望重新布局布線。這時(shí),我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時(shí)序約束。如果調(diào)整

2024-10-24 15:08:40 1602

1602

本文介紹了集成電路設(shè)計(jì)中靜態(tài)時(shí)序分析(Static Timing Analysis,STA)的基本原理、概念和作用,并分析了其優(yōu)勢(shì)和局限性。 ? 靜態(tài)時(shí)序分析(Static Timing

2025-02-19 09:46:35 1484

1484 Vivado中時(shí)序分析工具默認(rèn)會(huì)分析設(shè)計(jì)中所有時(shí)鐘相關(guān)的時(shí)序路徑,除非時(shí)序約束中設(shè)置了時(shí)鐘組或false路徑。使用set_clock_groups命令可以使時(shí)序分析工具不分析時(shí)鐘組中時(shí)鐘的時(shí)序路徑,使用set_false_path約束則會(huì)雙向忽略時(shí)鐘間的時(shí)序路徑

2025-04-23 09:50:28 1079

1079

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論