作者:Mculover666 1.實驗目的 用HDL語言+Vivado創建一個掛載在AXI總線上的自定義IP核 2.實驗步驟 2.1.創建一個新的項目 ? ? 2.2.調用Create

2020-12-21 16:34:14 4566

4566

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。本文將分別介紹FPGA中三種常用復位電路:同步復位、異步復位和異步復位同步釋放,以及相應的Verilog代碼示例。

2023-05-14 14:44:49 3405

3405

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-12-12 09:19:08 3688

3688

Xilinx的FIR IP核屬于收費IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個人學習,現在網絡上流傳的license破解文件在破解Vivado的同時也破解

2025-03-01 14:44:19 2709

2709

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

的基礎上,給出了一種仿真調試方 案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結構分析OpenCores網站提供的OC8051 IP核

2012-08-11 11:41:47

的情況時,總會遇到一些以前未曾接觸過的新內容,這些新內容會讓我們感到陌生和恐懼,不知道該如何下手。

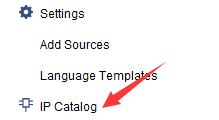

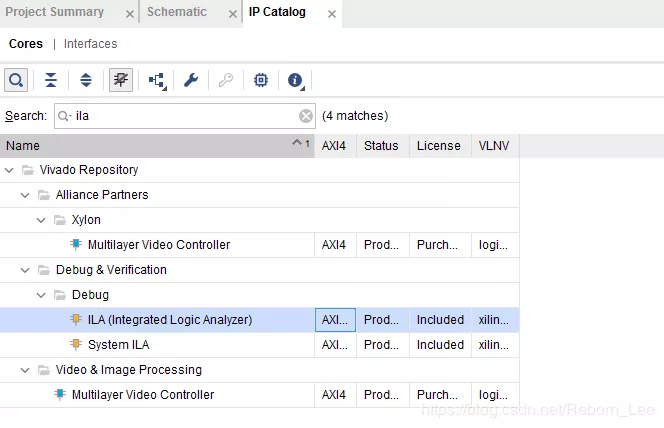

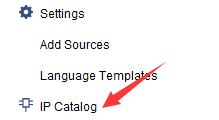

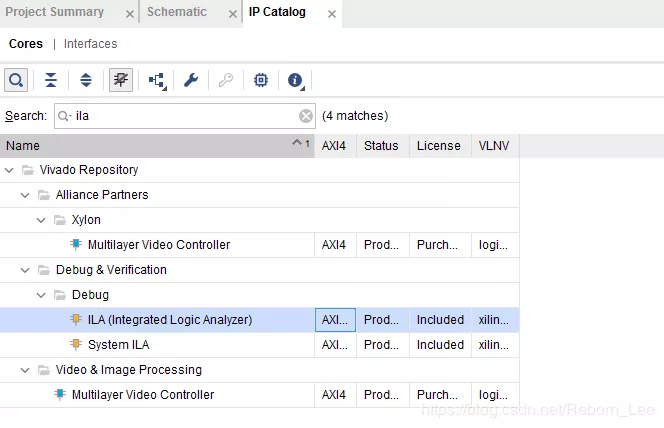

那么今天以xilinx vivado 為例分享學習FPGA 新IP核的正確打開方式。

一、常規

2023-11-17 11:09:22

FPGA的IP軟核使用技巧主要包括以下幾個方面:

理解IP軟核的概念和特性 :

IP軟核是指用硬件描述語言(如VHDL或Verilog)描述的功能塊,但并不涉及具體的電路實現細節。它通常只經過功能

2024-05-27 16:13:24

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個發展趨勢。許多公司推薦使用現成的或經過測試的宏功能模塊、IP核,用來增強

2011-07-06 14:15:52

發生IP核鎖定,一般是Vivado版本不同導致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態報告 Report -》 Report IP Status 2)點擊

2021-01-08 17:12:52

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一個IP核實

2025-10-24 06:25:22

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

剛剛接觸FPGA,通過視頻學習發現使用VIVADO編寫FPGA程序可以通過調用IP核連線和編寫.v文件,實際做過程什么時候該調用IP,怎么知道有該功能的IP,先調用IP連線還是先寫.V文件呢?

2022-08-29 08:44:03

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:39:13

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:40:28

vivado的三速以太網IP核接口太多了,完全不知道應該怎么用,哪位大佬能發我一份設計或者仿真嗎?簡單的就好

2021-04-15 12:58:00

請教一下,vivado怎么把帶ip核的工程進行封裝,保證代碼不可見,可以通過端口調用。我嘗試了以下方法,ippackage,如果要在另一個程序里調用,也要提供源代碼;另一個方法是將網表文件edf文件與端口聲明結合,這種方法只能實現不帶ip核的封裝

2017-07-14 09:18:30

vivado三種常用IP核的調用當前使用版本為vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點

2021-07-29 06:07:16

常用的FBAR模型有哪三種?

2021-03-11 06:16:18

做TCP通訊的時候,有時候需要知道自己的IP雖然知道自己電腦ip可以不用這么麻煩,但是有時候就想用自己所學來獲得自己所需,職業病 咳咳這里給出得到本地IP的三種方法。源程序,在附件里。

2012-11-27 17:17:54

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

用vivado2019.2建立工程,工程中調用cordic IP核進行atan求解,功能仿真時正常且滿足要求;綜合時正常;實現時報錯提示多重驅動。

如果經cordic計算后的輸出值不用于后續的操作

2023-06-06 17:17:37

方式;固核則通常介于上面兩者之間,它已經通過功能驗證、時序分析等過程,設計人員可以以邏輯門級網表的形式獲取。FPGA的開發方式分為三種,分別是:原理圖、Verilog HDL以及IP核。其中原理圖方式

2016-12-22 23:37:00

為什么vivado2016調用MIG ip核會收到嚴重警告呢?這個critical warning會有影響嗎,要怎么解決呢?

2021-10-18 09:41:21

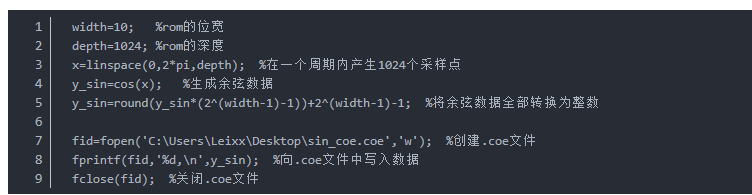

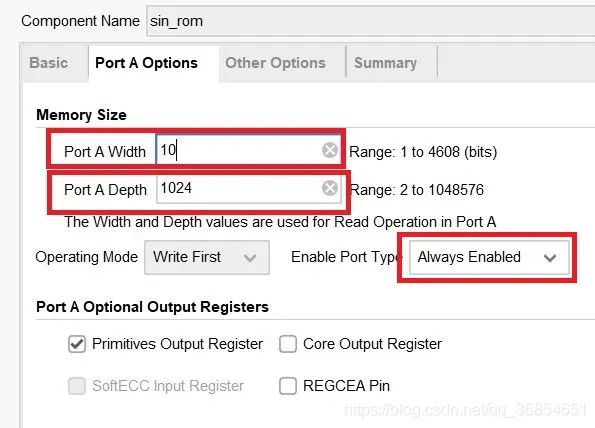

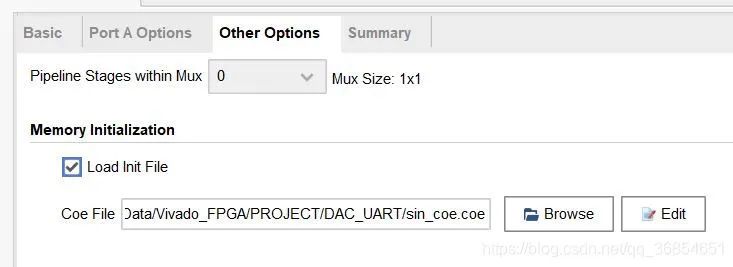

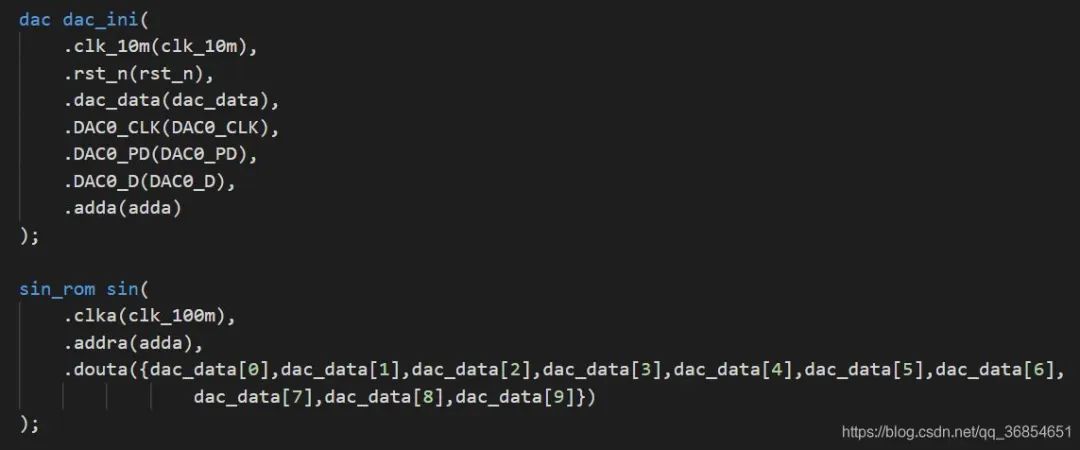

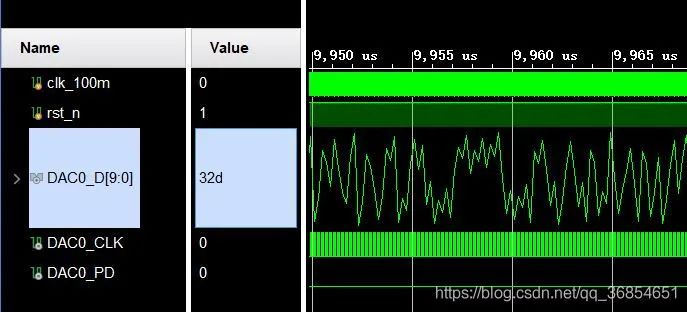

本例程主要使用Vivado 調用ROM IP核,用含有正弦曲線的.coe文件初始化ROM,最終通過仿真實現波形的顯示 一、首先建立工程 二、選擇芯片的型號 我

2021-01-08 17:16:43

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規模的設計應用,適宜的IP核對開發能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調用這些模塊

2024-04-29 21:01:16

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

單片機系統中最常用的三種通信協議是什么?

2022-02-17 06:03:46

%91/vivado2016-%E8%B0%83%E7%94%A8MIG-ip%E6%A0%B8%E4%B8%A5%E9%87%8D%E8%AD%A6%E5%91%8A-Project-1-19/m-p/884989鏈接不管用的話就按照下圖自己找吧。回復: vivado2016 調用MIG ip核

2021-07-28 07:16:27

飛舞,這里就不贅述了,以免有湊字數的嫌疑。下面我們就Matlab和FPGA兩個工具雙管齊下,比對Vivado的FFT IP核生成的數據。2 Matlab產生測試數據,繪制cos時域和頻域波形

2019-08-10 14:30:03

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

的經驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現在有一些經驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

`玩轉Zynq連載21——Vivado中IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https://pan.baidu.com

2019-09-04 10:06:45

Vivado的FFT IP核生成的數據。 2 Matlab產生測試數據,繪制cos時域和頻域波形使用projectzstar_ex67matlab文件夾下的Matlab源碼fft_1line.m,運行產生1組

2020-01-07 09:33:53

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-16 11:42:55

IR900NAT配置常用的三種情景

2024-07-26 07:02:10

三種不同的“防 Ping”技巧

淺析三種不同的“防 Ping”方法

眾所周知,Ping命令是一個非常有用的網絡命令,大家常用它

2010-04-14 13:53:00 1287

1287 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 FPGA的IP核設計技術的系列資料,大家可以收集看下,這些都是我看過過濾后留下的,感覺不錯,希望對大家有幫助

2015-11-30 17:49:01 6

6 利用FPGA的IP核設計和實現FFT算法

2016-05-24 14:14:47 37

37 引入IP核的三維FPGA結構研

2017-01-07 20:32:20 2

2 本文基于xilinx 的IP核設計,源于音頻下采樣這一需求。 創建vivado工程 1. 首先打開vivado,創建一個新的project(勾選create project subdirectory

2017-02-08 02:25:09 5883

5883

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

有關FPGA——VIVADO15.4開發中IP 的建立

2017-02-28 21:04:35 16

16 在linux系統上實現vivado調用VCS仿真教程 作用:vivado調用VCS仿真可以加快工程的仿真和調試,提高效率。 前期準備:確認安裝vivado軟件和VCS軟件 VCS軟件最好安裝

2018-07-05 03:30:00 12369

12369

中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。 IP內核的三種類型 IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。

2017-11-15 11:19:14 10744

10744 在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立

2017-11-18 04:22:58 6145

6145 中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。 IP內核的三種類型 IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。

2017-11-28 15:49:58 2339

2339 在給別人用自己的工程時可以封裝IP,Vivado用封裝IP的工具,可以得到像xilinx的ip一樣的可以配置參數的IP核,但是用其他工程調用后發現還是能看到源文件,如何將工程源文件加密,暫時沒有找到方法,如果知道還請賜教。

2018-06-26 11:33:00 8932

8932 大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 Xilinx FPGA有三種可以用來做片上存儲(RAM,ROM等等)的資源,第一個就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。

2018-12-16 11:31:21 14210

14210

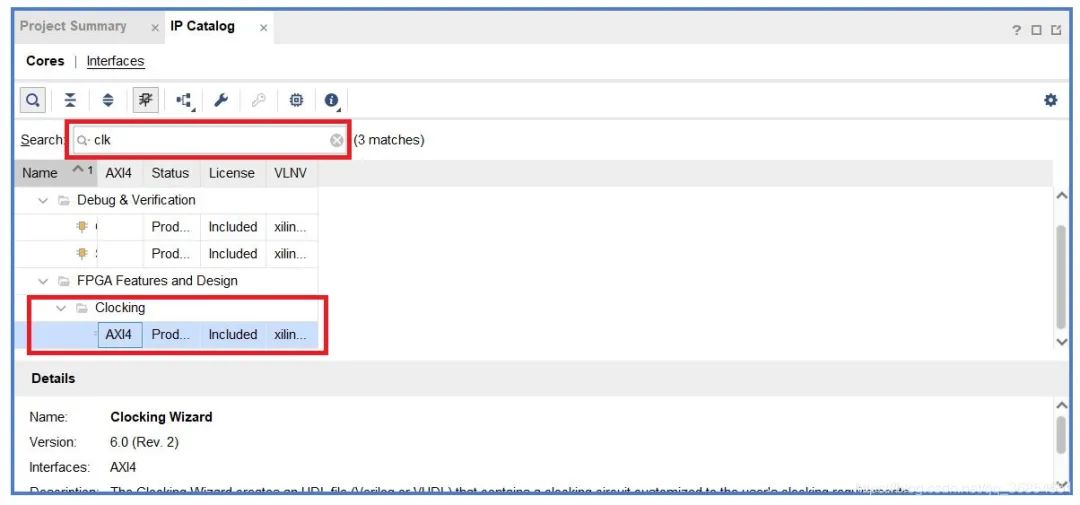

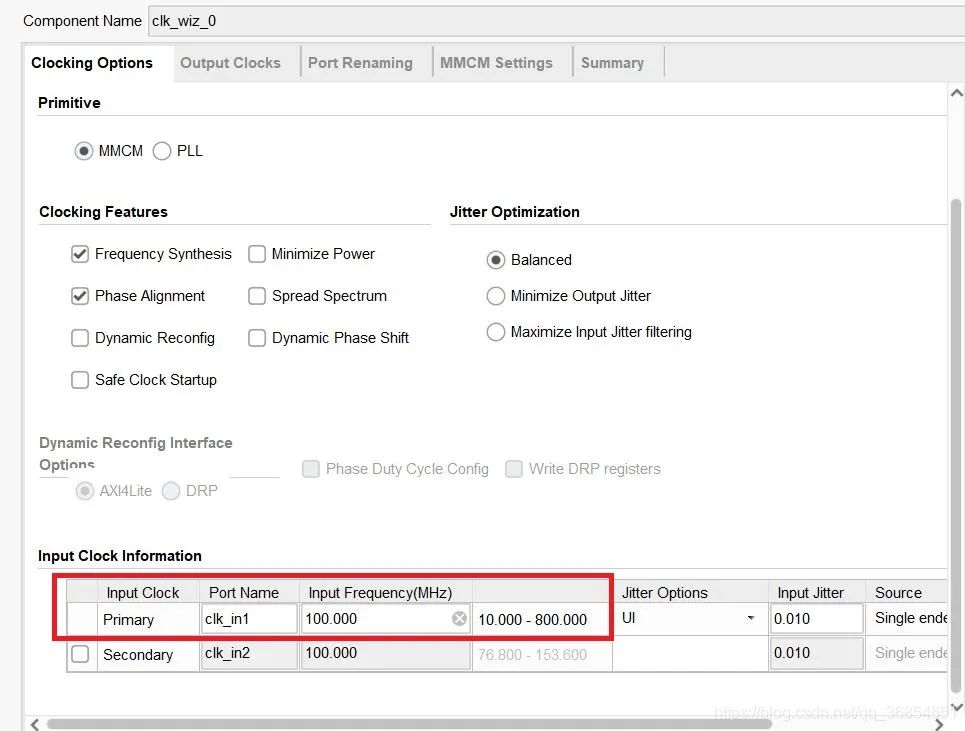

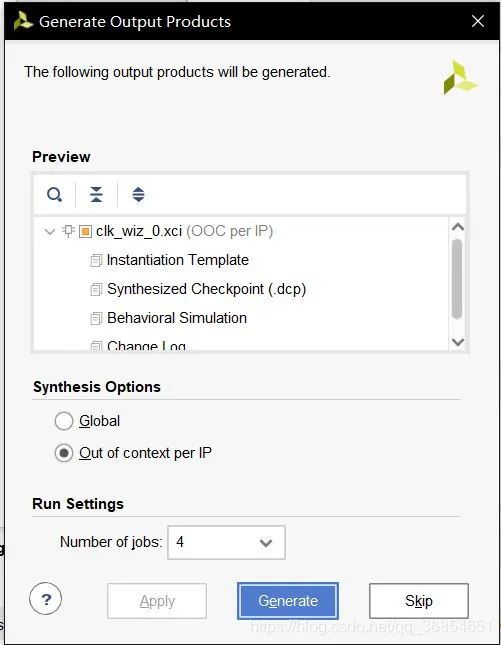

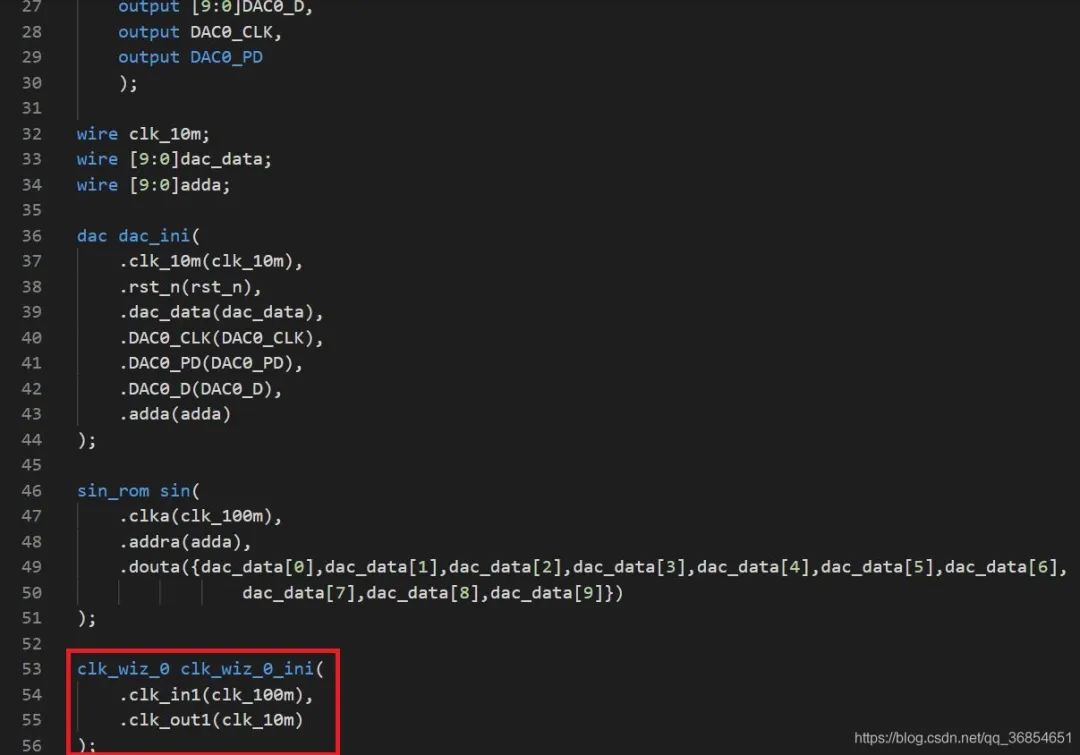

在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,下面就介紹一下在vivado2017.3中進行PL開發時調用IP的方法。

2018-12-22 14:26:38 5200

5200 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,這是同步時序電路的關鍵,這時就需要使用到時鐘向導IP,下面就介紹一下在vivado中進行PL開發時調用IP的方法。

2018-12-22 15:14:38 10894

10894 IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的方式,而這三種IP內核實現方法也各具特色。

2019-12-19 07:07:00 2268

2268

IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的方式,而這三種IP內核實現方法也各具特色。

2019-10-08 07:09:00 1940

1940 IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的方式,而這三種IP內核實現方法也各具特色。

2019-09-26 07:08:00 2545

2545

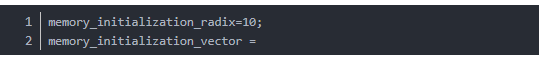

.coe格式的數據文件簡介 在Vivado中,對rom進行初始化的文件是.coe文件.它的格式如下: memory_initialization_radix=10

2020-11-20 15:01:24 7939

7939

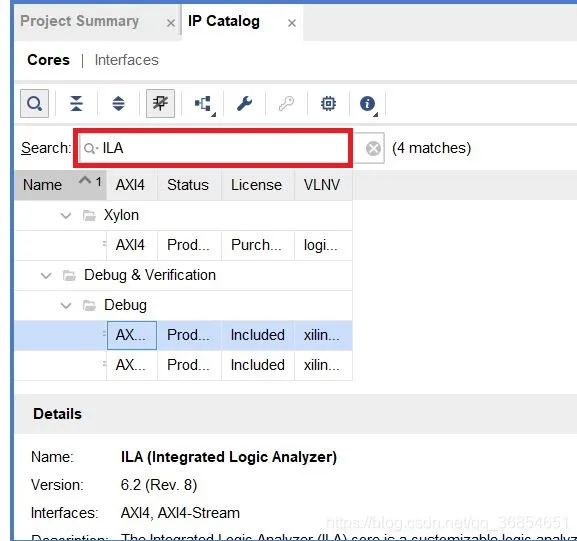

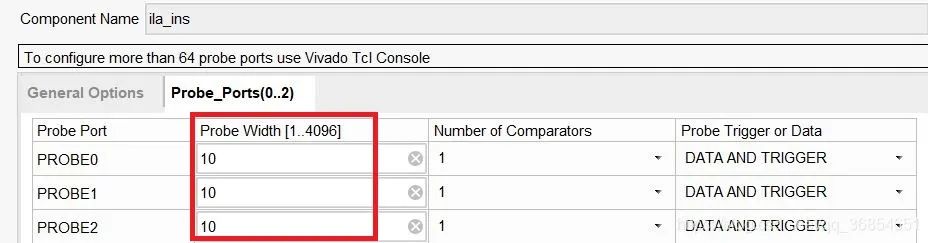

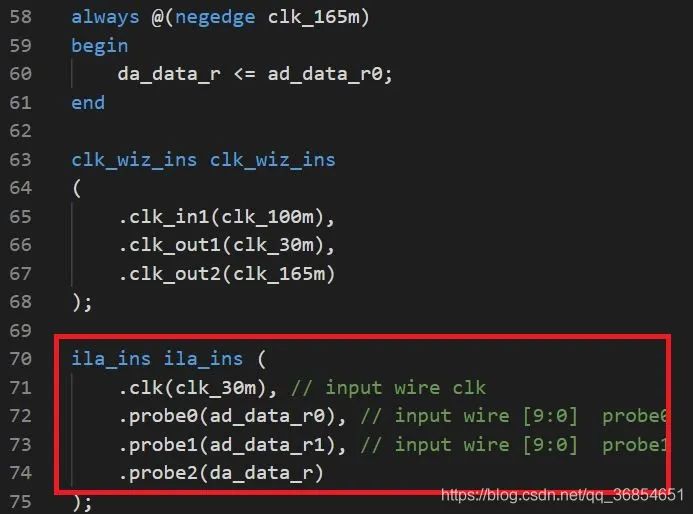

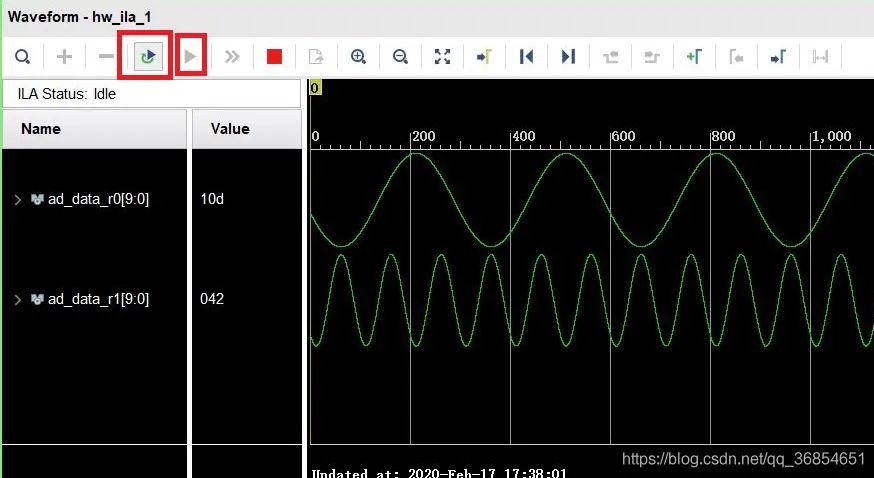

Vivado中提供了多種Debug的操作方式,下面就來總結一下: 1. 代碼中例化ILA IP核 第一種,直接例化ILA IP核: 需要探測多少個信號,信號的位寬是多少,直接選擇即可: 下面界面可以

2020-11-11 17:07:13 11668

11668

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 Vivado2017.2 中BRAM版本為 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5種類型:Single-port RAM

2021-03-10 06:15:56 19

19 些許改進,所以寫這篇文章補充下。 在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。 對于沒有使用SECURE IP核的IP核仿真,只需要在VCS

2021-03-22 10:31:16 5360

5360 本次使用Vivado調用DDS的IP進行仿真,并嘗試多種配置方式的區別,設計單通道信號發生器(固定頻率)、Verilog查表法實現DDS、AM調制解調、DSB調制解調、可編程控制的信號發生器(調頻調相)。

2021-04-27 16:33:06 8131

8131

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。

2021-04-27 15:45:12 25681

25681

Vivado提供了三種封裝IP的方式:(1)將當前工程封裝為IP;(2)將當前工程中的BD(IPI 設計)封裝為IP;(3)將指定的文件目錄封裝為IP。 IP Packager支持的輸入文件HDL

2021-08-10 18:09:29 9155

9155

調用第三方仿真軟件查看波形的過程中存在的一些問題。 1、添加新的觀測信號需要重新仿真 Vivado直接調用Modelsim/QuestaSim進行仿真時,波形文件里默認只會出現仿真最頂層中包含

2021-09-02 10:12:06 10120

10120

本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用

2022-03-16 14:14:19 2713

2713

在FPGA實際的開發中,官方提供的IP并不是適用于所有的情況,需要根據實際修改,或者是在自己設計的IP時,需要再次調用時,我們可以將之前的設計封裝成自定義IP,然后在之后的設計中繼續使用此IP。因此本次詳細介紹使用VIvado來封裝自己的IP,并使用IP創建工程。

2022-04-21 08:58:05 7941

7941 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 4676

4676 最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 4032

4032

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復用的設計模塊或功能片段。它們是預先編寫好的硬件設計代碼,可以在FPGA芯片上實現特定的功能。

2023-07-03 17:13:28 8969

8969 Modelsim是十分常用的外部仿真工具,在Vivado中也可以調用Modelsim進行仿真,下面將介紹如何對vivado進行配置并調用Modelsim進行仿真,在進行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 5396

5396

在 Linux 系統中,經常需要查找 IP 地址以進行網絡配置、故障排除或安全管理。無論是查找本地主機的 IP 地址還是查找其他設備的 IP 地址,本文將介紹三種簡單的方法,幫助你在 Linux 中輕松找到所需的 IP 地址。

2023-08-02 09:53:30 973

973

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

IP(Intellectual Property)是知識產權的意思,半導體行業的IP是“用于ASIC或FPGA中的預先設計好的電路功能模塊”。一些常用的復雜的功能模塊(如FIFO、RAM、FIR

2023-08-22 15:04:43 7796

7796

上一篇介紹了常用的鎖相環IP,這一節將介紹一種較為常用的 存儲類IP核 ——ROM的使用方法。ROM是 只讀存儲器 (Read-Only Memory),顧名思義,我們只能讀出事先存放在固態中的數據

2023-08-22 15:06:38 7616

7616

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 3014

3014

Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

2023-09-17 15:37:31 3220

3220

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 FPGA(現場可編程門陣列)的編程涉及到三種主要的硬件描述語言(HDL):VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。這些語言在FPGA設計和開發過程中扮演著至關重要的角色。

2024-03-15 14:36:01 2412

2412 本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5640

5640

電子發燒友App

電子發燒友App

評論